Modelsim与Quartus联合调用

Posted zstar-_

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了Modelsim与Quartus联合调用相关的知识,希望对你有一定的参考价值。

Quartus II和Modelsim的联合仿真

这里拿正点原子FPGA的教程中的例子:

首先编写流水灯的verilog文件:

module flow_red(

input sys_clk , //系统时钟

input sys_rst_n, //系统复位,低电平有效

output reg [3:0] led //4个LED灯

);

//reg define

reg [23:0] counter;

//*****************************************************

//** main code

//*****************************************************

//计数器对系统时钟计数,计时0.2秒

always @(posedge sys_clk or negedge sys_rst_n) begin

if (!sys_rst_n)

counter <= 24'd0;

else if (counter < 24'd10)

counter <= counter + 1'b1;

else

counter <= 24'd0;

end

//通过移位寄存器控制IO口的高低电平,从而改变LED的显示状态

always @(posedge sys_clk or negedge sys_rst_n) begin

if (!sys_rst_n)

led <= 4'b0001;

else if(counter == 24'd10)

led[3:0] <= {led[2:0],led[3]};

else

led <= led;

end

endmodule

注意:这里为了仿真清晰,counter计数器判断改成了24’d10

编译之后,编写vt文件,这个文件用于设定仿真情况的激励信号和时钟信号

`timescale 1 ns/ 1 ns

module flow_red_vlg_tst();

// constants

// general purpose registers

// test vector input registers

reg sys_clk;

reg sys_rst_n;

// wires

wire [3:0] led;

// assign statements (if any)

flow_red i1 (

// port map - connection between master ports and signals/registers

.led(led),

.sys_clk(sys_clk),

.sys_rst_n(sys_rst_n)

);

initial

begin

sys_clk = 1'b0;

sys_rst_n = 1'b0;

#100 sys_rst_n = 1'b1;

#1000 $stop;

end

always #10 sys_clk = ~sys_clk;

endmodule

注意:教程中sys_clk 取反用的是 负号"-",实际应当用波浪号"~",否则语句不报错,但不生效。

之后,在Assignments->setting里面将vt文件进行绑定。

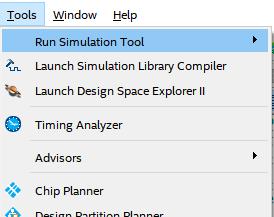

最后,选择Tools->RunSimulation Tool->RTL Simulation,即可成功运行Modelsim

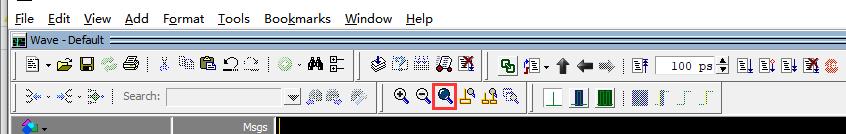

进入Modelsim界面,点击第三个放大镜可以显示全部波形。

点击 Foemat->Toggle Leaf Names ,可以将变量路径名隐藏。

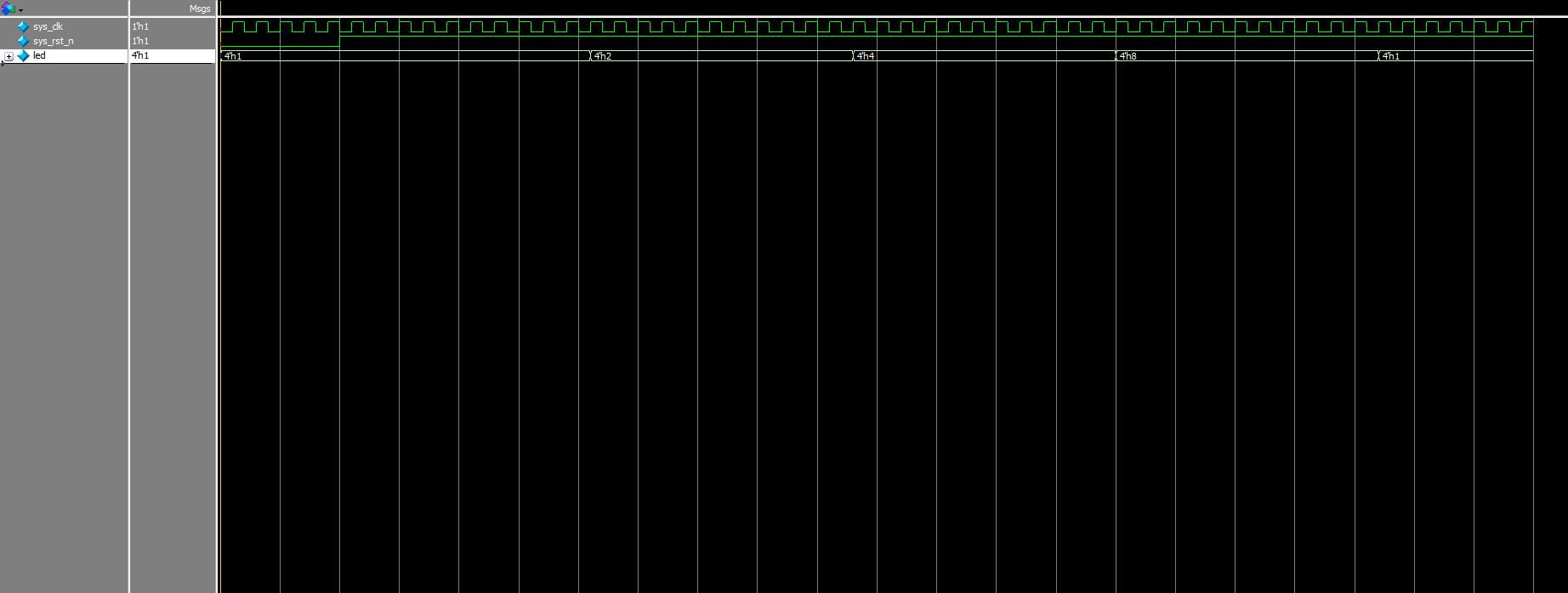

仿真效果如图所示:

以上是关于Modelsim与Quartus联合调用的主要内容,如果未能解决你的问题,请参考以下文章