FPGA实验流水灯实验

Posted zstar-_

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了FPGA实验流水灯实验相关的知识,希望对你有一定的参考价值。

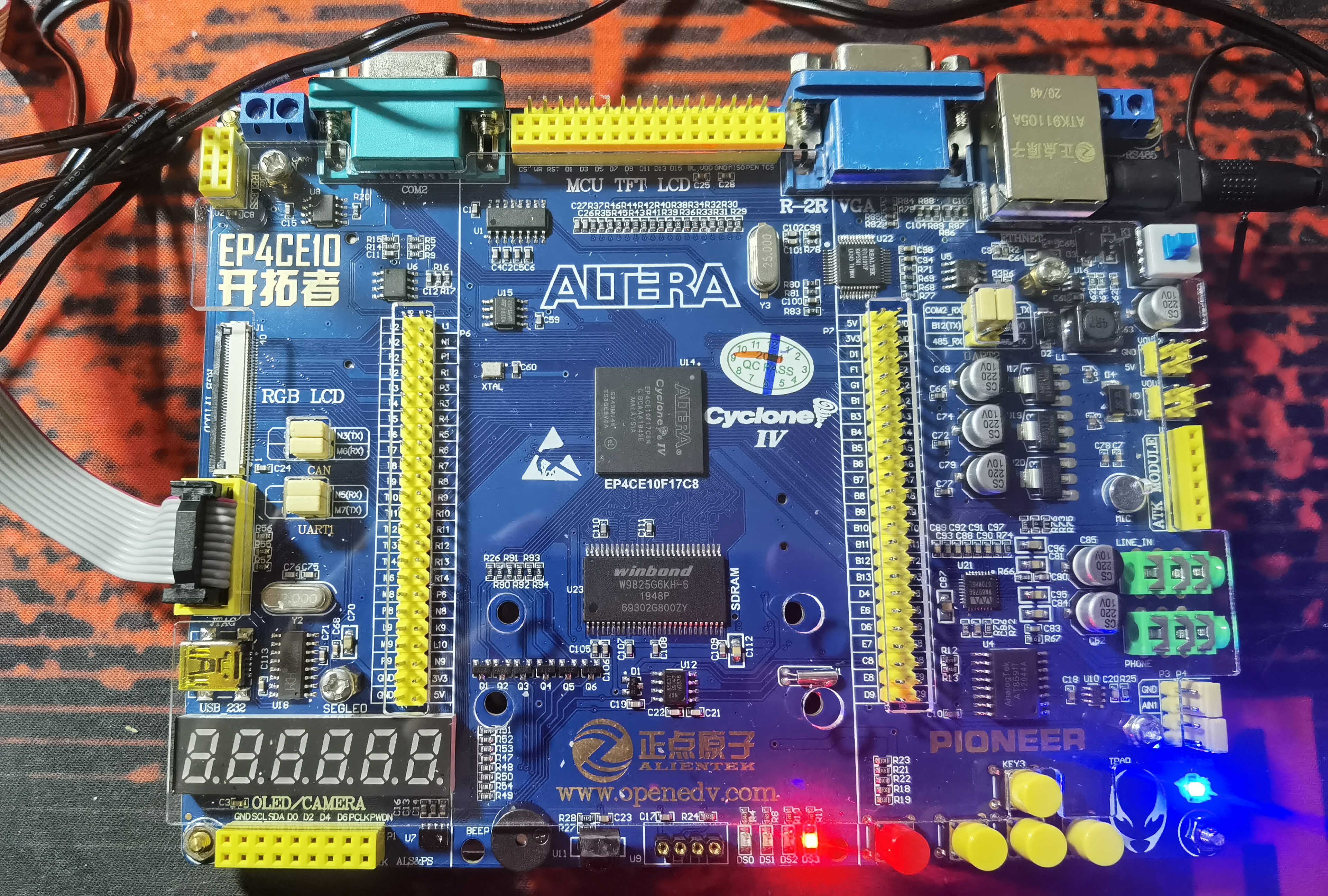

流水灯通常是硬件领域的”Hello World”,本次将使用正点原子的开拓者FPGA开发板来实现简单的流水灯。

Quartus Ⅱ芯片选择设置

Verilog代码

module flow_light(

input sys_clk , //系统时钟

input sys_rst_n, //系统复位,低电平有效

output reg [3:0] led //4个LED灯

);

//reg define

reg [23:0] counter;

//*****************************************************

//** main code

//*****************************************************

//计数器对系统时钟计数,计时0.2秒

always @(posedge sys_clk or negedge sys_rst_n) begin

if (!sys_rst_n)

counter <= 24'd0;

else if (counter < 24'd1000_0000)

counter <= counter + 1'b1;

else

counter <= 24'd0;

end

//通过移位寄存器控制IO口的高低电平,从而改变LED的显示状态

always @(posedge sys_clk or negedge sys_rst_n) begin

if (!sys_rst_n)

led <= 4'b0001;

else if(counter == 24'd1000_0000)

led[3:0] <= {led[2:0],led[3]};

else

led <= led;

end

endmodule

这里注明一下0.2秒实现的思路:

开发板的时钟频率为50Hz,时钟周期是20ns,0.2s/20ns=10^7。

因此,计数器counter的值累加到10^7即为0.2秒。

通过计算器的程序员模式,可以查看10^7次方需要的寄存器位数。

因此,寄存器定义时就设定为24位。

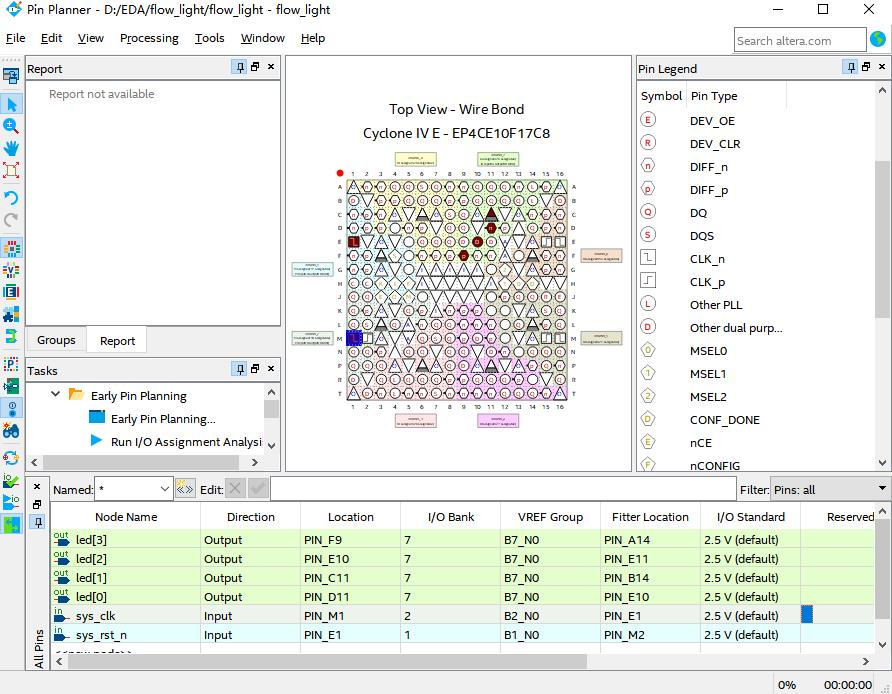

管脚绑定

管脚绑定参照正点原子给的管脚图:

实验效果

以上是关于FPGA实验流水灯实验的主要内容,如果未能解决你的问题,请参考以下文章