嵌入式电路设计(fpga电路设计)

Posted 费晓行

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了嵌入式电路设计(fpga电路设计)相关的知识,希望对你有一定的参考价值。

【 声明:版权,请勿用于商业用途。 联系信箱:feixiaoxing @163.com】

之前本来准备写写dsp电路的,实际上目前用的比较多的dsp还是28335,常用于电机控制。但这类电路和stm32其实都属于mcu,除了执行浮点计算的处理方法不一样,硬件接口部分没什么太大的区别。所以,我们还不如谈谈fpga电路。

大部分公司里面,fpga其实是属于硬件这块的,至少通讯公司里面fpga是和硬件部门分在一起的。如果是芯片设计公司,fpga一般用作芯片原型设计的,也就是流片之前,主要的功能先在fpga上面跑一跑。实际项目中,fpga一般有两个用途,一个是做硬件算法加速,这个常见于zynq,另外一个就是帮助做一些实时控制、或者是信号采集这类对实时性有要求的场合。

虽然听过fpga的人很多,但是熟悉fpga最小电路的人不一定多。我们可以借助于开源硬件平台了解下。原电路图的地址在这,https://oshwhub.com/wangxuan/fpga-ddr-ce-shi-ban。

1、功能说明

从图上看,这就是一块很简单的fpga电路图,两边的排针也没有焊接上去。其实,这就是一块fpga最小系统,只不过还有一块ddr1的芯片,在电路板的背面。

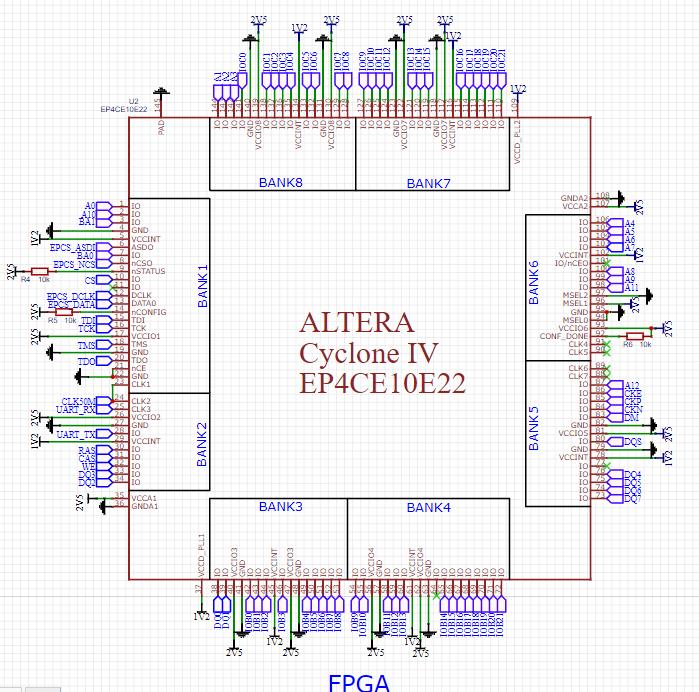

2、fpga芯片

fpga用的是ep4ce10e22,这是一块低端fpga芯片,总共有8个bank。每一个bank可以理解成一个子模块,子模块里面有电源输入、有信号输入输出。从电源接口上说,就是2.5v、1.2v两种。这里,除了pin9、pin14、pin92和一个电阻相连,其他要么电源、要么地、要么就是直接和其他信号直连。

3、晶振

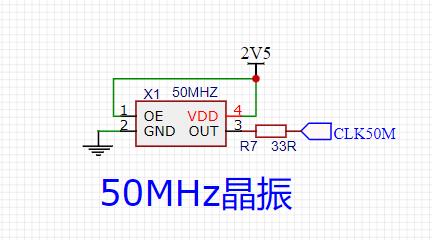

晶振是芯片的灵魂,外挂一个50M的晶振也是少不了的。fpga的晶振普遍没有mcu、soc高,但是这不妨碍它的高性能、低功耗,本质原因还是在于其并发的verilog设计。

4、sof保存的地方

fpga内部是没有办法保存sof文件的,所以上电后,需要从外面的flash加载到fpga,这样fpga才能稳定运行。

5、jtag烧入接口

第一次把bitfile烧入到flash里面,其实需要借助于jtag的帮助,这个和arm soc的jtag其实是一样的。TDI和TMS各有一个上拉电阻,TCK接一个下拉电阻。

6、dcdc电源转换

通常输入电压一般是5v,所以这里就需要用ams1117将其装换成3.3v、2.5v、1.2v。后两个是fpga需要的电压,3.3v是ch340e需要的电压。注意选用不同的ams1117型号即可。

7、ddr部分

上面这三部分,也就是U1.1、U1.2、U1.3指的都是同一个芯片,除了一部分nc悬空、一部分接地,剩下来就是地址、数据、cas、ras、we这些常用接口了。它们都是和fpga直接相连。ddr的电压输入为2.5v。

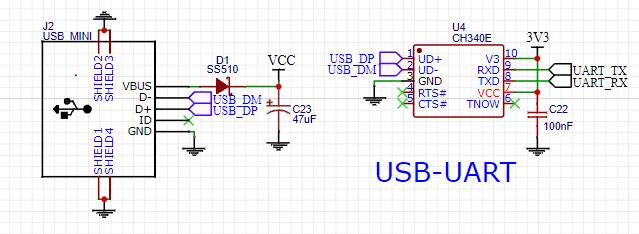

8、usb接口、usb转串口

这部分就是常见套路了,usb mini提供电源,还通过ch340e实现了usb转串口,注意这里ch340e是3.3v输入。 串口直接连接fpga。

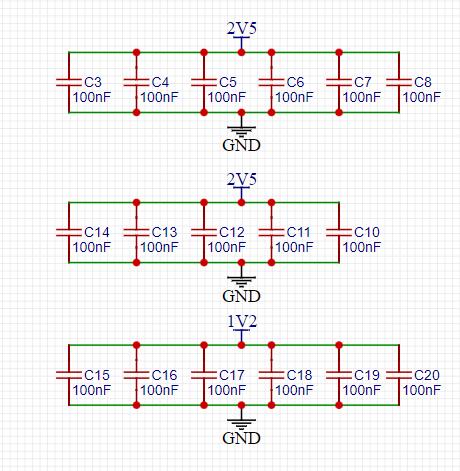

9、电源滤波

常规操作,电源滤波,一般 电容的位置需要和芯片靠近一点。

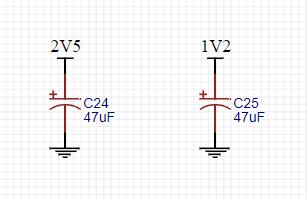

10、两个特殊的滤波电路

和上面第9部分不同,c24、c25是在电压变换后,并联一个电容,而第9部分是在芯片输入的时候, 并联一个电容。前者一般是47uF,大一点,后者一般都是100nf,小一点。

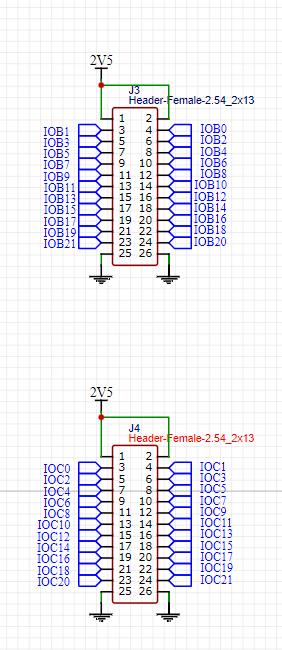

11、引出的接口

和第5部分J1调试接口不同,J3、J4这里引出的接口主要用于扩展fpga的使用,把一些不用的接口通过这种方式引出来。

一个小巧的fpga电路也就上面这部分内容,这还包括了ddr和ch340e这些额外添加的内容。所以,大家其实也不用觉得fpga有多神秘,它就是一个普通的电路,对于那些功能不多,但是对速度和性能要求很高的场景,fpga其实是非常适合的。

以上是关于嵌入式电路设计(fpga电路设计)的主要内容,如果未能解决你的问题,请参考以下文章