Verilog语言基础

Posted zstar-_

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了Verilog语言基础相关的知识,希望对你有一定的参考价值。

Verilog HDL 和 VHDL对比

VHDL: 语法严谨(Basic语言)、 行为与系统级抽象描述能力强、代码冗长、 编程耗时多;

Verilog HDL:语法灵活(C语言)、 版图级与门级描述能力强、代码量小、易上手。

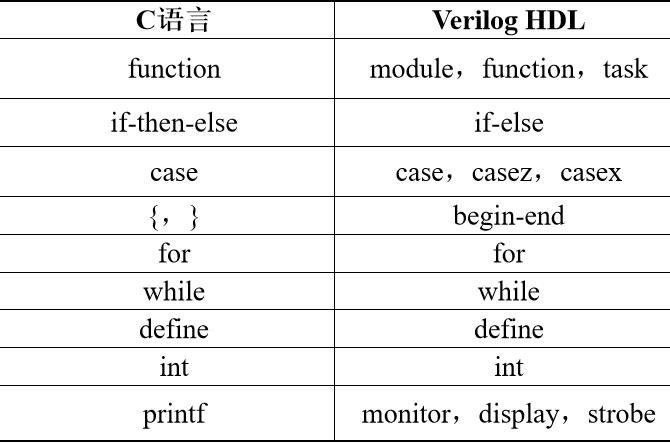

Verilog HDL 和 C语言对比

C是软件语言、 Verilog是硬件描述语言。

Verilog和C语法极其相似,甚至有些是通用的。

C执行时是逐行串行执行,Verilog执行时是并行执行(处理速度非常快)。

C对内存的操作和进行数据的搬移,Verilog会生成所对应的硬件电路。

Verilog HDL语法

模块声明

module 模块名字(端口1,端口2,端口3,…,端口n);

端口定义

input[n-1:0] 端口名1,端口名2,端口名3,…,端口名n; //输入端口

output[n-1:0] 端口名1,端口名2,端口名3,…,端口名n; //输出端口

inout[n-1:0] 端口名1,端口名2,端口名3,…,端口名n; //双向端口

数据类型声明

wire a;//定义一个1位的wire型数据a(1位的wire型数据可以缺省)

reg[7:0] dout; //定义一个8位的reg型数据dout

reg A;//reg型数据A的宽度是1位(1位的reg型数据也不能缺省)

常量

- 整数型 4’b0101,-8’d12,4’ha, 8’b0011_1010

[换算为二进制位宽的总长度][’][数值进制符号][与数值进制符号对应的数值] - 实数型 234.12e2,6e-3

- 字符串型 “Hello world”

实数(浮点数)

- 十进制格式

- 科学计数法

特殊符号

变量

寄存器类型:reg [31:0] delay_cnt

一个抽象的数据存储单元,只能在always和initial中被赋值

线网类型: wire [7:0] data

表示电路间的物理连接,常在assign中被赋值

reg型保持最后一次的赋值,而wire型需要持续驱动

参数类型: parameter DATA_WIDTH = 4b’1000

在module内部常被用于定义状态机的状态、数据位宽和计数器计数个数大小等

运算符

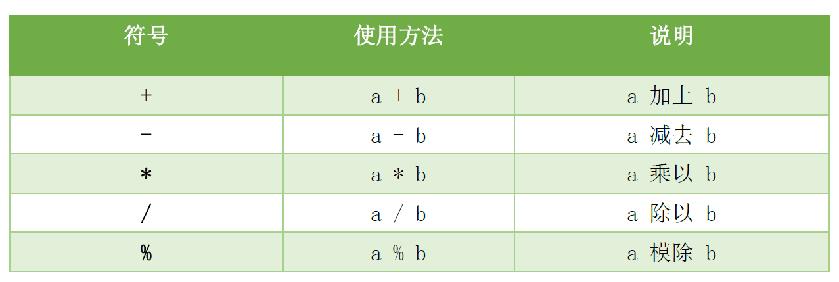

算术运算符

关系运算符

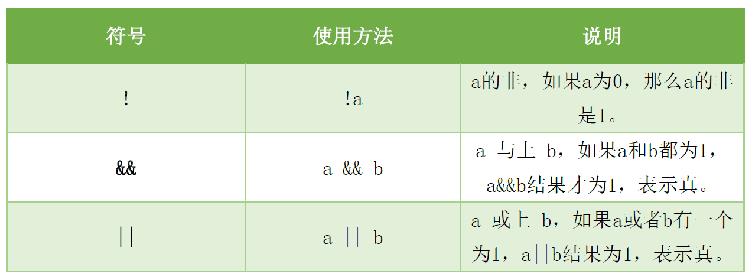

逻辑运算符

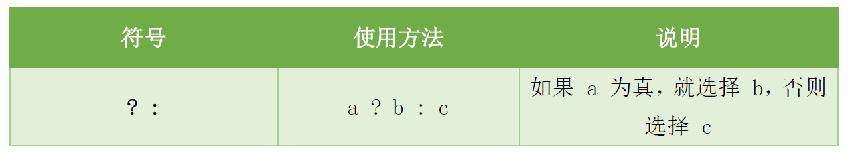

条件运算符

位运算符

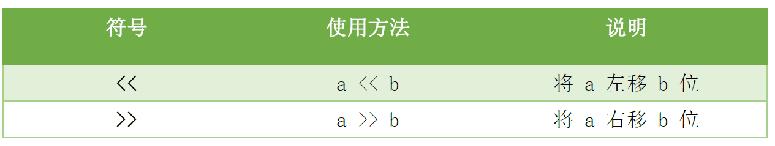

移位运算符

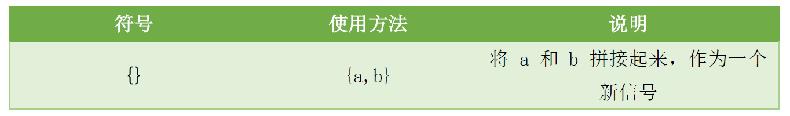

拼接运算符

运算符优先级

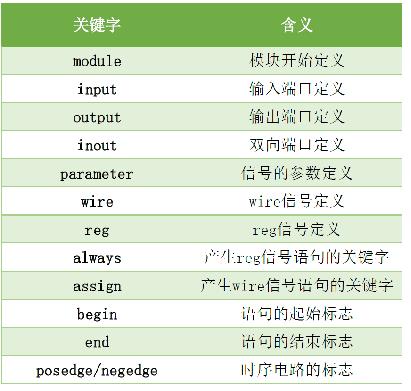

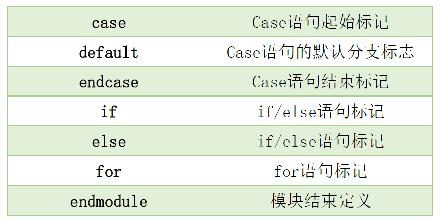

Verilog常用关键字

以上是关于Verilog语言基础的主要内容,如果未能解决你的问题,请参考以下文章