FAPI专题-6:5G FAPI接口 - 中文规范-2- 主要流程

Posted 文火冰糖的硅基工坊

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了FAPI专题-6:5G FAPI接口 - 中文规范-2- 主要流程相关的知识,希望对你有一定的参考价值。

作者主页(文火冰糖的硅基工坊):文火冰糖(王文兵)的博客_文火冰糖的硅基工坊_CSDN博客

本文网址:https://blog.csdn.net/HiWangWenBing/article/details/117602098

目录

2.2 时隙调度流程(P7接口):MAC层调度PHY发送和接收数据

第1章 概述

第2章 主要的流程

FAPI接口有三大流程:

(1)配置管理流程(P5接口):MAC层配置管理PHY层

(2)时隙调度流程(P7接口):MAC层调度PHY发送和接收数据

调度周期可以是125us, 250us,500us, 1ms,取决于子载波间隔。

(3)RF和波束赋型(P19接口):MAC层控制RF

2.1 配置管理流程(P5接口):MAC层配置管理PHY层

2.2.0 概述

(1)配置管理流程分类

- Initialization流程

- Termination流程

- Restart流程

- Reset流程

- Error notification流程

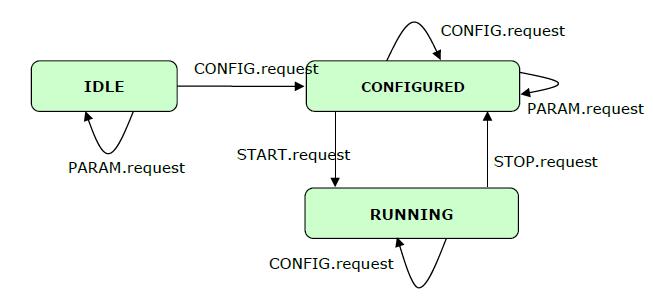

(2)PHY的配置管理状态机

配置管理流程会驱动PHY的状态机的转换。

- IDLE状态:开机后的PHY状态。

- CONFIGURED状态:PHY被配置后的状态。

- RUNNING状态:PHY处于服务状态,MAC层可以对PHY进行时隙调度。

2.1.1 Initialization:初始化流程

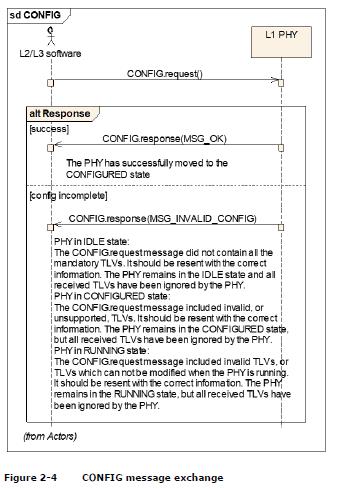

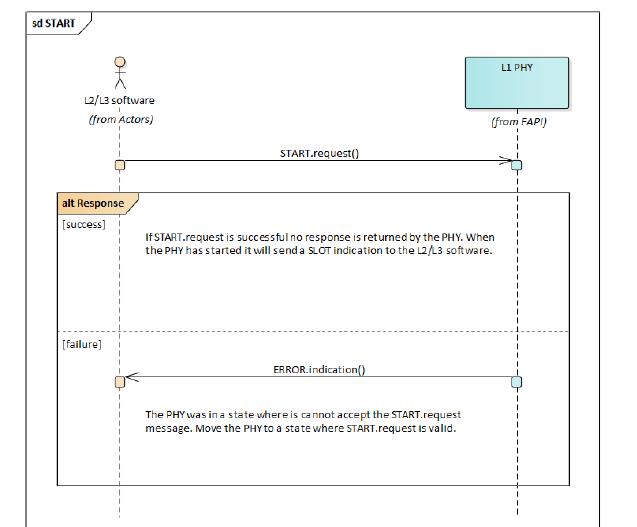

初始化过程是指PHY由IDLE状态 -》configured状态 =》 running状态的状态切换的过程。

初始化是通过PARAM.request, CONFIG.request, START.request这三个消息来完成的。

- PARAM.request:获取PHY的能力参数

- CONFIG.request:对PHY进行配置

- START.request:启动PHY工作

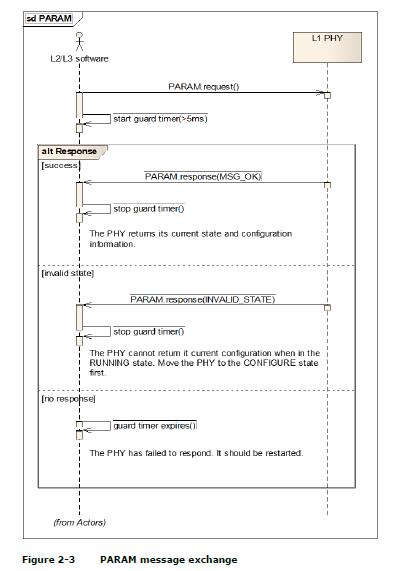

(1)PARAM.request

定时器的作用是防止消息没有响应,通过定时器的超时,处理异常。

(2)CONFIG.Request

(3)START.request

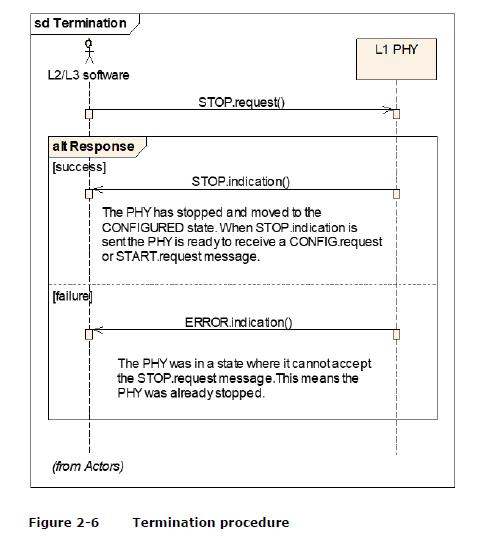

2.1.2 Termination终止流程

终止流程的目的是暂停PHY,使得PHY从RUNNING状态切换到CONFIGURED状态。

终止流程会清除PHY运行时的实时数据,但配置管理数据保持不变。

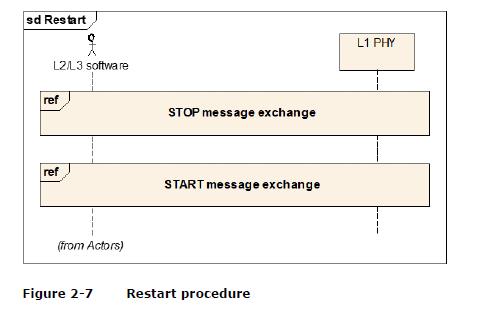

2.1.3 Restart:重启PHY

重启流程会清除PHY运行时的实时数据,但配置管理数据保持不变,然后重启启动PHY.

因此重启是由STOP.request + START.request组成。

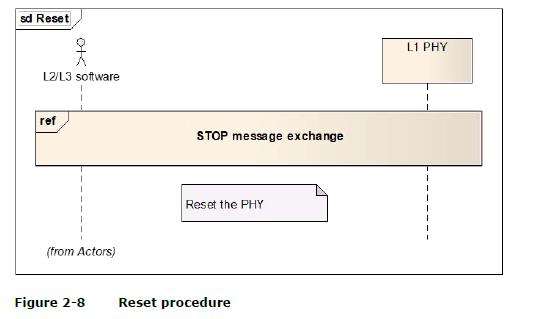

2.1.4 Reset:复位流程

该流程让PHY回到IDLE状态,Reset PHY的过程,该规范并没有确定,取决于不同厂家的实现。

通过通过硬件RESET管脚来完成,也可以通过自定义消息完成。

之所以没有明确通过消息来完成,使用消息有一个致命的缺陷,就是RESET流程通常是在异常的情况才需要触发RESET流程,PHY异常或死机的时候,有时候是不能处理消息的。

当然,FAPI规范要求,在RESET之前,需要先发送STOP消息进行尝试,然后在进行硬件复位。

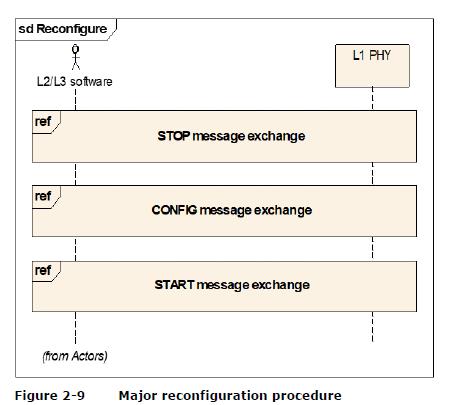

2.1.5 Reconfigure:重新配置流程

有两种方法实现重配

(1)完全重配

完全重配流程通过如下三个消息完成。

完全重配,通常发生在Cell reset时候。

(2)最小化重配

最小化重配,不需要STOP PHY, 直接对PHY进行CONFIG.request。

最小化重配通常发生在RRC Reconfig的时候。

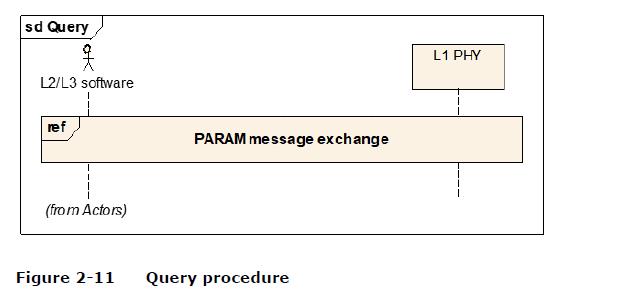

2.1.6 Query:参数或状态查询

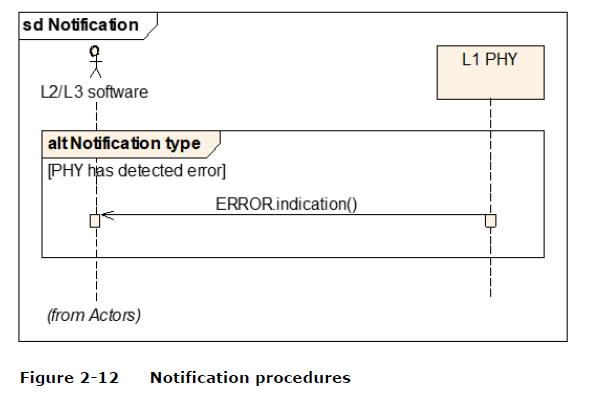

2.1.7 Notification

PHY通过该流程,主动通知L2和L3, 自身内部的状态和异常。

2.2 时隙调度流程(P7接口):MAC层调度PHY发送和接收数据

2.2.0 概述

Slot时隙调度流程是重点,也是理解的难点。该流程起到两个重要的作用:

(1)控制上下行的PHY物理层的帧结构

(2)在L2与PHY物理层之间传送数据

上述两个过程,就是MAC层调度器对PHY物理层的无线资源进行调度的结果。

调度流程有如下的子过程组成:

(1)下行发送

- Transmission of a 125us, 250us, 500us or 1ms SLOT message:调度指示消息,取决于子载波间隔,通过slot indication消息,可以由物理层通知上层,slot的起点,实现TTI (Slot)信号的对齐。

- Synchronization of SFN/SLot between the L2/L3 software and PHY:slot indication实现了TTI信号的频率和相位对齐,而该过程在TTI对齐的基础之上,实现SFN号和SLOT号的同步与对齐。

- Transmission of the BCH transport channel:广播信道数据发送

- Transmission of the PCH transport channel:寻呼信道数据发送

- Transmission of the DL-SCH transport channel:下行共享信道D-SCH用户数据发送

- Transmission of the downlink control information (DCI):下行控制信息指示DCI(基站调度手机), 调度指示和D-SCH用户数据是分开的。现有调度,后来用户数据。

- Transmission of the CSI reference signal:信道状态指示(Channel State Information)

(2)上行接收

- Reception of the RACH transport channel:RACH信道的接收

- Reception of the UL-SCH transport channel:上行共享信道UL-SCH用户数据的接收

- Reception of the uplink control information (UCI):上行控制信息(手机的调度请求),或称为上行调度请求。

- Reception of the sounding reference signal:sounding探测参考信号。

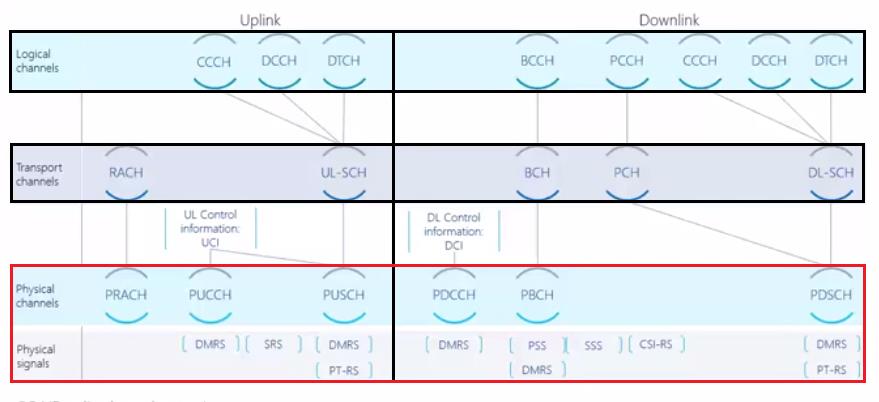

(3)物理层信道

2.2.1 SLOT signal

时隙信号是通过SLOT.indication指示消息来完成的,由PHY发送给MAC层调度器,表明PHY层1个时隙调度的开始。

PHY层通过硬件中断,产生周期性的时隙信号,然后通过SLOT.indication通知MAC层。

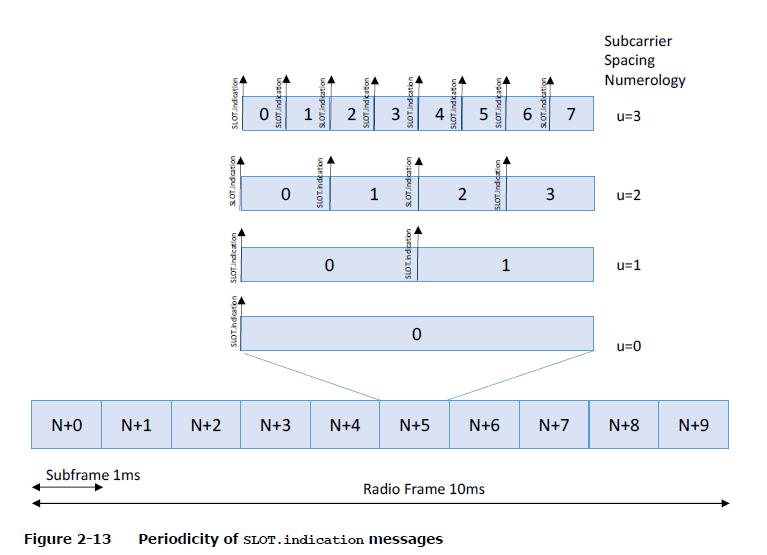

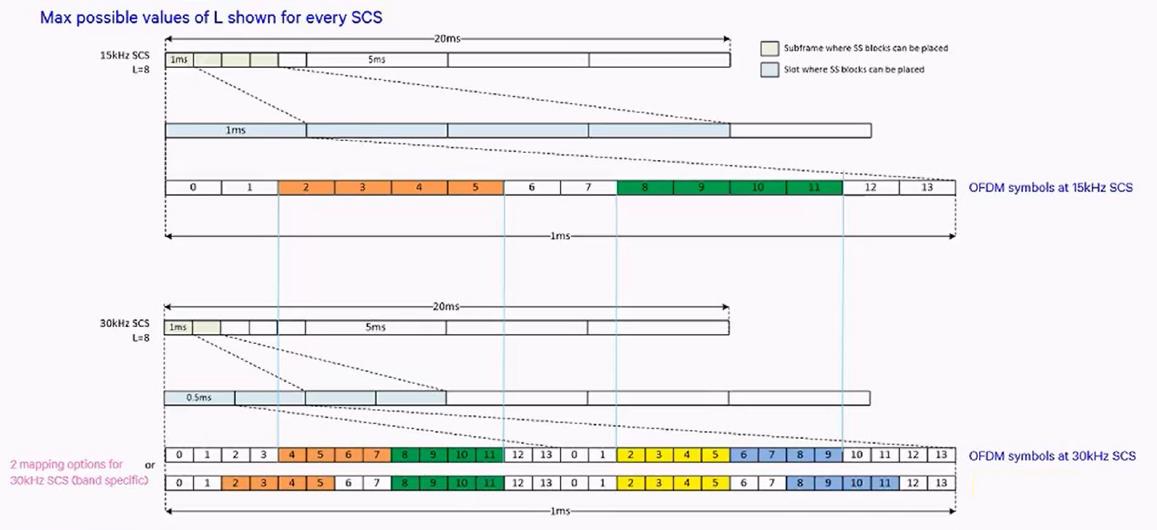

该时隙的周期可以是125us, 250us, 500us or 1ms,其大小取决于子载波间隔的大小。在LTE中,通常1ms调度一次,而5G支持更小的调度周期。

从上图可以看出,Slot时隙调度周期,并不影响10ms帧和1ms的子帧。

时隙周期越小,一个子帧中包含的时隙就越多,对硬件的处理能力要求越高。

- u=0:1ms子帧周期内调度1次,调度周期为1ms,这是LTE的调度周期

- u=1:1ms子帧周期内调度2次,调度周期为0.5ms

- u=2:1ms子帧周期内调度4次,调度周期为0.25ms

- u=3:1ms子帧周期内调度8次,调度周期为0.125ms

2.2.2 SFN/SL Synchronization

(1)什么是SFN/SL同步

在通过PHY层的SLOT.indication指示进行调度前,需要完成10ms帧的系统帧号SFN和SLOT时隙号的同步与对齐。

SFN/SL同步过程就是要维持L2/L3软件实体与L1 PHY实体之间SFN和Slot号的一致。

(2)为什么需要同步流程?

之所以需要特定的流程维持SFN和Slot号的一致性,这是因为它们运行在不同的平台之上,L2&L3软件运行通常运行在ARM CPU + Linux操作系统的平台上,而L1软件运行在DSP之上。这两个系统通常是独立的,只能通过串行总线相连。、

(3)维持SFN/Slot的重要性?

为此这种同步非常重要,因为4G/5G的帧结构是时频结构,频域上是子载波的位置,而时域的位置就是通过10ms帧的系统帧号 + 子帧号 + 时隙号来标识的,不同的系统帧号 + 子帧号 + 时隙号其在无线帧结构中的位置是不相同的,也就是说传输的数据所包含的信息是不相同的。

(4)如何维持两个实体(MAC与PHY)之间SFN/Slot的一致性?

如何维持是关键,这里提供了两种主要的思路:

思路1:集权法,L1 PHY时刻使用L2&L3配置的SFN/Slot的值。

这种方案的优点:是简单,基本是不需要同步机制,L2/L3软件维持SFN/Slot值设定,L1直接使用。

这种方案的缺点:也是明显,它需要L1 PHY和L2&L3软件集成在同一个硬件平台和软件平台上。如单一的SOC芯片。对于完全一体化高度集成的系统是可行的,但对于硬件和软件平台功能分离的系统,这种方案就无法实施了。

思路2:自主法,L1 PHY使用L2&L3软件配置的SFN/Slot的值作为初始值,然后各自自主地维护自身的SFN/SL号,并进行定期的监控,确保双方的SFN/SL是一致的、对齐的。

这种方案优点:能够支持L1 PHY软件与L2&L3软件使用不同的硬件和软件平台,如L1在DSP上,L2&L3在ARM+Linux平台上,这种方案灵活,伸缩性强。

这种方案的缺点:硬件设计复杂,L1 PHY和L2&L3需要维持各种的硬件时钟同步,软件设计复杂,需要同步机制。

这两种方案,在实际系统中,都有自己的使用场合。

既然是同步,就一定有一个主(Master),一个从(Slave),Master负责SFN/SL的初始化以及后期发生不一致时,作为纠错的基准。

是L2&L3软件作为基准,还是L1 PHY作为基准呢?其实,都可以,取决于系统的实现。

因此,谁作为Master就有两种方案:L2&L3软件作为master或L1 PHY作为Master。

(5)称为Master的条件

对能够作为Master的软件实体是有要求的,即自身必须能够同步到外部的标准参考时钟源上,如:

- GPS参考时钟源(都适用)

- 1588参考时钟源(只适用L2&L3作为Master,因为DSP通常不能处理1588协议栈)

- 1PPS参考时钟源(都适用)

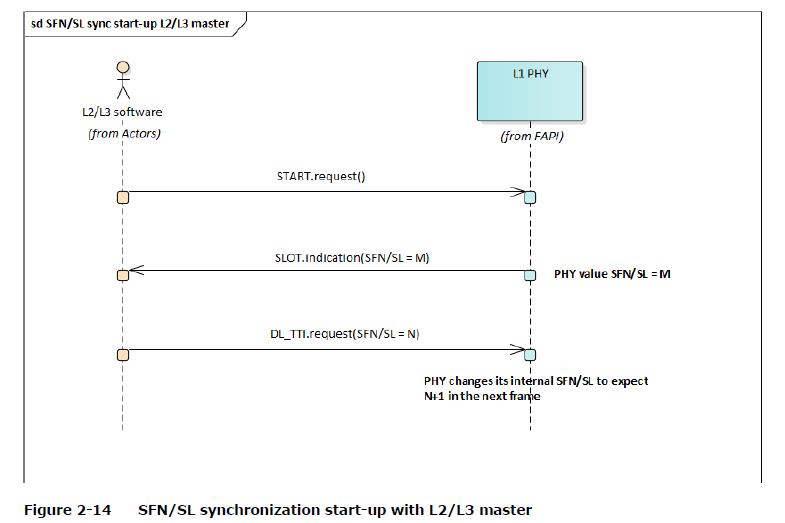

2.2.2.1 L2/L3 software is master

(1)SFN/SL的初始化

- L2&L3软件通过Start.request P5配置信令启动L1 PHY.

- L1 PHY启动后,PHY可以使用任意的SFN/SL值作为默认值M,并通过SLOT.indication = M消息通知L2&L3软件,自己默认的SFN/SL值。

- L2&L3软件,通过DL_TTI.request = N 修正L1 PHY默认的SFN/SL, 得到初始的SFN/SL=N,

至此,完成了SFN/SL的初始化,以及SFN/SL的初始同步。

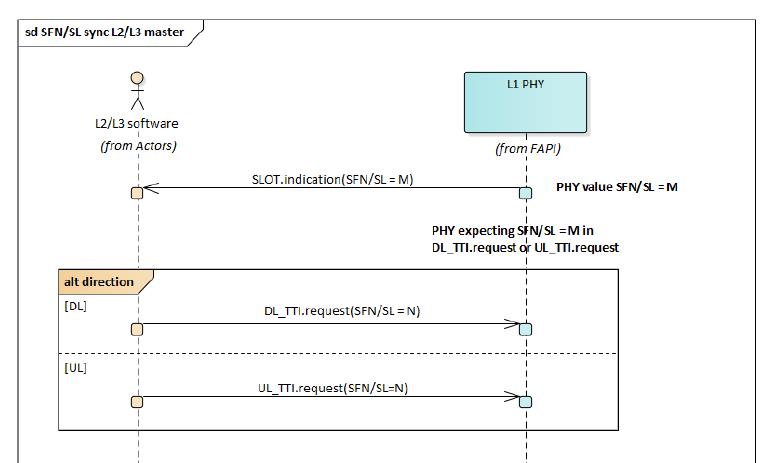

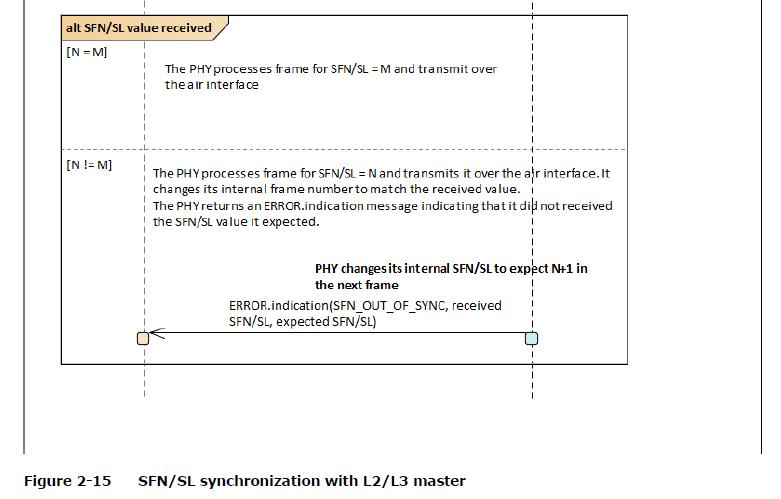

(2)SFN/SL维持与纠错

完成初始化同步后,后续还有可能失步,因此需要一种流程来时刻监控SFN/SL的同步状态 ,并在失步时由L2&L3的软件就PHY进行纠错,重新同步。

由于L2&L3是Master,由L2&L3软件负责对L1的SFN/SL就行纠错。过程如下:

- L1 PHY通过SLOT.indication(SFN/SL=M)向L2&L3软件汇报自身的SFN/SL,

- L2&L3软件发现L1 PHY的SFN/SL=M与自身维持的SFN/SL=N不一致,就启动纠错机制,通过DL_TTI.request(SFN/SL=N) or UL_TTI.request(SFN/SL=N), 要求L1 PHY对自身的SFN/SL就行纠错。

- L1 PHY收到DL_TTI.request(SFN/SL=N) or UL_TTI.request(SFN/SL=N),之后,如果N=M, 这表明是同步的。

- L1 PHY收到DL_TTI.request(SFN/SL=N) or UL_TTI.request(SFN/SL=N),之后,如果N!=M, 这表明是失步的,则L1 PHY对自身的SFN/SL就行纠错,设置为SFN/SL=N.

- L1 PHY同时通过ERROR.indication(失步指示,接受到的SFN/SL, 原先期望的SFN/SL)指示自身内部SFN/SL的失步和纠错情况。

或许有人为思考,L1 PHY已经完成了纠错,为啥还要通过ERROR.indication通知L2&L3软件呢?

主要是因为,L2&L3软件也有可能与它自身的参考时钟源失步,因此通知L2&L3软件自身的纠错情况,以便L2&L3软件根据自身内部的状态,采取合适的行为。

2.2.2.2 L1 PHY is master

如果L1 PHY is master,L1 PHY就是参照的标准,纠偏就发生在L2&L3软件中。

这种方案的难点是L1 PHY如何获得同步时钟。

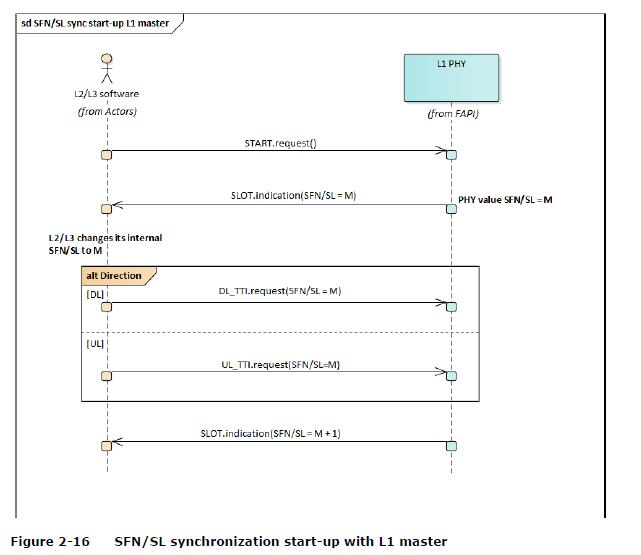

(1)SFN/SL的初始化

- L2&L3软件通过Start.request P5配置信令启动L1 PHY.

- L1 PHY启动后,PHY就不能使用任意的SFN/SL值作为默认值M,M值是PHY与GPS或外部时钟源进行同步后的结果值。

- L1 PHY通过SLOT.indication = M消息通知L2&L3软件,初始SFN/SL值。

- L2&L3软件收到该消息后,设置自身的SFN/SL=M,作为自己的初始SFN/SL值。

- L2&L3软件通过DL_TTI.request = M通知L1 PHY,自身当前的SFN/SL值M, 很显然,与PHY此时是一致的。

- L1 PHY通过SLOT.indication = M+1通知L2&L3软件,期望的下一个SFN/SL值。

至此,完成了SFN/SL的初始化,以及SFN/SL的初始同步。

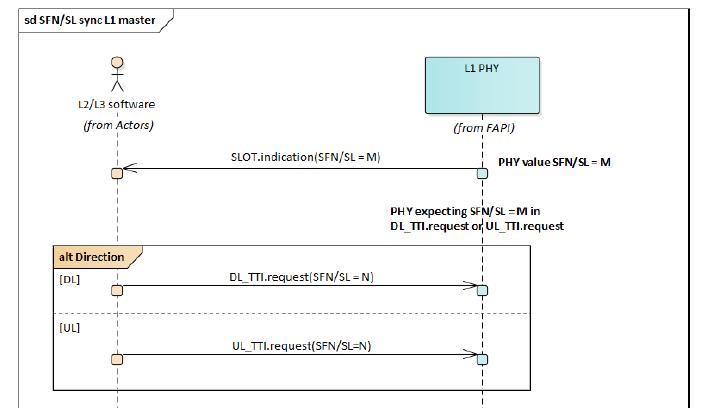

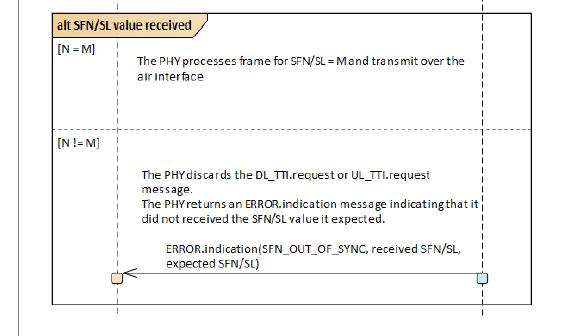

(2)SFN/SL维持与纠错

- L1 PHY通过SLOT.indication(SFN/SL=M)向L2&L3软件汇报自身的SFN/SL

- L2&L3软件发现L1 PHY的SFN/SL=M与自身维持的SFN/SL=N不一致,就启动纠错机制,通过DL_TTI.request(SFN/SL=N) or UL_TTI.request(SFN/SL=N), 要求L1 PHY对自身的SFN/SL就行纠错。

- L1 PHY收到DL_TTI.request(SFN/SL=N) or UL_TTI.request(SFN/SL=N),之后,如果N=M, 这表明是同步的。

- L1 PHY收到DL_TTI.request(SFN/SL=N) or UL_TTI.request(SFN/SL=N),之后,如果N!=M, 这表明是失步的,但L1 PHY是Master,它不会对自身的SFN/SL就行纠错,并丢弃该请求。

- L1 PHY同时通过ERROR.indication(失步指示,接受到的SFN/SL, 原先期望的SFN/SL)指示自身内部SFN/SL的失步和纠错情况。

- L2&L3软件是Slave,因此L2&L3软件会对自身的SFN/SL进行纠错。

在上述过程中, L1 PHY会一直丢弃DL_TTI.request(SFN/SL=N) or UL_TTI.request(SFN/SL=N),知道L2&L3对自身的SFN/SL进行纠错,重重同步。

2.2.3 API message order

FAPI P7接口的消息的发送,是有严格的时序要求的,并非任意时序发送。

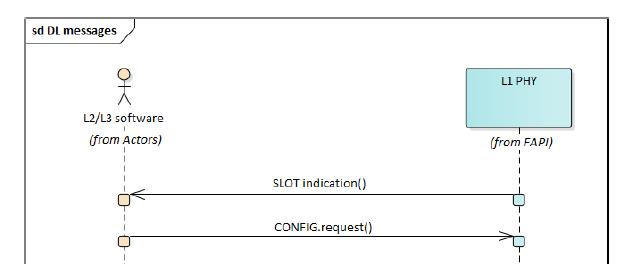

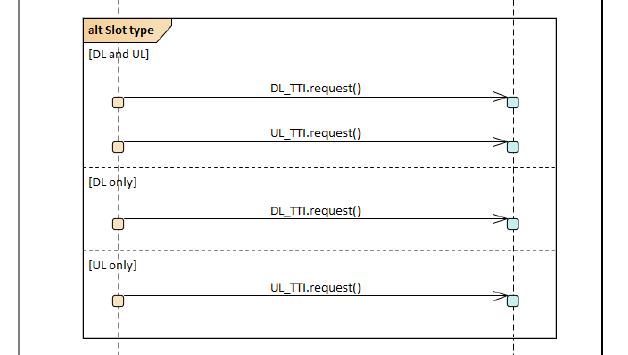

(1)下行消息的时序

- SLOT.indication():时隙开始开始指示,实现时隙信号的同步与对齐

- CONFIG.request():完成PHY的配置或重配

- DL_TTI.request:下行SFN/SL同步与对齐

- UL_TTI.request:上行SFN/SL同步与对齐

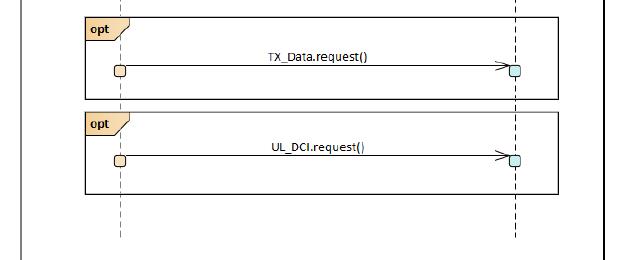

- TX_Data.request:下行数据发送,可选,并不是每个TTI时隙都需要发送,

- UL_DCI.request:对手机的上行调度指示。可选,并不是每个TTI时隙都需要发送。

备注:

DCI: Downlink Control Information,通过PDCCH承载,用于给终端提供指示,如何解调下行DL-SCH信道中数据。

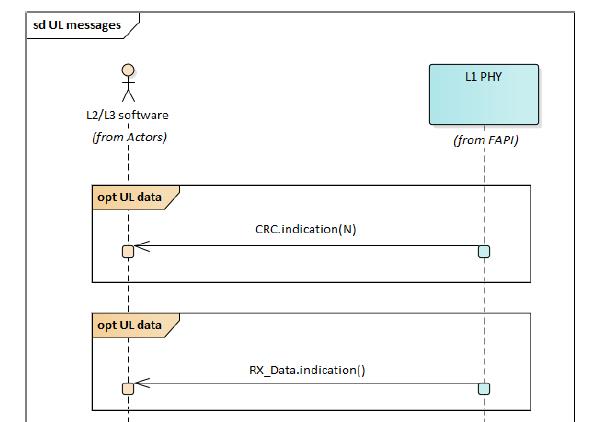

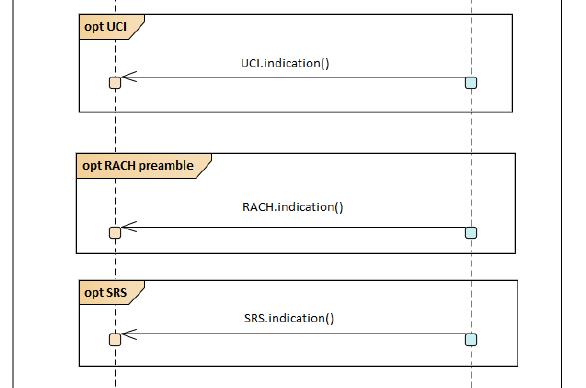

(2)上行消息的时候

- CRC.indication(N):上行数据控制信息。

- Rx_Data.indication():上行数据指示,传输接收到的UL-SCH信道数据。

- UCI.indication:上行控制信道信息指示,通过UL-CCH信道进行传输。

- RACH.indication:随机接入请求,通过PRACH信道进行传输

- SRS.indication:探测参考信号指示,

上述信号都是可选信息,并不是每个时隙都需要。

2.2.4 Downlink(与下行发送相关的子流程)

2.2.4.1 BCH(广播信道)

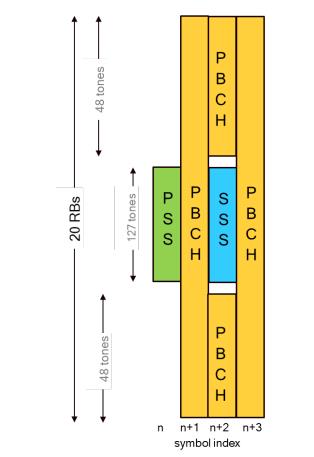

广播信道BCH用于广播发送主信息块MIB, 其周期为80ms,通过物理广播信道PBCH发送。PBCH与主同步信号PSS和辅同步信号SSS信号一起,共同组成同步信号块SSB,如下下图所示:

SSB可以以时间复用的方式在不同的波束中传输。波束扫描中的一组SSB称为SS突发。

SSB的发送周期为5-160ms。

(1)SSB在FR1中的位置(20ms内)

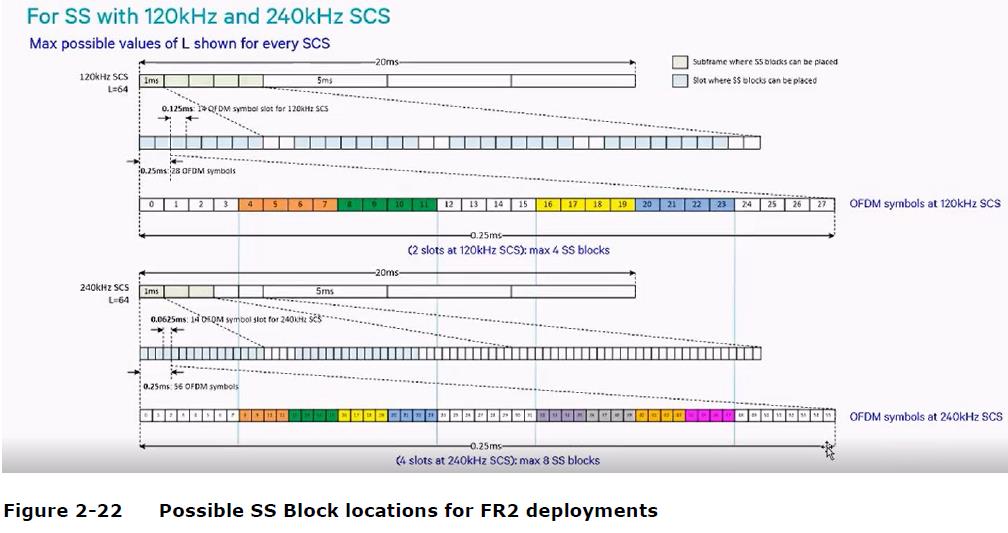

(2)SSB在FR2中的位置(20ms内)

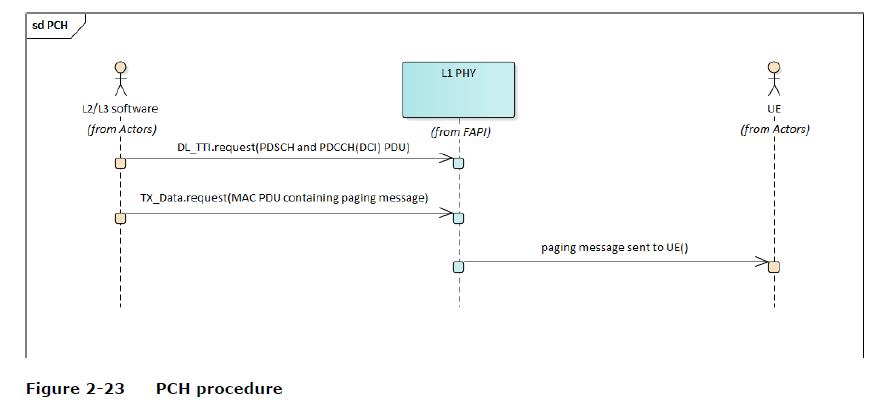

2.2.4.2 PCH(寻呼信道)

通过该消息,可以在基站小区内寻呼某个特定的UE.

- UE会在特定的时间点(paging occasions)周期性的监控,是否有寻呼信息。

- L2&L3软件的职责就是为UE计算特定的时间点(paging occasions)

- L1 PHY的职责是在DL_TTI.request指示下,在特定的paging occasions发送PCH信道的PDU。

- DL_TTI.request来用承载DCI

- PCH PDU是通过DL_TTI.Data下发给L1 PHY的。

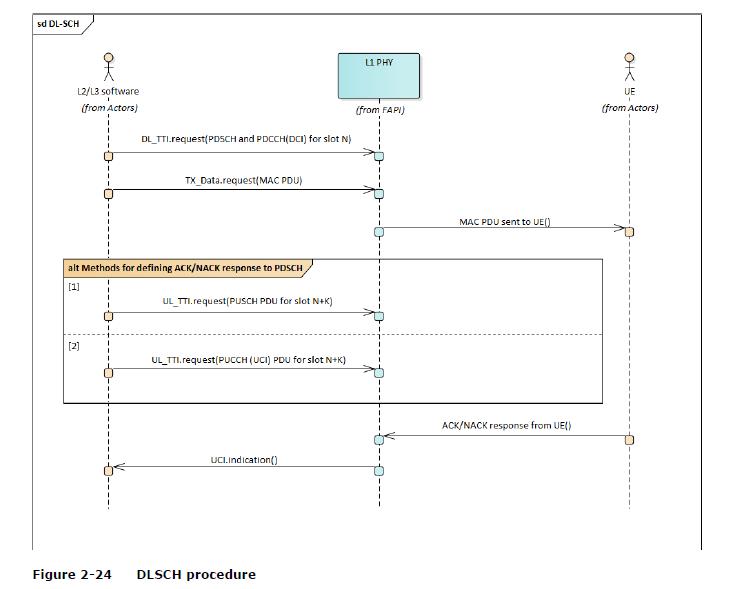

2.2.4.3 DL-SCH

DL-SCH信道用于基站给UE发送用户特定的业务数据,该信道采用了混合重传机制HARQ, 因此,基站软件在调度DL-SCH信道上的下行业务数据的时候,需要同时要为UE调度好ACK/NACK信息的上行资源。调度过程如下:

- L2软件通过DL_TTI.request(PDSCH, PDCCH DCI)进行时隙调度

- L2软件通过Tx_Data.request (MAC PDU)发送DL-SCH信道的PDU

- L1 PHY通过DL-SCH信道给UE发送数据

- L2软件通过DL_TTI.request(PDSCH)进行时隙调度

- L2软件通过DL_TTI.request(PDCCH)进行时隙调度

- L1 PHY在PDCCH信道接收UE的应答

- L1 PHY通过UCI.indiation指示UE的应答信息。

2.3 RF和波束赋型(P19接口):MAC层控制RF

待续。。。。。

作者主页(文火冰糖的硅基工坊):文火冰糖(王文兵)的博客_文火冰糖的硅基工坊_CSDN博客

本文网址:https://blog.csdn.net/HiWangWenBing/article/details/117602098

以上是关于FAPI专题-6:5G FAPI接口 - 中文规范-2- 主要流程的主要内容,如果未能解决你的问题,请参考以下文章

FAPI专题-7:5G FAPI接口 - 中文规范-3- P5消息格式

ORAN专题系列-27:5G FAPI接口 - 中文规范-1- 概述总体架构

FAPI专题-5:5G nFAPI接口 - 中文规范-4-VNF与PHY之间的时隙定时管理

ORAN专题系列-24:5G nFAPI接口 - 中文规范-1- 概述总体框架