AD7606调试笔记:采集多路不正常,少采集几路就正常

Posted 四臂西瓜

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了AD7606调试笔记:采集多路不正常,少采集几路就正常相关的知识,希望对你有一定的参考价值。

AD7606调试笔记:采集多路不正常,少采集几路就正常了

问题描述:

最近在调试嵌入式比赛的作品,用单片机同时带动两个7606同步采集的过程中,发现采集8+3路信号的时候,后3路数据不对,当采集8+2路时正常。

查错方案:

处理速度不够

当然首先怀疑是速度不够快,我使用的条件是32k采样率,一次采集至多只能花费32us。DEBUG后,发现,实际上只用了约17us,对于32us的要求来说绰绰有余,说是快很多也毫不过分。我电赛时为了克服HAL库的缓慢,能高速得带动7606,专门用IO口模拟SPI驱动的7606。

排除速度问题。

时序不对

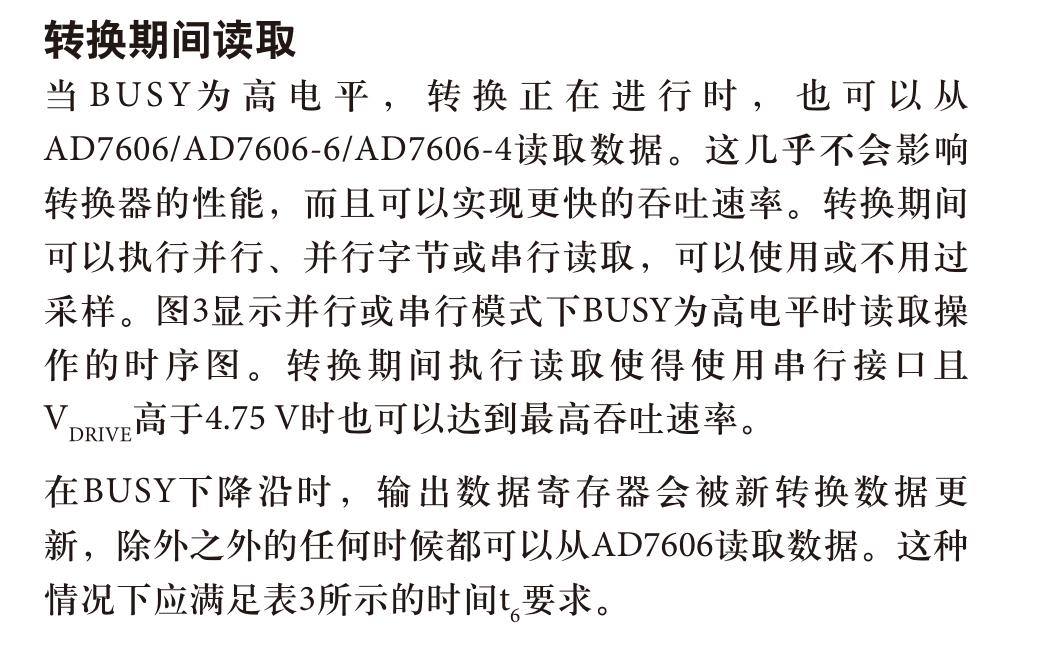

选用的是4倍过采样,上升沿读取,也就是转换期间读取。数据手册上描述如下:

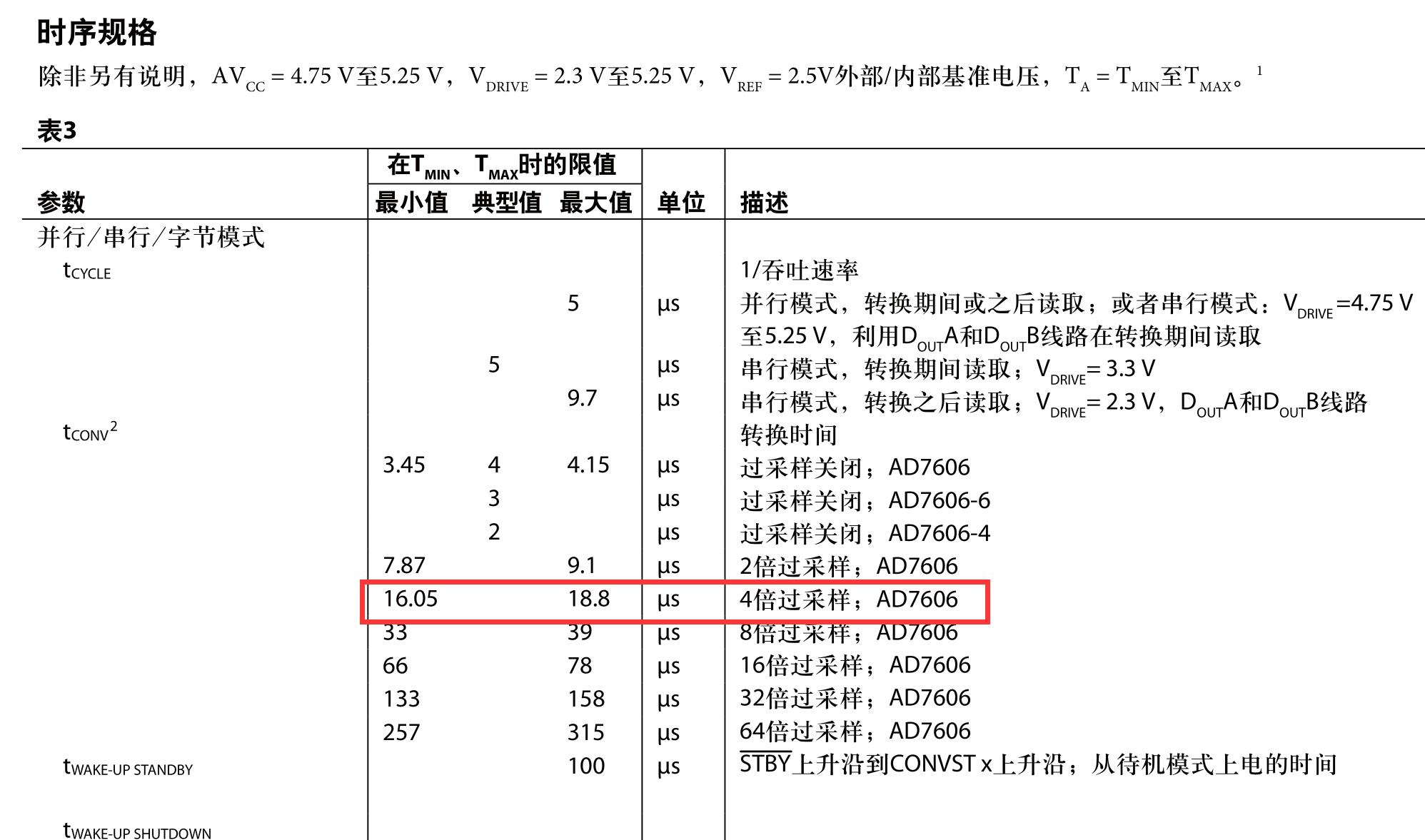

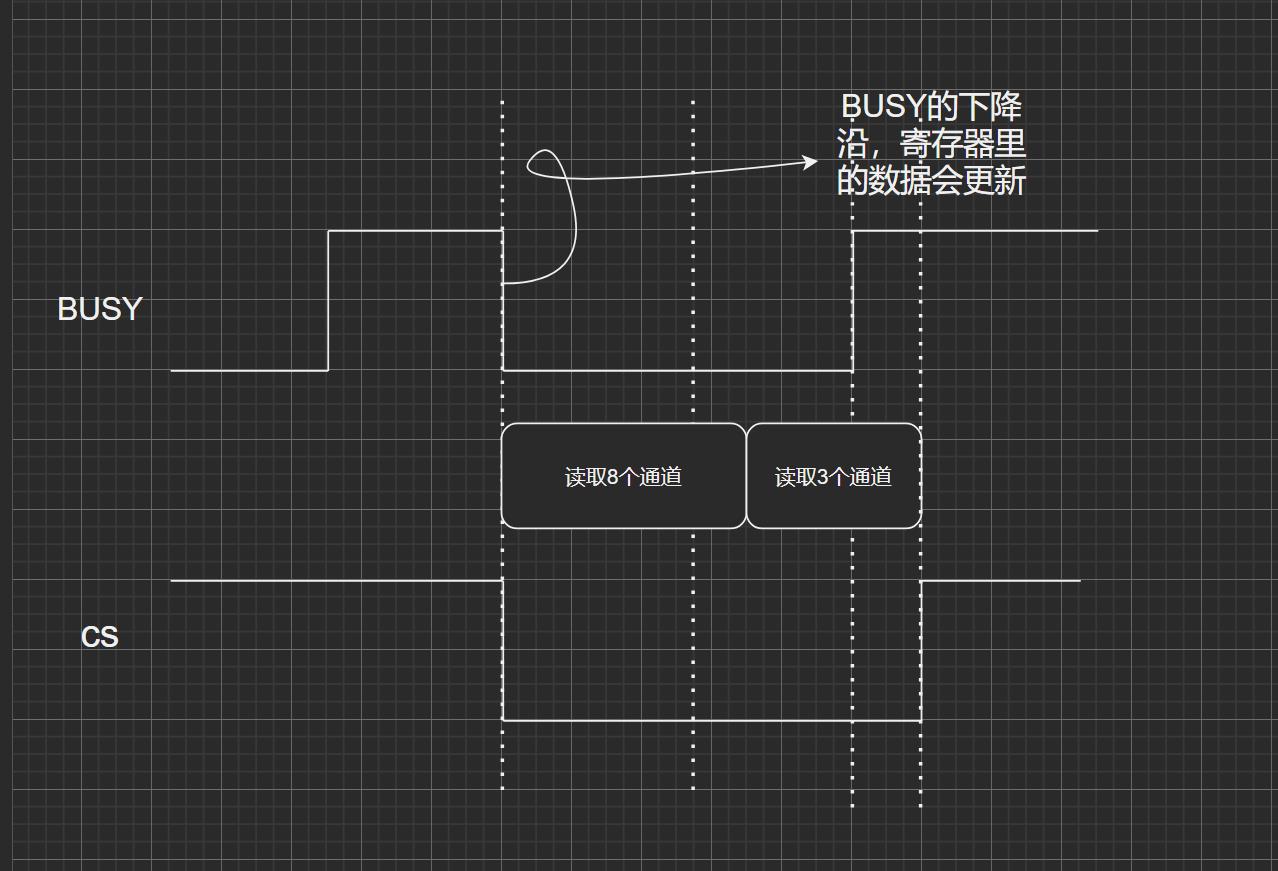

于是有疑问了,会不会是我采集的时间太长,在BUSY的高电平持续时间内没有读取完成?当BUSY下降沿到来时,寄存器数据更新了,我此时正在读取,数据自然就出错了。很有可能,开始检验。

锁定时序问题,通过DEBUG查看,前8个通道的数据花费了13.34us,后3路花费了4us左右。

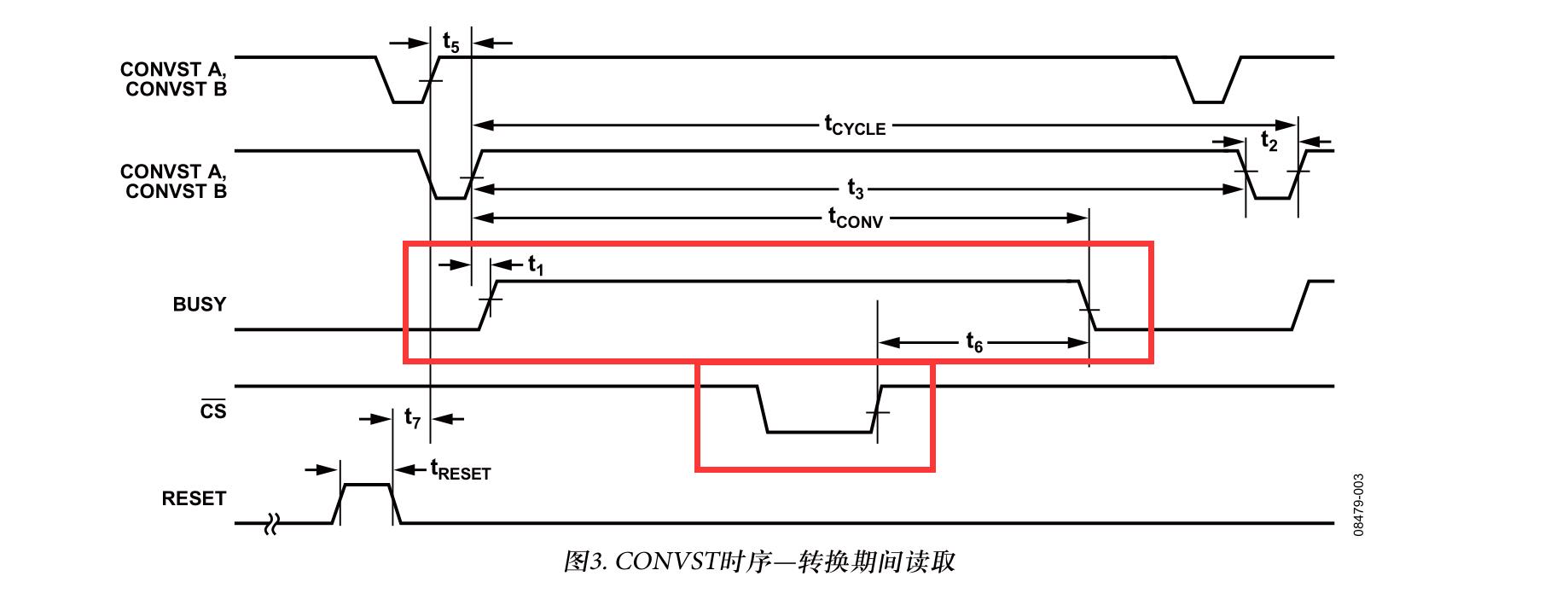

我使用的是4倍过采样率,转换时间,也就是BUSY持续高电平的时间是16-18us。

嗯?!16us,我的采样时间是17us多,正好赶上了BUSY的下降沿。

如上是错误的时序。

解决办法

延时

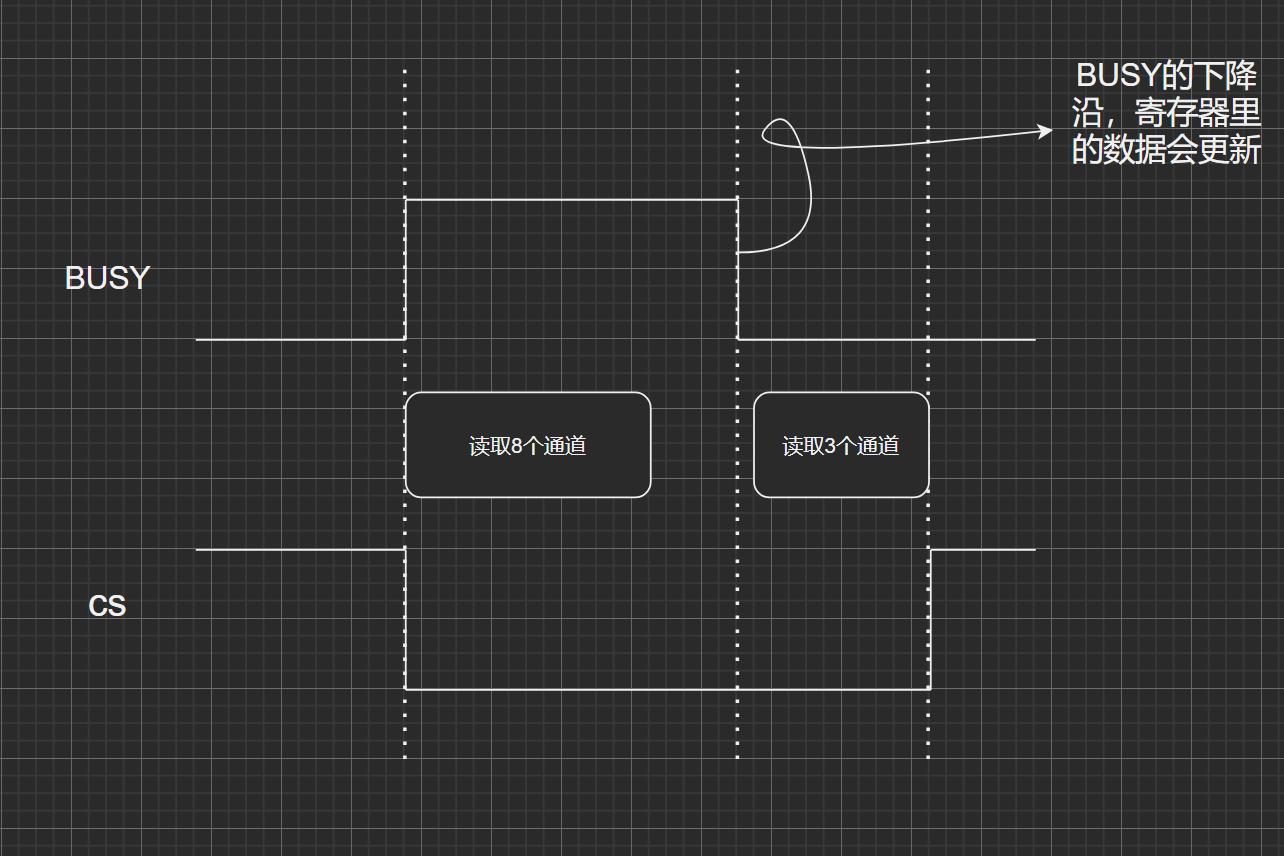

读取3个通道和读取8个通道之间,加入延时。如下图。延时5us就可以了。

这样解决会有一个问题,就是8路数据和3路数据不再是同步的了。这不满足要求呀。

转换完成读取

将触发改成BUSY的下降沿触发,这样就改成了转换完成再去读取。

经过测试,数据正确。可是大家一定也注意到了,我在读取后3路时,BUSY又被拉高了,开始新的一轮测量。这样是否会影响呢?根据我测到的数据来看是不影响的。那么他是否会影响呢?

是否影响?

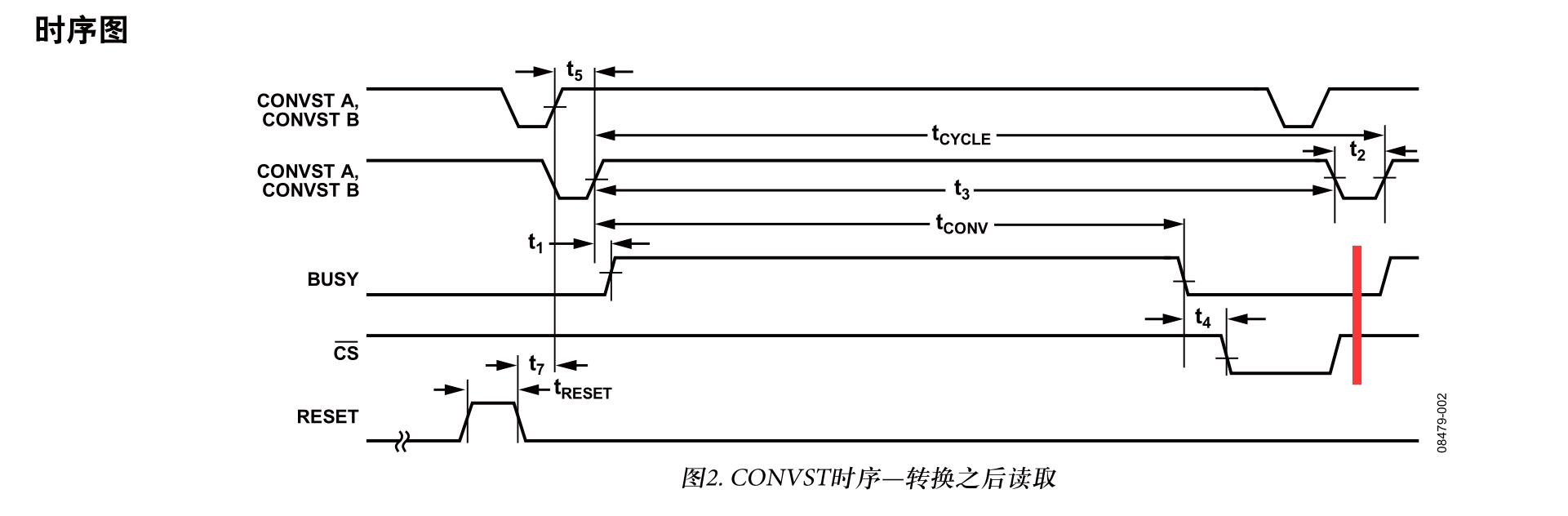

我们观察数据手册上的时序图。BUSY上升沿前,是完成了采集的。但是也没有指明是否可以这样测。不如来做个实验验证验证。

我让我手上的两个7606,去采集16路信号。采集时间如下,用了26.6us。32k采样率下,一个周期31.25us,BUSY高电平16us,低电平约15us,下降沿开始采集,采集了26.6us,明显已经进入了下一个周期的BUSY的高电平。严重超时。

开启采集,观察数据。数据正常!看来采集是可以持续到下一个周期的BUSY高电平。

结论

- 转换完后读取数据:上面的问题,基本上是由于采用了转换期间读取导致的。转换期间读取,只能在BUSY高电平下进行,比如这里的16us,有时间的限制。改用下降沿触发,就可以在一整个周期内读取信号,也就是这里的31.25us。

- 注意时序:叮嘱自己一下。

未若头发因风起

- 如果觉得本文章对你有作用,请大方的点个赞吧

以上是关于AD7606调试笔记:采集多路不正常,少采集几路就正常的主要内容,如果未能解决你的问题,请参考以下文章