MIPI协议--物理层D-PHY

Posted bobuddy

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了MIPI协议--物理层D-PHY相关的知识,希望对你有一定的参考价值。

通读了一下MIPI物理层D-PHY的规格书,拿掉了规格书中一些冗余繁复的部分,留下了一些比较重要的内容,现总结如下:

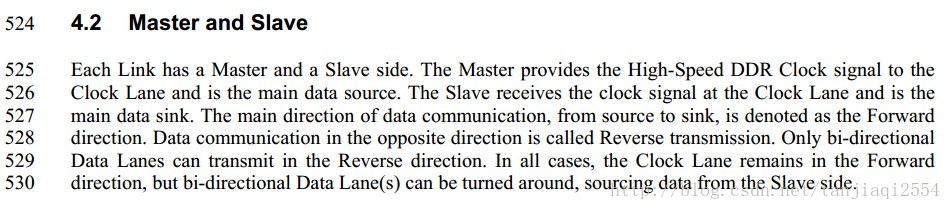

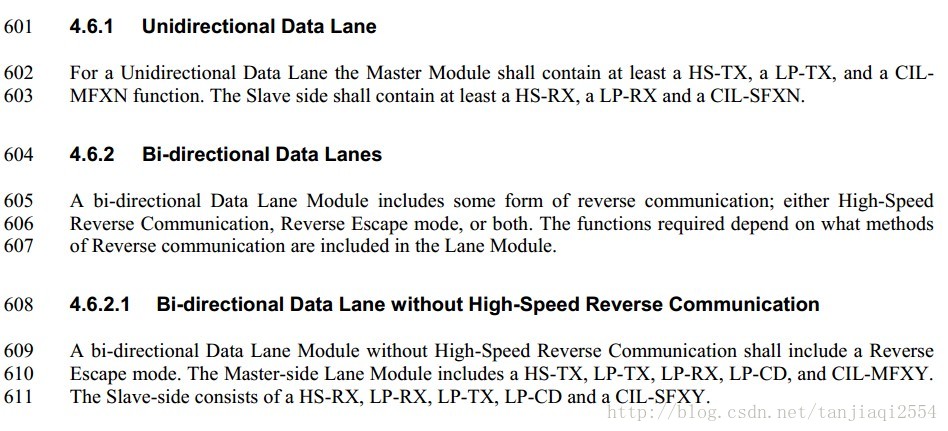

规格书中前部分章节大篇幅论述了D-PHY的几种内部实现结构,D-PHY采用的是非对称主从结构,即一个lane通道中同一时刻必须存在一个主,一个从。并根据以上传输方向性,定义了前向通道和反向通道。

又由于D-PHY支持高速和低功耗模式,结合其lane可支持半双工的特性,就衍生出了具有不同功能的lane属性,而集成不同lane的集合,就构成了不同的D-PHY结构,lane的差异主要体现在如下几点:

1. 首先纯单端是不需要LP-CD模块的。

2. 而双端又可以分为仅支持低功耗双端和高速低功耗模式均可双端的情况。

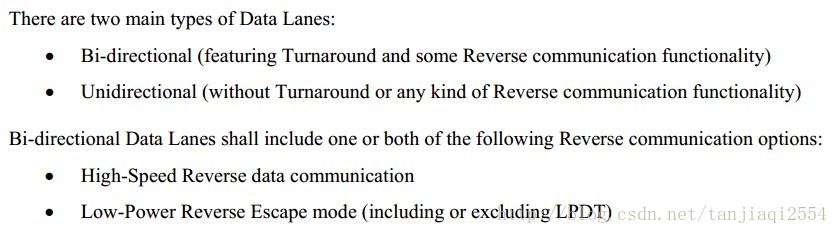

针对具有以上不同lane的D-PHY结构,就需要具有不同功能的CIL(Control and Interface Logic)模块来协同处理数据传输,其CIL后缀首字母缩写含义可参看以下表格。

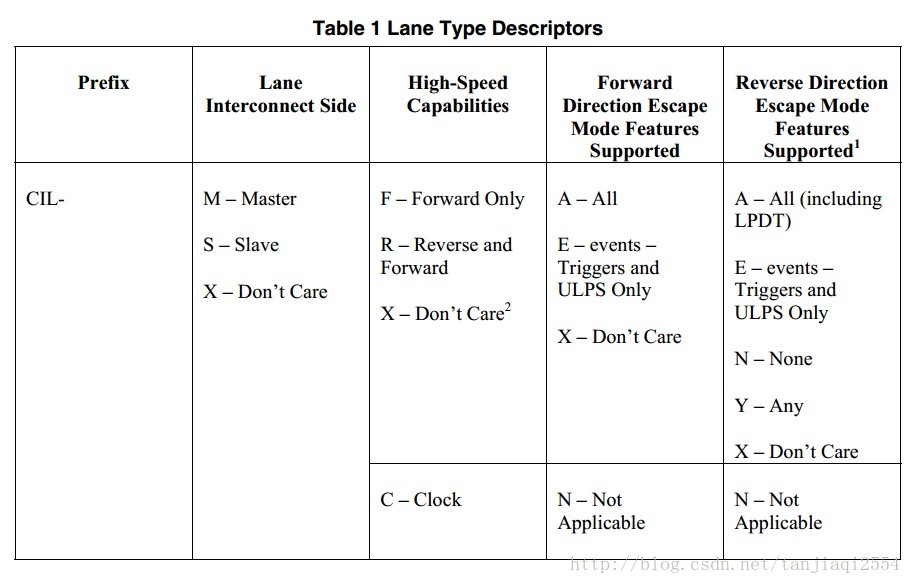

下面这张图说明了高速信号和低功耗信号的MIPI差分信号电压摆幅情况。

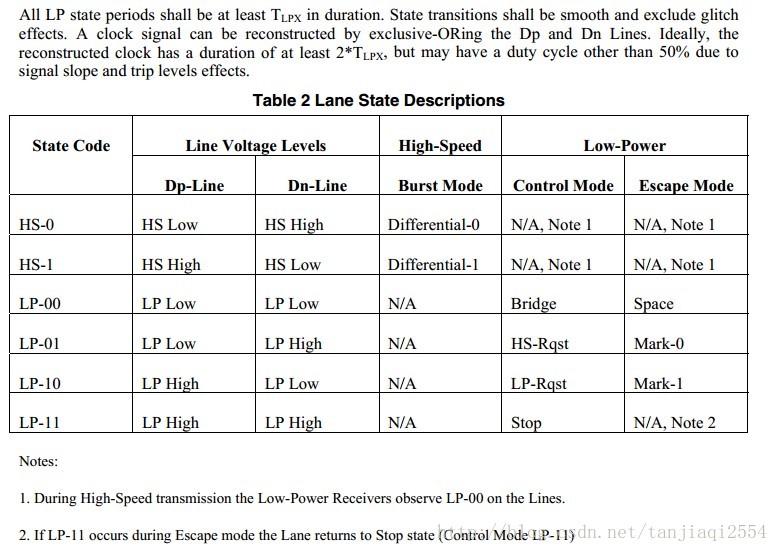

由于MIPI是差分信号,即一条lane由两条线组成,因此通过高低电平的组合,这两条线应该有4种状态,但图中可以很明显看到高速信号摆幅仅为200mV,因此为了确保传输稳定,高速时我们认为信号只有两种状态,即互为高低压交错的两种状态,因此lane状态则共有如下表所示的六种状态。一对lane中的正信号线为Dp-Line,负信号线为Dn-Line.

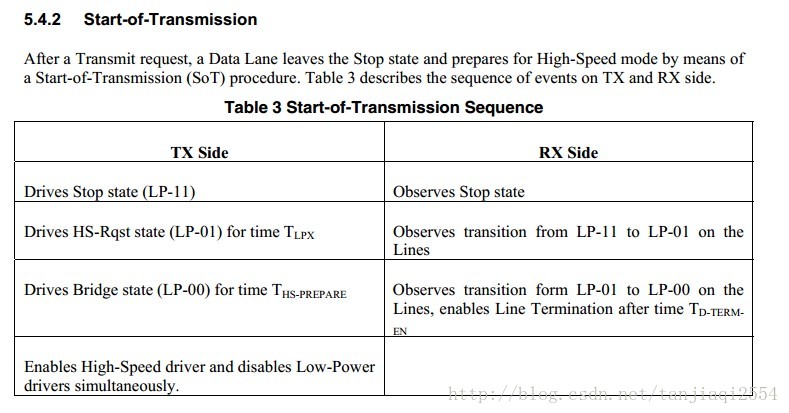

知道了lane的这六种状态接下来,我们可以利用低功耗的状态来组合我们开启高速传输等的指令序列了,如下表所示:

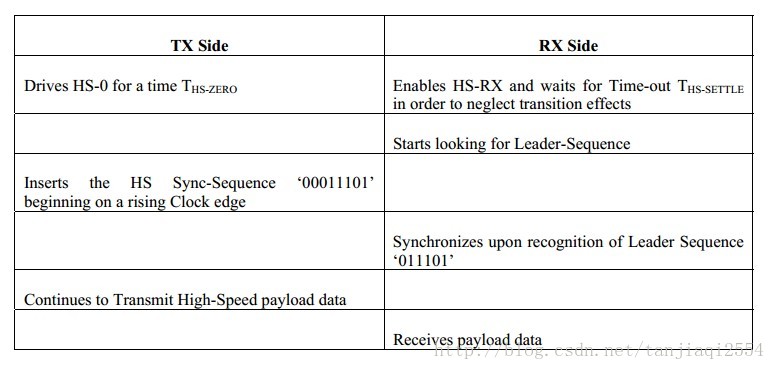

我们启动高速传输的SOT指令,使用的就是如上的(LP-11=>LP-01=>LP-00=>HS-0[持续Ths-zero时间]=>发送HS同步序列“00011101”)序列。SOT接收器状态检索过程不再赘述,请自行读表。结束传输的EOT序列比较简单,也请自行读表。

从以上时序图,我们能清楚的看到SOT和EOT各状态切换的顺序,以及所需的时间。

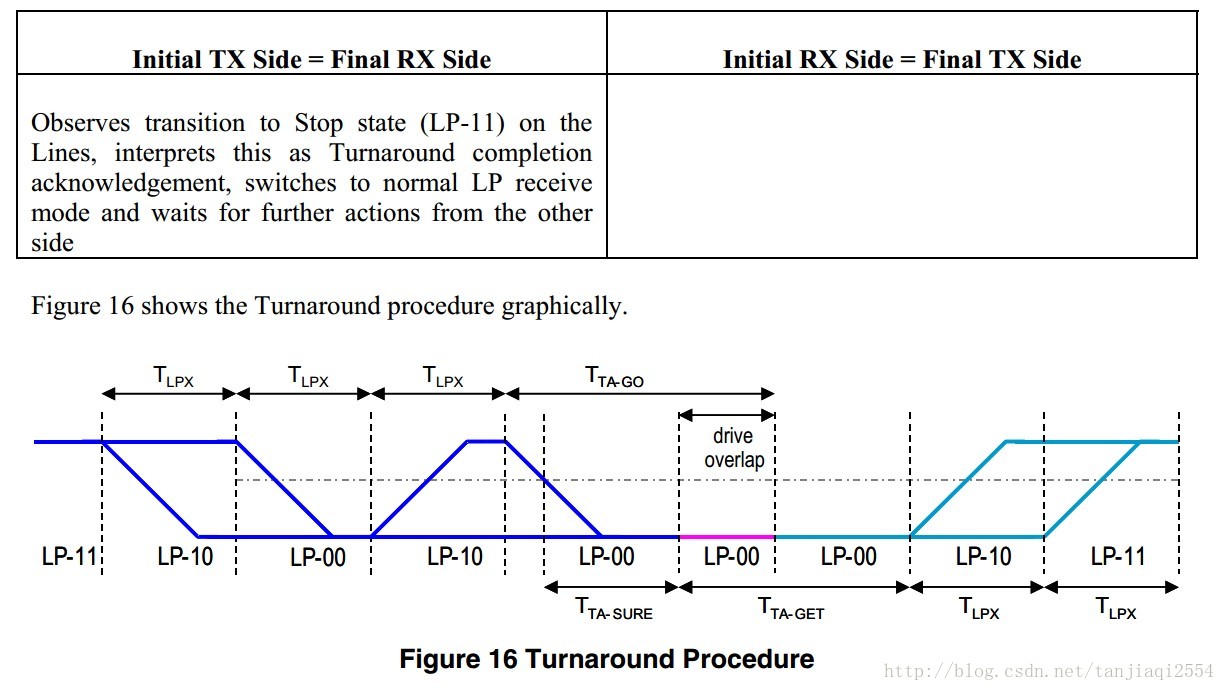

接下拉我们看看双端数据lane,传输方向调换指令Turnaround.从以下表格和时序图可以清楚的看到各LP state切换的时序,所以也不赘述了。

这里唯一想提一下的是,注意如上时序图中,在一个相对较长的LP-00状态中,存在一个drive overlap的主从控制权交换过程。执行完这条指令,我们并没有转换主从关系,但是我们转换了传输方向,在前向通道至反向通道及反向通道至前向通道间,进行了切换。

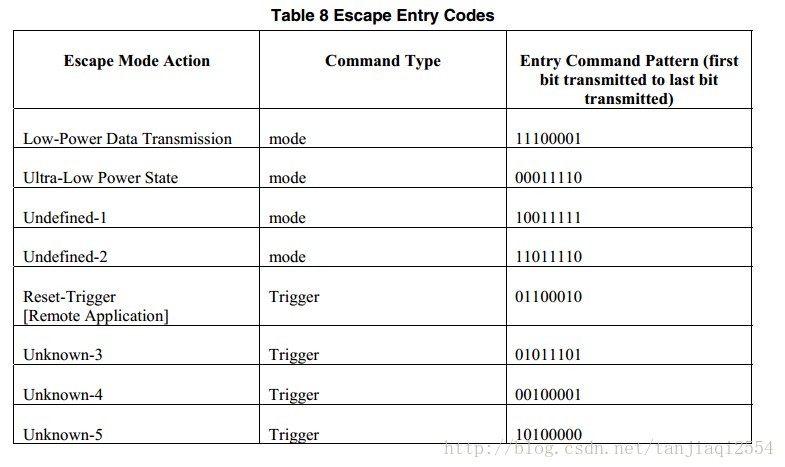

接下来我们再看看Escape Mode指令,首先,这条指令是用来做什么的呢,它是用来给MIPI提供一些额外功能处理能力的LP指令,且值得注意的一点是,与前面不同,它是一条基于空间独热(Space-One-Hot) 位编码的异步指令,由于是异步指令,因此Data lane在操作这条指令时,并不依赖于Clk Lane。进入Escape Mode的引导步骤码序为LP-11=>LP10=>LP00=>LP01=>LP00.此外,因为是拿来指定一些功能,因此不同编码就具有不同的意义,这里我们先从下表看看它所具有的一些功能码。

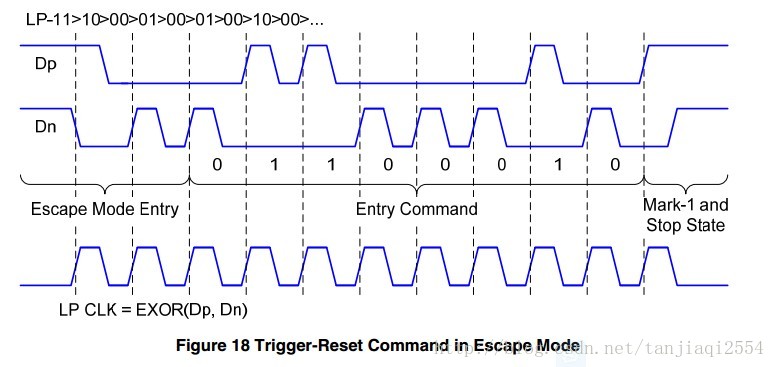

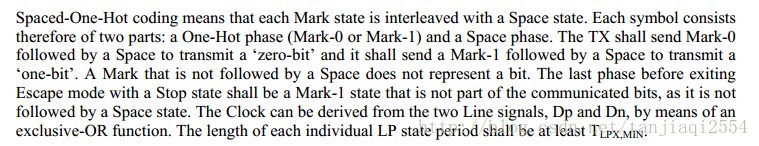

这里我们以上表中的Reset-Trigger指令为例,分析一下如下时序图,首先我们在时序图前半部分发现了进入Escape Mode的引导码LP-11=>LP10=>LP00=>LP01=>LP00。接下来我们来看看这个所谓的空间独热编码(Space-One-Hot) ,我们发现它占用两个LP状态的时间来表示一位数据,这里小编我以一种等价的方式来评价这种空间独热编码,注意,实际其定义不是这样的。我们发现它的0位,等价于用LP-01=>LP00表示,它的1位等价于用LP-10=>LP00表示,你也可以认为0位和1位的Dp和Dn状态是互相交错的。此外,从图中我们发现它还有一个显著的特点,就是在发送Space-One-Hot编码过程中,Dp和Dn线异或刚好是以一个LP状态周期Tlpx为周期的时钟,因此这个特性可以用来做校验,不符合Space-One-Hot特性的数据信号将被丢弃。然后小编我在表后在附上关于Space-One-Hot官方给出的解释。

官方还指出在退出Escape-Mode时,必须停留在Mark-1状态,这里等价于LP10状态。

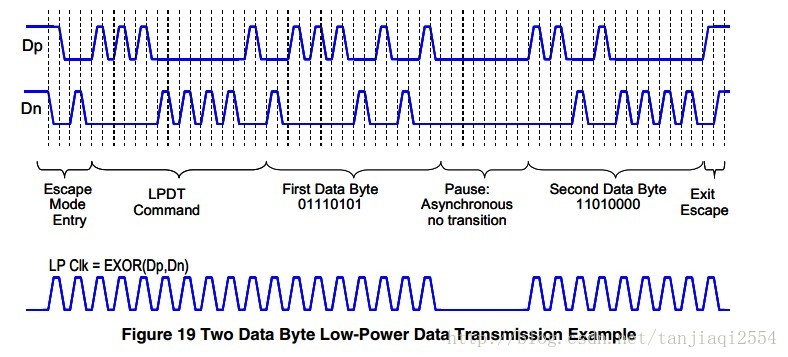

从上面的Escape Mode的功能码中发现,它是可以用来触发Low-Power Data Transmission(LPDT)的,但传输的数据仍然要遵循Space-One-Hot的异步传输规则。保持一个LP00(官方称为Space)状态,可以用来暂停数据传输。老规矩仍然上一张图给读者分析。

Escape Mode的功能码中的Ultra-Low Power指令比较简单,这里读者自己看看官方解释就好。

官方文档中,关于Data Lane的说明到此就基本结束了。

接下来我们看看Clk Lane,首先Clk Lane是单端的,常规的Escape Mode指令也不支持,仅支持ULPS指令。

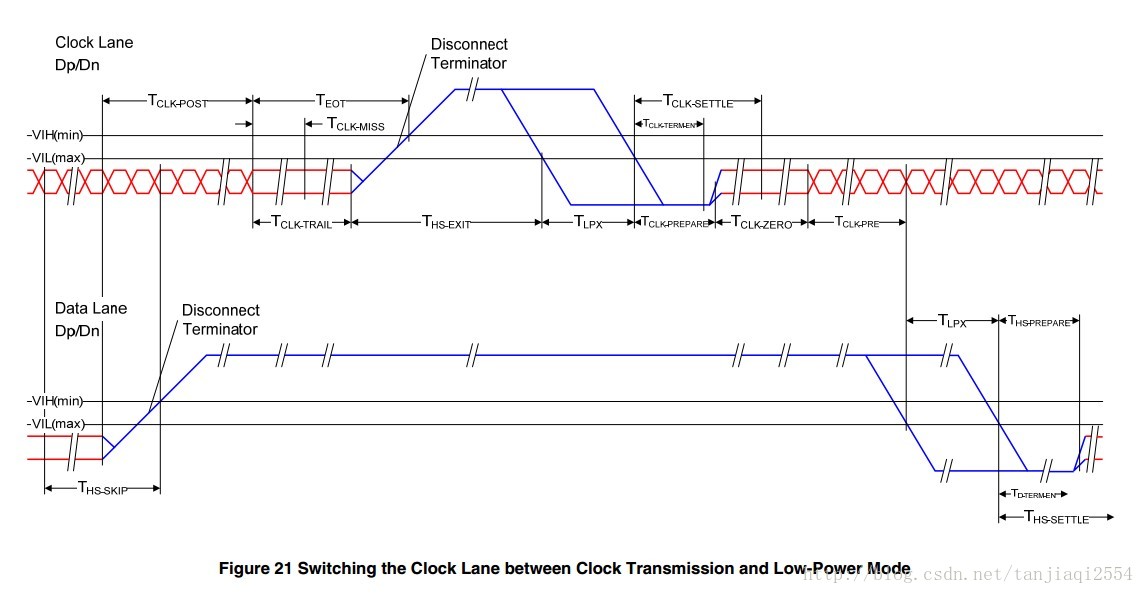

接下来结合上面的时序图和下面的表格,我们来分析一下Clk Lane在切换高速和低功耗模式时的步骤,首先是进入低功耗模式的步骤如下:

1. Clk lane处于交错高速信号HS-0和HS-1的状态

2. 最后一个数据通道也进入低功耗状态了

3. Clk lane在以上状况下依然保持高速时钟状态一段时间,时间长度为Tclk-post,并最后以HS-0状态结束

4. 保持HS-0状态Tclk-trail时间

5. 开始切换HS-TX模块至LP-TX模块,并驱动LP-11状态,保持Ths-exit时长。至此即进入了LP模式。

接下来我们看看如何退出LP模式进入高速模式:

1. LP-TX模块驱动停止状态LP-11

2. 驱动LP-01状态,并维持Tlpx时长

3. 驱动LP-00状态,并维持Tclk-prepare时长

4. 驱动HS-0状态,并维持Tclk-zero时长,并在这段时间内同步完成LP-TX到HS-TX的模块切换。

5. 在任一条Data Lane启动前,保持高速时钟状态Tclk-pre时长。接下来Data Lane也开始启动切换,切换步骤结合前述说明理解。

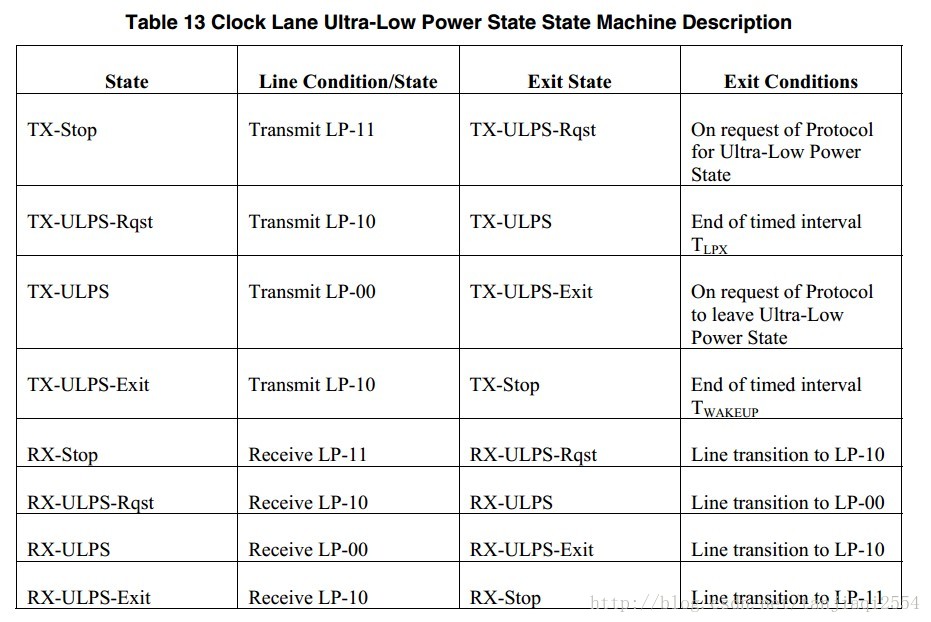

注意Clk Lane虽然不支持Escape Mode,但是是支持Ultra-Low Power状态(ULPS)的,由于比较简单这里小编也只贴一张图,读者自己理解了。

接下来规格书中总结了以上LP状态机切换的步骤,同时讲解了MIPI的lane初始化的过程、错误侦测的内容,以及进一步讲解了MIPI的一些电气特性和信号衰减增益相关的内容,小编这里不关心这些内容,若读者关心,请自行去阅读了。

下一篇中小编我打算以一种载荷格式传输为实例,详细探讨一下行场有效时间和总时间的估算方法,以便进一步探讨一些MIPI传输方案在接收器上的时钟参数选取方法。

以上是关于MIPI协议--物理层D-PHY的主要内容,如果未能解决你的问题,请参考以下文章

Crosslink-NX器件应用案例:SLVS/LVDS/HiSPI/DVP转MIPI D-PHY CSI