RGMII接口

Posted smartvxworks

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了RGMII接口相关的知识,希望对你有一定的参考价值。

RGMII接口

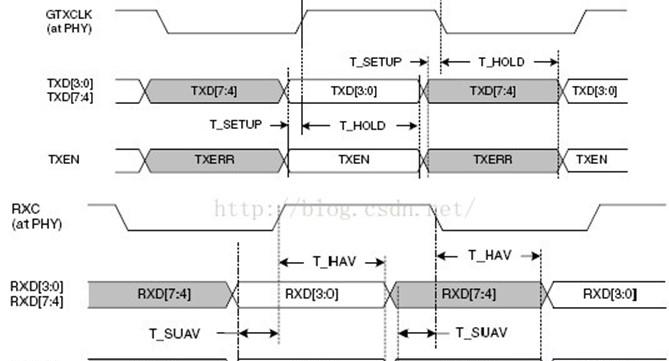

即Reduced GMII,是RGMII的简化版本,将接口信号线数量从24根减小到14根(COL/CRS端口状态指示信号,这里没有画出),时钟频率仍旧为125MHz,TX/RX数据宽度从8为变为4位,为了保持1000Mbps的传输速率不变,RGMII接口在时钟的上升沿和降低沿都采样数据。在参考时钟的上升沿发送GMII接口中的TXD[3:0]/RXD[3:0],在参考时钟的降低沿发送GMII接口中的TXD[7:4]/RXD[7:4]。

RGMI同时也兼容100Mbps和10Mbps两种速率,此时参考时钟速率分别为25MHz和2.5MHz。 TX_EN信号线上传送TX_EN和TX_ER两种信息,在TX_CLK的上升沿发送TX_EN,降低沿发送TX_ER;一样的,RX_DV信号线上也传送RX_DV和RX_ER两种信息,在RX_CLK的上升沿发送RX_DV,降低沿发送RX_ER。RGMII的收发时序以下图所示:

管理配置

◇MDC——配置接口时钟

◇MDIO——配置接口I/O

管理配置接口控制PHY的特性。该接口有32个寄存器地址,每一个地址16位。其中前16个已经在"IEEE 802.3,2000-22.2.4Management Functions"中规定了用途,其他的则由各器件本身指定。

以上是关于RGMII接口的主要内容,如果未能解决你的问题,请参考以下文章