13.STC15W408AS单片机SPI

Posted 小猿猪哥

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了13.STC15W408AS单片机SPI相关的知识,希望对你有一定的参考价值。

https://mp.weixin.qq.com/s/vq-ON4pPU16BtIxYhHpWVQ

STC15系列单片机还提供另一种高速串行通信接口 —— SPI接口。SPI是一种全双工、高速、同步的通信总线,有两种操作模式:主模式和从模式。在主模式中支持高达3 Mbps的速率(工作频率为12MHz时,如果CPU主频采用20MHz到36MHz,则可更高,从模式时速度无法太快,SYSclk/4以内较好),还具有传输完成标志和写冲突标志保护。

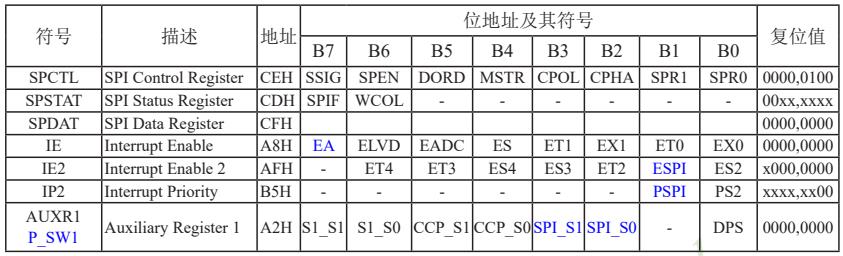

一、 与SPI功能模块相关的特殊功能寄存器

1.1 SPI控制寄存器SPCTL

SPCTL : SPI控制寄存器

SSIG:SS引脚忽略控制位。

SSIG=1,MSTR(位4)确定器件为主机还是从机

SSIG=0,SS脚用于确定器件为主机还是从机.SS脚可作为I/O口使用(见SPI主从选择表)

SPEN:SPI使能位。

SPEN=1,SPI使能;

SPEN=0,SPI被禁止,所有SPI引脚都作为I/O口使用。

DORD:设定SPI数据发送和接收的位顺序

DORD=1, 数据字的LSB(最低位)最先发送;

DORD=0, 数据字的MSB(最高位)最先发送。

MSTR:主/从模式选择位(见SPI主从选择表)。

CPOL:SPI时钟极性

CPOL=1,SCLK空闲时为高电平。SCLK的前时钟沿为下降沿而后沿为上升沿。

CPOL=0,SCLK空闲时为低电平。SCLK的前时钟沿为上升沿而后沿为下降沿。

CPHA:SPI时钟相位选择。

CPHA=1, 数据在SCLK的前时钟沿驱动,并在后时钟沿采样

CPHA=0, 数据在SS为低(SSIG=0)时被驱动,在SCLK的后时钟沿被改变,并在前时钟沿被采样。(注:SSIG = 1时的操作未定义)

SPR1、SPR0:SPI时钟频率选择控制位:

表中,CPU_CLK是CPU时钟。

1.2 SPI状态寄存器SPSTAT

SPSTAT: SPI状态寄存器

SPIF:SPI传输完成标志。

当一次串行传输完成时,SPIF置位 SPI中断被打开(即ESPI (IE2.1) 和EA(IE.7) 都置位),则产生中断。SPI处于主模式且SSIG=0时,如果SS为输入并被驱动为低电平,SPIF也将置位 "模式改变"。SPIF标志通过软件向其写入"1"清零。

WCOL:SPI写冲突标志。

在数据传输的过程中如果对SPI 数据寄存器SPDAT执行写操作,WCOL将置位。WCOL标志通过软件向其写入"1"清零。

1.3 SPI数据寄存器SPDAT

SPDAT: SPI数据寄存器

SPDAT.7 - SPDAT.0: 传输的数据位Bit7~Bit0。

1.4 中断允许寄存器2

ESPI : SPI中断允许位

ESPI=1,允许SPI中断,

ESPI=0,禁止SPI中断。

二、SPI接口的结构

STC15系列单片机的SPI功能方框图如下图所示。

SPI的核心是一个8位移位寄存器和数据缓冲器,数据可以同时发送和接收。在SPI数据的传输过程中,发送和接收的数据都存储在数据缓冲器中。对于主模式,若要发送一字节数据,只需将这个数据写到SPDAT寄存器中。主模式下SS信号不是必需的;但是在从模式下,必须在SS信号变为有效并接收到合适的时钟信号后,方可进行数据传输。在从模式下,如果一个字节传输完成后,SS信号变为高电平,这个字节立即被硬件逻辑标志为接收完成,SPI接口准备接收下一个数据。

三、SPI接口的数据通信

SPI接口 有4个管脚 SCLK, MISO, MOSI和SS,可在3组管脚之间进行切换SCLK/P1.5,MISO/P1.4, MOSI/P1.3和SS/P1.2 ]; SCLK_2/P2.1, MISO_2/P2.2, MOSI_2/P2.3和SS_2/P2.4][SCLK_3/P4.3, MISO_3/P4.1, MOSI_3/P4.0和SS_3/P5.4]。MOSI ( Master Out Slave In,主出从入):主器件的输出和从器件的输入,用于主器件到从器件的串行数据传输。当SPI作为主器件时,该信号是输出;当SPI作为从器件时,该信号是输入。数据传输时最高位在先,低位在后 根据SPI规范,多个从机可以共享一根MOSI信号线。在时钟边界的前半周期,主机将数据放在MOSI信号线上,从机在该边界处获取该数据。MISO ( Master In Slave Out,主入从出):从器件的输出和主器件的输入,用于实现从器件到主器件的数据传输。当SPI作为主器件时,该信号是输入;当SPI作为从器件时,该信号是输出。数据传输时最高位在先,低位在后 SPI规范中,一个主机可连接多个从机,因此,主机的MISO信号线会连接到多个从机上,或者说,多个从机共享一根MISO信号线。当主机与一个从机通信时,其他从机应将其MISO引脚驱动置为高阻状态。SCLK ( SPI Clock,串行时钟信号):串行时钟信号是主器件的输出和从器件的输入,用于同步主器件和从器件之间在MOSI和MISO线上的串行数据传输。当主器件启动一次数据传输时,自动产生8个SCLK时钟周期信号给从机。在SCLK的每个跳变处(上升沿或下降沿)移出一位数据。所以,一次数据传输可以传输一个字节的数据。

SS( Slave Select,从机选择信号):这是一个输入信号,主器件用它来选择处于从模式的SPI模块。主模式和从模式下SS的使用方法不同。在主模式下,SPI接口只能有一个主机,不存在主机选择问题,该模式下SS不是必需的。主模式下通常将主机的SS管脚通过10KΩ的电阻上拉高电平。每一个从机的SS接主机的I/O口,由主机控制电平高低,以便主机选择从机。在从模式下,不管发送还是接收,SS信号必须有效。因此在一次数据传输开始之前必须将SS为低电平。SPI主机可以使用I/O口选择一个SPI器件作为当前的从机。

SPI从器件通过其SS脚确定是否被选择。如果满足下面的条件之一,SS就被忽略:如果SPI系统被禁止,即SPEN(SPCTL.6)= 0(复位值)如果SPI配置为主机,即MSTR(SPCTL.4)=1,并且P1.2/SS配置为输出( P1M0.2和P1M1.2)如果SS脚被忽略,即SSIG(SPCTL.7)= 1,该脚配置用于I/O口功能。

注:即使SPI被配置为主机(MSTR = 1),它仍然可以通过拉低SS脚配置为从机(如P1.2/SS配置为输入且SSIG=0)。要使能该特性,应当置位SPIF(SPSTAT.7)。

四、SPI测试代码

这里采用的是查询法。

#define u16 unsigned int

#define u8 unsigned char

// 控制寄存器 SPCTL

#define SSIG 1 // 1: 忽略SS脚,由MSTR位决定主机还是从机 0: SS脚用于决定主从机。

#define SPEN 1 // 1: 允许SPI,0:禁止SPI,所有SPI管脚均为普通IO

#define DORD 0 // 1:LSB先发,0:MSB先发

#define MSTR 1 // 1:设为主机 0:设为从机

#define CPOL 1 // 1: 空闲时SCLK为高电平,0:空闲时SCLK为低电平

#define CPHA 1 // 数据在SCLK的前时钟沿驱动,并在后时钟沿采样

#define SPEED_4 0 // fosc/4

#define SPEED_8 1 // fosc/8

#define SPEED_16 2 // fosc/16

#define SPEED_32 3 // fosc/32

// 状态寄存器 SPSTAT

#define SPIF 0x80 //SPI传输完成标志。写入1清0。

#define WCOL 0x40 //SPI写冲突标志。写入1清0。

void Spi_Init(void)

{

SPDAT = 0; //初始化SPDAT

SPSTAT = SPIF | WCOL; //清除SPI状态标志

SPCTL = (SSIG << 7) + (SPEN << 6) + (MSTR << 4) + (CPOL << 3) + (CPHA << 2) + SPEED_4;

}

void Spi_Send(u8 dat)

{

SPSTAT = SPIF + WCOL; //清0 SPIF和WCOL标志

SPDAT = dat; //发送一个字节

while (!(SPSTAT & SPIF)); //等待SPI数据传输完成

SPSTAT = SPIF + WCOL; //清0 SPIF和WCOL标志

}

以上是关于13.STC15W408AS单片机SPI的主要内容,如果未能解决你的问题,请参考以下文章