CPU - 指令流水线相关知识

Posted 王万林 Ben

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了CPU - 指令流水线相关知识相关的知识,希望对你有一定的参考价值。

CPU - 指令流水线相关知识

什么是指令流水线?

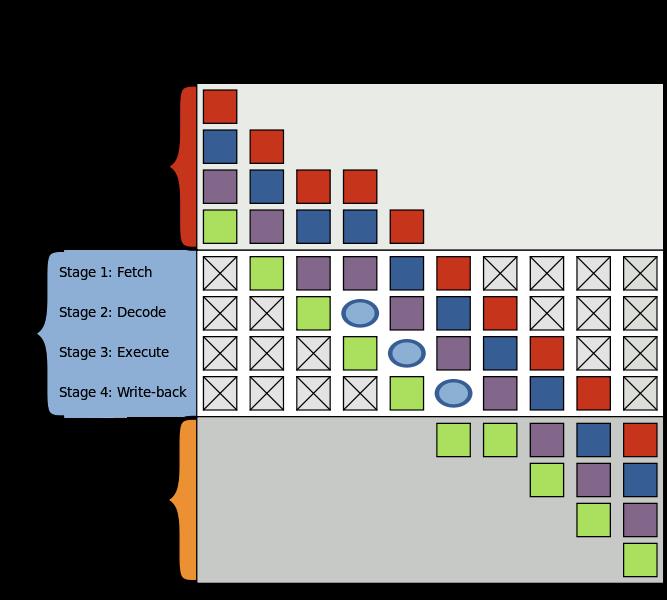

图片来自维基百科。如图所示,指令流水线有4个stage,分别是Fetch、Decode、Execute与Write-back。设计指令流水线,使得在同一个时刻,每个Stage都能执行不同指令的一个Stage,大大增加了执行指令的throughput。

什么是Bubble(NOP, no operation)instruction?

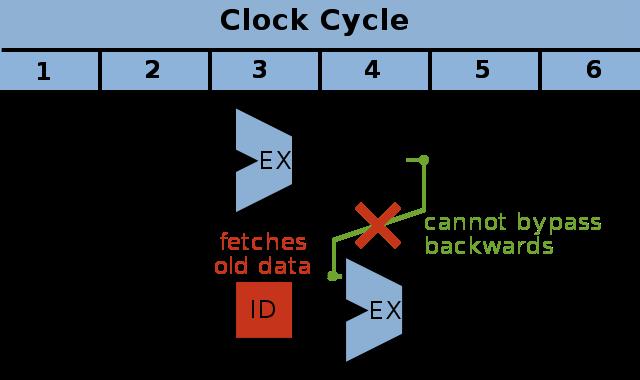

Bubble instruction是一条空指令,意在使得下一条指令再慢一个Stage。如图所示,

那么Bubble instruction有什么作用?

假设两条指令间,第二条指令的输入是第一条指令的输出,它们有依赖关系。如图所示,如果第二条指令紧跟(仅落后一个Stage)第一条指令,则第二条指令的输入无法从第一条指令的输出获得。

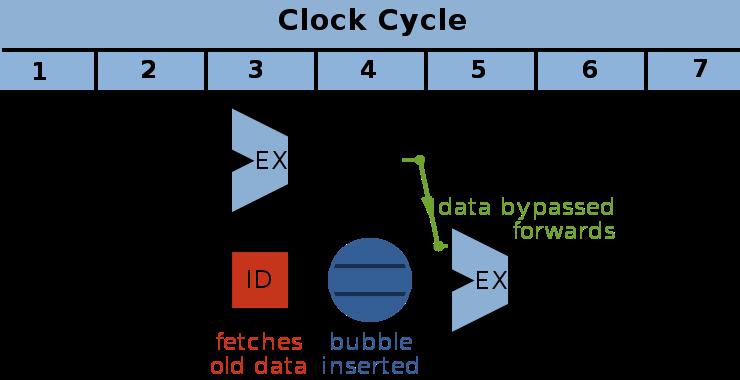

因此引入一个气泡,使得第二条指令的输入能匹配到第一条指令的输出,这巧妙地解决了上述问题。如图所示:

参考资料

https://en.wikipedia.org/wiki/Pipeline_stall

https://software.intel.com/content/www/us/en/develop/blogs/pipeline-speak-learning-more-about-intel-microarchitecture-codename-sandy-bridge.html

https://software.intel.com/content/www/us/en/develop/blogs/pipeline-speak-part-2-the-second-part-of-the-sandy-bridge-pipeline.html

https://software.intel.com/content/www/us/en/develop/articles/processor-specific-performance-analysis-papers.html

以上是关于CPU - 指令流水线相关知识的主要内容,如果未能解决你的问题,请参考以下文章