(计算机组成原理)第三章存储系统-第五节1:双端口RAM和多模块存储器

Posted 快乐江湖

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了(计算机组成原理)第三章存储系统-第五节1:双端口RAM和多模块存储器相关的知识,希望对你有一定的参考价值。

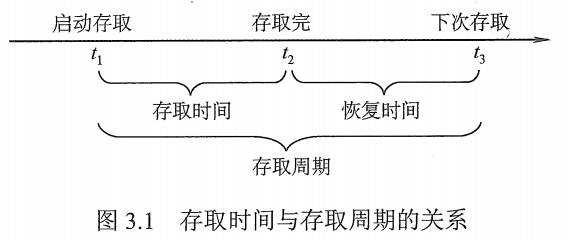

前面我们说到了存取周期的概念,存取周期是指可以连续读写的最短时间间隔

对于之前我们讲到过DRAM芯片,其恢复时间是比较长的,有可能会到达存取周期的几倍。

现代计算机的CPU通常都是多核的,那么如果此时多核CPU都要访问主存,是不是必须要等待芯片恢复后才能读取呢,如果主存恢复时间太长又该怎么办呢?

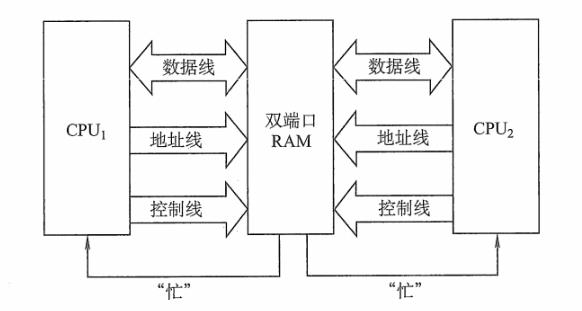

一:双端口RAM

该项技术可以优化多核CPU访问一根内存条的速度

双端口RAM是指同一个存储器有左右两个独立的端口,分别具有两组相互独立的地址线、数据线和读写控制线,允许两个独立的控制器同时异步地访问存储单元

- 两个端口的地址不相同时,在两个端口上进行读写操作一定不会发生冲突

- 两个端口同时存取存储器的同一地址单元时,会因数据冲突造成数据存储和读取错误

两个端口对同一主存操作有以下4种情况

1:两个端口不同时对同一地址单元读出数据

- 没有错误

2:两个端口同时对同一地址单元读出数据

- 没有错误

3:两个端口同时对同一地址单元写入数据

- 发生写入错误

4:两个端口同时对同一地址单元操作,一个写入,一个读出

- 发生读出错误

3、4情况的解决方法为:置“忙”信号 B ‾ U ‾ S ‾ Y ‾ \\overline B\\overline U\\overline S\\overline Y BUSY为0,由判断逻辑决定暂时关闭一个端口(延时)。未被关闭的端口正常访问,被关闭的延长一个很短的时间段后再访问

二:多模块存储器-多体并行

即便是单核的CPU其速度也是远远快于主存,因此CPU不能连续对主存进行访问,势必要等待主存的恢复时间到才能进行下次访问,可以看出这样的限制大大拖累了整机的性能。

多体并行存储器由多体模块组成。每个模块都有相同的容量和存取速度,各模块都有独立的读写控制电路、地址寄存器和数据寄存器。它们既能并行工作,又能交叉工作

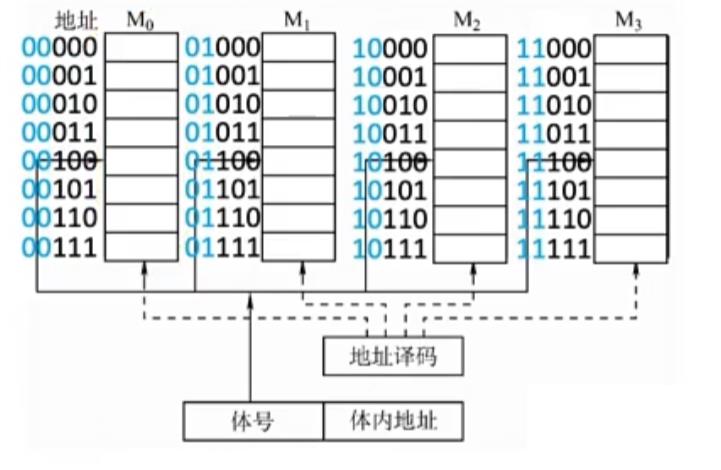

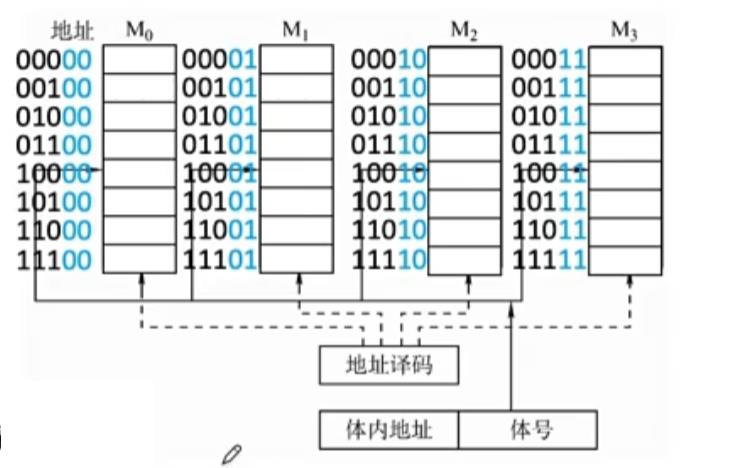

(1)高位交叉编址

高位交叉编址是指高位地址表示体号,低位地址为体内地址

如下图,存储器共有4个模块

M

0

−

M

3

M_{0}-M_{3}

M0−M3,你可以将其理解为“4根内存条”,按照这种方式编址后前两位它指定了选中的是哪一个内存条(有2位正好对应4个状态),后面的则决定了是该内存条中的具体地址

高位交叉编址方式下,总是把低的体内地址送到由高位体号确定的模块内进行译码。访问一个连续的主存块时,总是先在一个模块内访问,等到该模块访问完才转到下一个模块访问,CPU总是按顺序访问存储模块,存储模块不能并行访问,因为不能提高存储器的吞吐率

假设每个存储体的存取周期为T,存取时间为r,并且T=4r,如果采用这种编址方式的多体存储器,那么CPU真正花在读数据上的时间只有r,但是却要再花费3r的时间用来等,效率不高。也就是说连续读取n个存储字,就要耗时nT

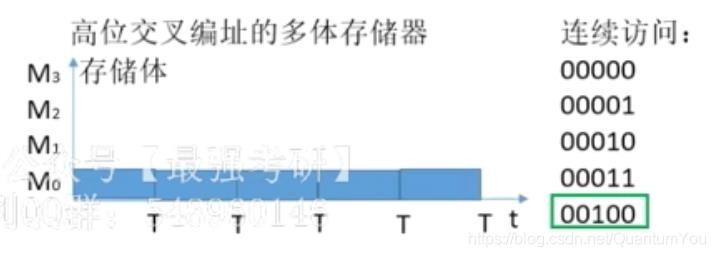

(2)低位交叉编址

低位交叉编址是指低位地址为体号,高位地址为体内地址

如下图,存储器共有4个模块

M

0

−

M

3

M_{0}-M_{3}

M0−M3,你可以将其理解为“4根内存条”。每个模块按照“模m”交叉编址,模块号==单元地址%m,假定有m个模块,每个模块有k个单元,则0,m,(k-1)m位于

M

0

M_{0}

M0;1,m+1,(k-1)m+1单元位于

M

2

M_{2}

M2,以此类推

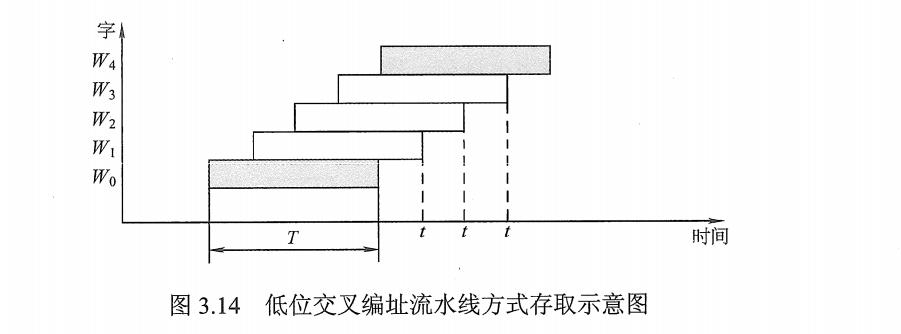

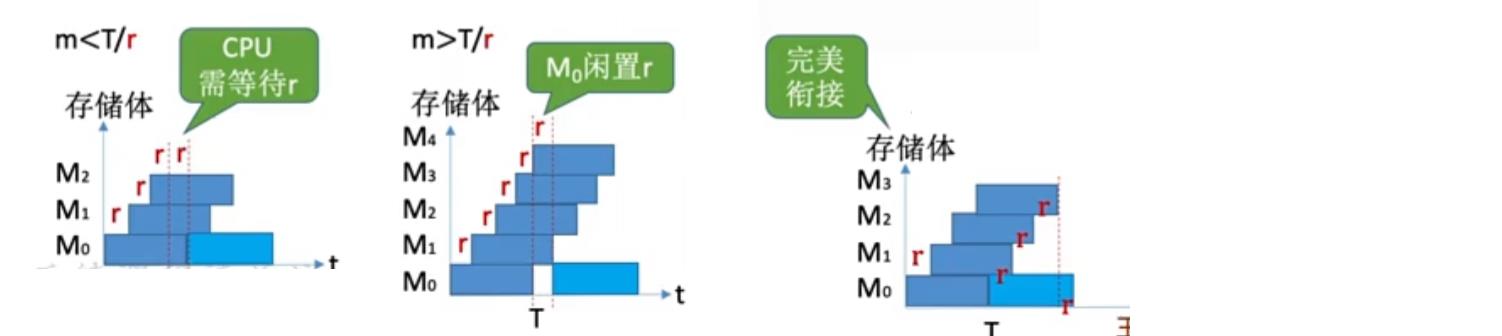

低位交叉编址方式下,总是把高位的体内地址送到由低位体号确定的模块内进行译码。程序连续存放在相邻的模块中,因此将采用此编址方式的存储器称为交叉存储器。采用低位交叉编址后,可在不改变每个模块存取周期的前提下,采用流水线的方式并行存取,提高存储器带宽

低位交叉编址方式下,总是把高位的体内地址送到由低位体号确定的模块内进行译码。程序连续存放在相邻的模块中,因此将采用此编址方式的存储器称为交叉存储器。采用低位交叉编址后,可在不改变每个模块存取周期的前提下,采用流水线的方式并行存取,提高存储器带宽

采用低位交叉编址的存储器连续读取n个存储字,耗时为T+(n-1)r。CPU每经过时间r后会启动下一模块,因此交叉存储器要求其模块数必须大于等于T/r,以保证启动某模块后经过T时间后再次启动该模块时,其上次的存取周期已到(也就是已经恢复)

多模块存储器实际有两类,一类就是我们上面讲到的多体并行存储器,另一类则是单体多字存储器。简单理解就像是上面的四个内存条合并组装到了一起,整体只有一套存储系统,一套控制电路

单体多字系统的特点是存储器中只有一个存储字,每个存储单元存储m个字,总线宽度也为m个字,一次并行读出m个字,地址必须顺序排列并处于同一个存储单元。

单体多字系统在一个存取周期内,从同一地址取出m条指令,然后将指令逐条发送至CPU执行,即每隔1/m存取周期,CPU向主存取一条质量。

显然这种方式增大了存储器的带宽,提高了单体的工作速度,但缺点就是指令和数据在主存内必须是连续存放的,一旦遇到转移指令或操作数不能连续存放

以上是关于(计算机组成原理)第三章存储系统-第五节1:双端口RAM和多模块存储器的主要内容,如果未能解决你的问题,请参考以下文章