基于32单片机的16通道ADC的数据采集

Posted 皇甫春云

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了基于32单片机的16通道ADC的数据采集相关的知识,希望对你有一定的参考价值。

基于32单片机的16通道ADC的数据采集

这个部分的内容,是作为外部模拟量部分的采集工作,按照任务要求,所设计的方案,需要完成以下指标:

- ADC必须能采集16通道的模拟量

- ADC的分辨率是16bit

- 采样率不小于20khz

由此分析可以得出,完成这个任务,对于H7系的MCU而言,性能 是绰绰有余的,可以保证上述指标的完美实现,但奈何手头的这个H7板子是借来的,所有只能花短暂的时间进行这个H7的ADC模块的调试。而长远考虑是要将数据的采集放在F4上来完成,所以这里提出了两种MCU类型的ADC多通道的数据采集方案的对比设计。

对于F4而言:

必须选择使用规则组的形式,进行多通道的模拟量采集,但是采集的精度只有12bit的分辨率,分辨率越高,则每个通道转换所需要的时间就越长。对于实验设计而言,需要先完成三个通道的数据正确采集后,再扩展更多通道的数据采集。即分为分辨率扩展和通道数目的扩展两个部分完成。

-

ADC 主要特性

这是F4的芯片手册的介绍

● 可配置 12 位、10 位、8 位或 6 位分辨率

● 在转换结束、注入转换结束以及发生模拟看门狗或溢出事件时产生中断

● 单次和连续转换模式

● 用于自动将通道 0 转换为通道“n”的扫描模式

● 数据对齐以保持内置数据一致性

● 可独立设置各通道采样时间

● 外部触发器选项,可为规则转换和注入转换配置极性

● 不连续采样模式

● 双重/三重模式(具有 2 个或更多 ADC 的器件提供)

● 双重/三重 ADC 模式下可配置的 DMA 数据存储

● 双重/三重交替模式下可配置的转换间延迟

● ADC 转换类型(参见数据手册)

● ADC 电源要求:全速运行时为 2.4 V 到 3.6 V,慢速运行时为 1.8 V

● ADC 输入范围:VREF- <VIN < VREF+

● 规则通道转换期间可产生 DMA 请求

通过阅读正点原子的开发教程和官方的芯片手册,按照任务指标的要求和自己开发的习惯上的考虑,我总结出了这些需要注意的问题:

- F4内置的ADC的多通道模拟量数据采集中规则组的通道数最多是16个

- 采集的分辨率最大是12bit

- ADC1和ADC2均可

- 触发方式是硬件边沿触发或者软件的逐次触发均可,用来启动ADC的转换

- 扫描模式适用于多通道,单通道禁用

- 连续转换,可以在启动ADC转换后,自动完成多次的数据采集

- 初始化时的规则序列的长度这个参数指的是规则组中的通道数

- ADC完成一组转换后,可以触发外部事件,形成中断等。

- ADC的最大工作频率是36MHz

- 单通道的数据转换时间是 Tconv= 采样时间 + 12个周期

- 12bit的分辨率,故转换后的数值是3.3/2^12=3.3/4096=0.0008056640625

- 此时钟来自于经可编程预分频器分频的 APB2 时钟

- 如果转换过程足够慢,则可使用软件来处理转换序列。在这种情况下,必须将 ADC_CR2 寄 存器中的 EOCS 位置 1,才能使 EOC 状态位在每次转换结束时置 1,而不仅是在序列结束 时置 1。当 EOCS = 1 时,会自动使能溢出检测。因此,每当转换结束时,EOC 都会置 1,并且可以读取ADC_DR 寄存器。溢出管理与使用 DMA 时的管理相同。

- 当转换的通道数目过多时,需要借助DMA来及时转移采集完成的数据,保证数据连续快速的采集。

对于H7而言:

也必须采用规则通道的形式进行模拟量的采集,它的分辨率支持16bit,规则组最多也只能是16通道。

- ADC的特性

- 高性能特性

– 多达 2 个 ADC,可在双重模式下运行

– 可配置 16 位、14 位、12 位、10 位或 8 位分辨率

– ADC 转换时间与 AHB 总线时钟频率无关

– 可通过降低分辨率来缩短转换时间

– 可管理单端输入或差分输入(可按通道进行编程)

– AHB 从总线接口,可实现快速数据处理

– 自校准(偏移校准和线性度校准)

– 可独立设置各通道采样时间

– 多达四条注入通道(对常规通道或注入通道的模拟输入分配完全可配置)

– 硬件辅助准备注入通道的上下文,从而实现快速上下文切换

– 数据对齐以保持内置数据一致性

– 数据可由 GP-DMA 管理,基于 FIFO 实现常规通道转换

– 数据可连接到 DFSDM 进行后期处理

– 4 个专用数据寄存器供注入通道使用 - 可通过以下方式启动转换过程:

– 通过软件启动常规转换和注入转换

– 通过极性可配置的硬件触发器(内部定时器事件或 GPIO 输入事件)启动常规转换

和注入转换 - 转换模式

– 每个 ADC 均可转换单条通道,也可扫描一系列通道

– 单次模式会在每次触发时对选定的输入执行一次转换

– 连续模式可连续转换选定的输入

– 不连续采样模式

- 高性能特性

因为H7的性能是要高于F4的ADC的,所以在寄存器的初始化上也就要比F4要复杂一点;而且使用的是HAL库,开发上也要比最开始的标准库函数要更简洁和容易。现总结如下:

- 分辨率是16bit

- 每个ADC的20个通道中分为4个快速通道,16个慢速通道

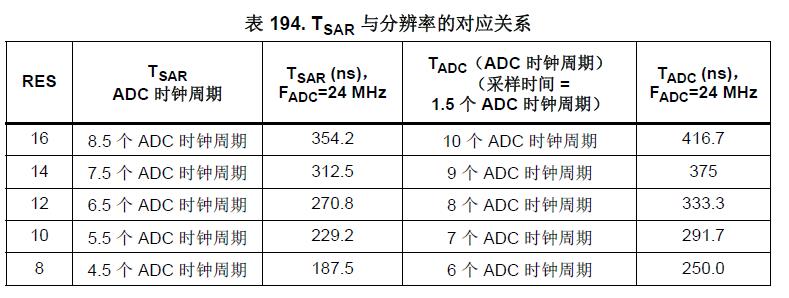

- 分辨率不同对应的通道的转换时间不同

ADC的转换时序图:

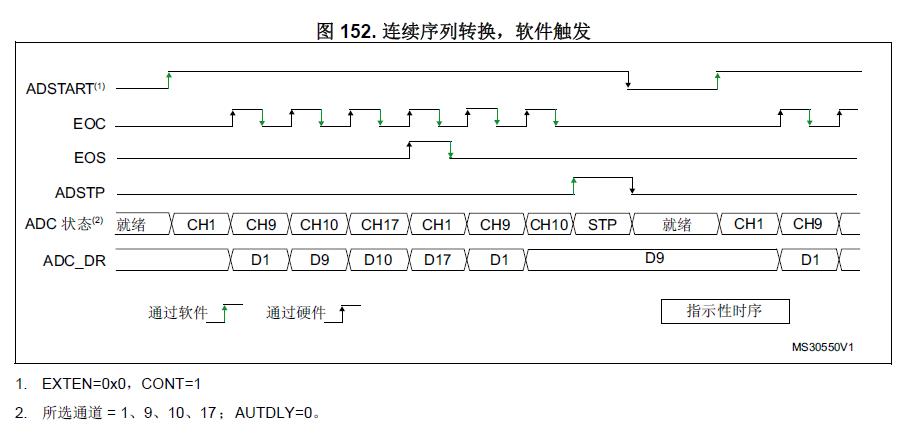

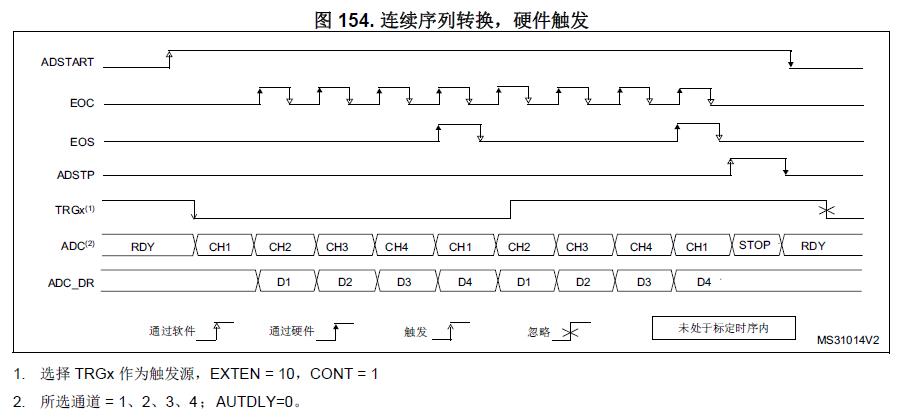

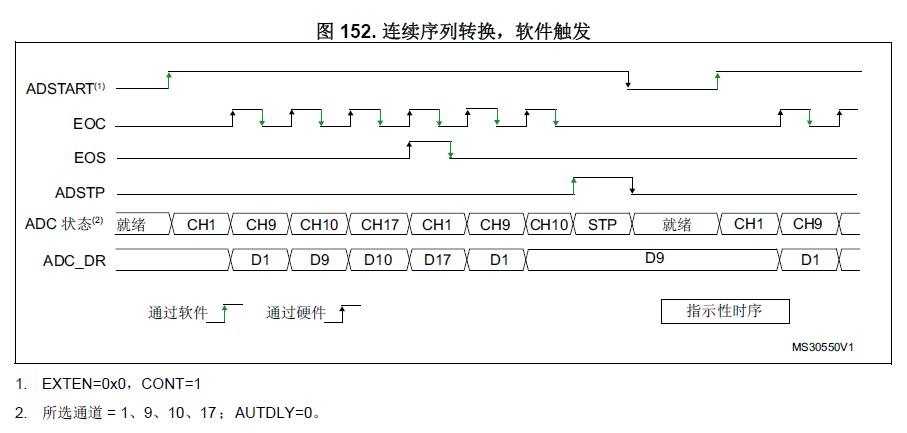

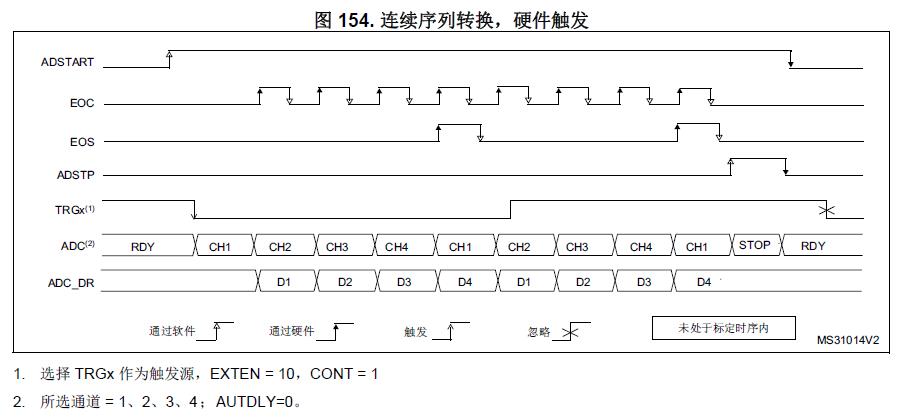

经过查阅相关的数据手册,可以发现,对于多通道的数据采集,采用连续序列转换,转换效率会更高,而STM32又提供了硬件和软件两种触发方式,分别如下图所示:

针对这两种方式,需要仔细的品味其时序转换之间的关系,才能将ADC转换利用好,遂下面是详细的分析过程:

ADSTART和ADSTP是整个ADC运行过程中的使能使能信号,用来启动和停止ADC的运行;而EOC和EOS是转换指示信号,用来指示每个通道和每个序列转换是否完成;而ADC状态是当前ADC运行到哪一步了;最后是ADC_DR是数据寄存器,用来存放转换完成后的数据。

故通过软件使能ADC后,立刻开始转换,当EOC拉高后,证明当前的一个通道转换完成,可以借助软件启动第二次转换了。当EOS拉高后,说明当前的一个序列已经转换完成了。通过拉高ADSTP可以停止当前序列的转换,前提是必须等待到该序列的最后一个通道转换完成后,才可以拉高。

通过对比分析,可以发现和软件触发基本一致,只是多了一个TRGx信号,借助硬件边沿信号来启动ADC的转换。图中设置的是下降沿触发ADC。

首先借助软件初始化,使能ADC,即拉高ADCSTART信号,只有当ADSTP拉高时,才会失能ADC这个外设,停止一切通道的数据转换。EOC和EOS同上,用来指示当前通道和当前序列是否抓换完成。而在使能ADC后,只有TRGx的触发信号有效时,才会启动ADC序列的转换,转换完成后的数据被存储到 32 位 ADC_DR 寄存器中。故转换后,需要将数据及时的读出到缓存中,以防数据被覆盖。

在不使用 DMA 的情况下管理转换序列:

如果转换过程足够慢,则可使用软件来处理转换序列。在这种情况下,软件必须使用 EOC 标 志及其相关中断来处理各个数据。每当转换结束时,EOC 都会置 1,并且可以读取 ADCx_DR 寄存器。OVRMOD 应配置为 0,以便将溢出事件作为错误进行管理。

在使用 DMA 的情况下管理转换序列:

由于转换得出的通道值会存储到唯一的数据寄存器中,因此,对于多个通道的转换,使用DMA 非常有帮助。这样可以避免丢失在下一次写入之前还未被读出的 ADCx_DR 寄存器中 的数据。

使用DMA来完成转换后数据的传送和存储

使用 DMA 管理转换

由于转换得出的通道值会存储到唯一的数据寄存器中,因此,对于多个通道的转换,使用DMA 非常有帮助。这样可以避免丢失在下一次写入之前还未被读出的 ADCx_DR 寄存器中 的数据。

DMA 模式使能时(单 ADC 模式下 ADCx_CFGR 寄存器中的 DMNGT 位 = 01 或 11,或者 双重 ADC 模式下 MDMA 不为 0b00),会在每次通道转换后生成 DMA 请求。这样便可将转 换的数据从 ADCx_DR 寄存器传输到用软件选择的目标位置。

尽管如此,如果因 DMA 无法及时处理 DMA 传输请求而发生溢出 (OVR=1),ADC 会停止生 成 DMA 请求,新转换对应的数据不会通过 DMA 进行传输。这意味着可将传输到 RAM 的所 有数据都视为有效数据。

根据 OVRMOD 位的配置,可保留或覆盖数据。

DMA 传输请求会禁止,直至软件将 OVR 位清零。

根据应用用途的不同,推荐使用两种不同的 DMA 模式(在单 ADC 模式下,使用 ADCx_CFGR 寄存器中的 DMNGT 位配置;在双重 ADC 模式下,使用 ADCx_CCR 寄存器中的 DAMDF 位配置):

DMA 单次模式(DMNGT 位 = 01)。

如果通过编程将 DMA 设置为传输固定数目的数据,应选择此模式。

DMA 循环模式(DMNGT 位 = 11)

如果在循环模式下对 DMA 进行编程,应选择此模式。

DMA 单次模式 (DMNGT=01)

在该模式下,每次出现新的转换数据时,ADC 都会生成 DMA 传输请求,DMA 到达最后一 个 DMA 传输操作时(发生 DMA_EOT 中断,请参见 DMA 一段),即使转换已再次开始, ADC 也会停止生成 DMA 请求。

DMA 传输完成后(在 DMA 控制器中配置的所有传输操作均已完成后):

ADC 数据寄存器的内容会冻结。

~ 任何正在进行的转换都会中止,其部分结果会被丢弃。

~ 不会将任何新的 DMA 请求发送到 DMA 控制器。如果仍存在已开始的转换,这样可避

免生成溢出错误。

~ 扫描序列会停止并复位。

~ DMA 会停止。

DMA 循环模式 (DMNGT=11)

在该模式下,每次数据寄存器中出现新的转换数据时,ADC 都会生成 DMA 传输请求,即使 DMA 已到达最后一次 DMA 传输操作也不例外。这样可将处于循环模式的 DMA 配置为处理 连续的模拟输入数据流。

以上是关于基于32单片机的16通道ADC的数据采集的主要内容,如果未能解决你的问题,请参考以下文章