(计算机组成原理)第三章存储系统-第三节1:SRAM和DRAM芯片以及DRAM的属性和地址线复用技术

Posted 快乐江湖

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了(计算机组成原理)第三章存储系统-第三节1:SRAM和DRAM芯片以及DRAM的属性和地址线复用技术相关的知识,希望对你有一定的参考价值。

文章目录

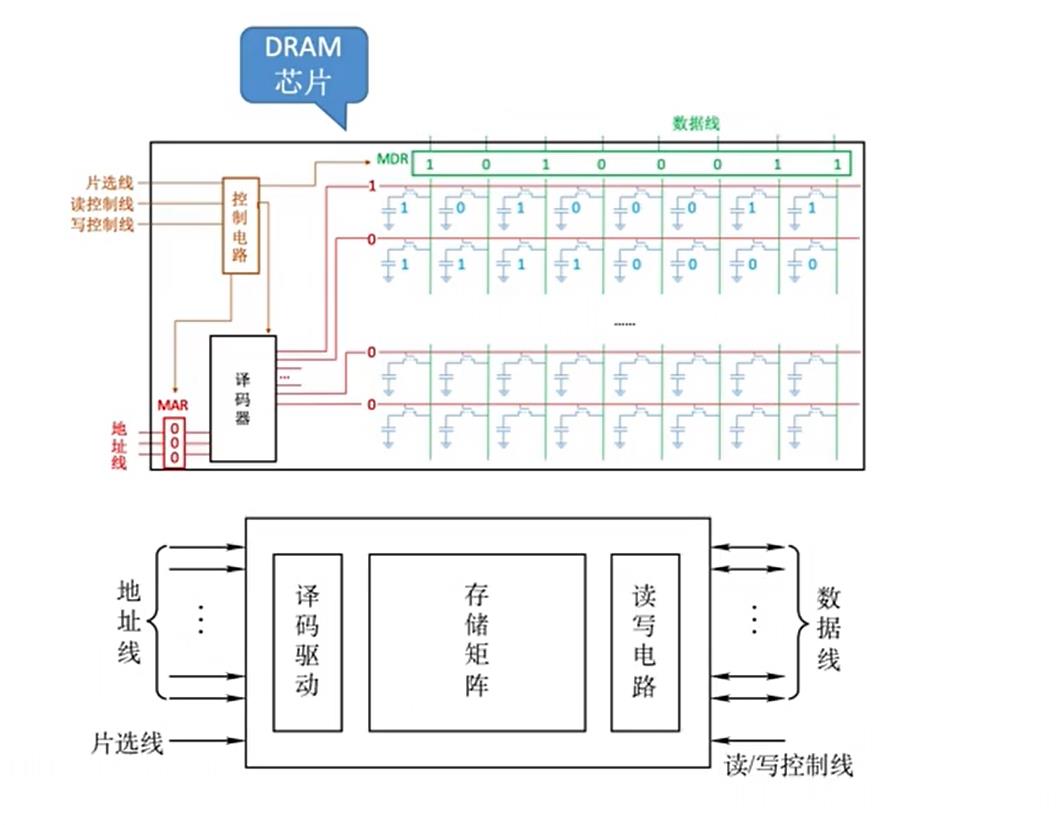

上一节我们简单介绍了半导体基本原理,明白了存储器的核心就是存储芯片,这一节我们主要介绍两种重要的存储器芯片:DRAM和SRAM

- DRAM( D y n a m i c − R a n d o m − A c c e s s − M e m o r − Dynamic-Random- Access -Memor- Dynamic−Random−Access−Memor−):动态DRAM,用于主存

- SRAM(Static- Random -Access -Memory):静态RAM,主要用于Cache

注意:DRAM芯片已经过时了,现在主存通常采用SDRAM(如DDR3和DDR4)

一:存储器元件不同导致的特性差异

上一节我们介绍的芯片实则就是DRAM芯片,也就是被用于制作主存

其实DRAM芯片和SRAM芯片的核心区别点就在于他们的存储元不一样

- DRAM:使用栅极电容

- SRAM:使用双稳态触发器

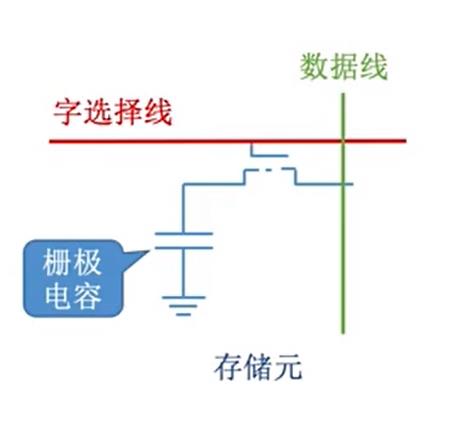

(1)栅极电容

关于栅极电容如何读写信息,其实前面我们已经大致谈过了。具体来说,就是当给字选择线一高电平时,MOS管接通,然后给数据线一高电平,由于电容一端接地,因此电容板之间产生电压差,于是电荷被“写入”进入电容,因此

- 1:表示电容内存储了电荷

- 2:表示电容内未存储电荷

在读出时,如果电容里面有电荷,那么当MOS管接通后,一定会在数据线位置检测到电流信号,反之则不会,分别对应数据1和数据0

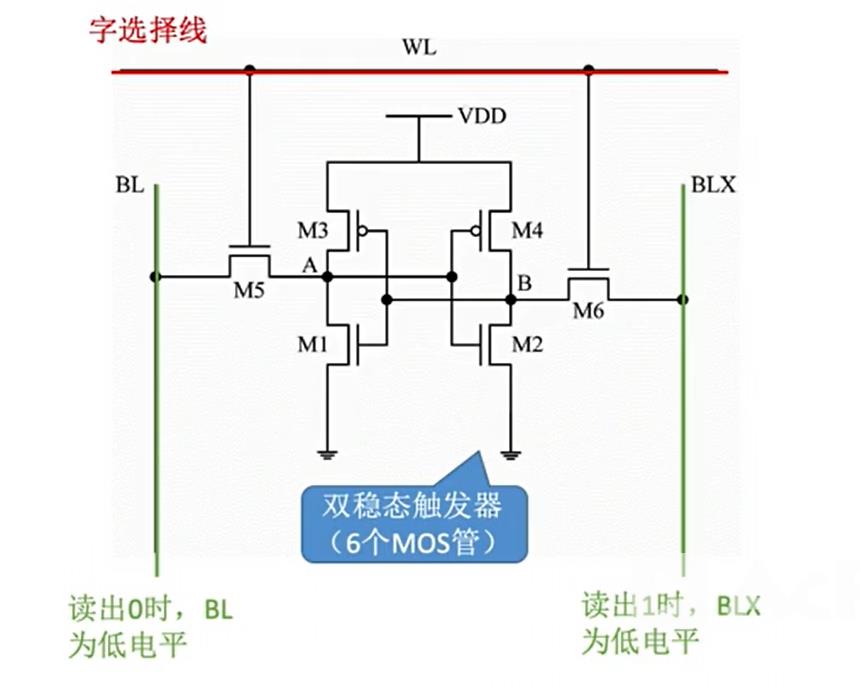

(2)双稳态触发器

双稳态触发器(点击了解更多)是一种具有记忆功能的逻辑单元电路,它能储存一位二进制码。它有两个稳定的工作状态,在外加信号触发下电路可从一种稳定的工作状态转换到另一种稳定的工作状态。

如下,它的两种稳定状态可以分别对应1和0

- 1:A高B低

- 0:A低B高

双稳态触发器相比栅极电容来说,它有两根数据线

当给字选择线一高电平信号后,如果里面存储的是1,那么将会在BLX这条线上输出低电平信号(左边没有);如果存储的是0,那么将会在BL这条线上输出低电平信号(右边没有)

如果要写入数据0,那么只需要给BL一低电平信号,同时给BLX一高电平信号;如果要写入数据1,那么只需要给BL一高电平信号,同时给BLX一低电平信号

(3)区别

1:关于读写速度

- DRAM使用栅极电容的充放电来完成读写操作,那么电容的物理特性就决定了其充放电是一种破坏性读出,读出后应该有重写操作,也就是需要重新充电,也称之为再生,读写速度较慢

- SRAM使用双稳态触发器,在读写数据时,触发器的状态是保持稳定的,因此属于非破坏性读出,无序进行重写操作,读写速度也就更快

2:关于成本和功耗

- DRAM:单个存储元制造成本低,集成度高,功耗低

- SRAM:单个存储元制造成本更高,集成度低,功耗大

3:其它区别

| 类型/特点 | SRAM(静态RAM) | DRAM(动态RAM) |

|---|---|---|

| 存储原理 | 触发器 | 电容 |

| 是否是破坏性读出 | 否 | 是 |

| 是否需要重写 | 否 | 是 |

| 运行速度 | 快 | 慢 |

| 集成度 | 低 | 高 |

| 发热量 | 大 | 小 |

| 成本 | 高 | 低 |

| 是否是易失性存储器 | 是 | 是 |

| 是否需要“刷新” | 是 | 否 |

| 送行列地址 | 同时送 | 分两次 |

| 用途 | Cache | 主存 |

- 刷新:电容里面的电荷不能永久存在,一般只能维持2ms,因此即使不断电,2ms后信息也会丢失,因此对于DRAM需要“刷新”,也就是再充电;而SRAM只要不断电,触发器的状态就不会改变

二:DRAM的刷新

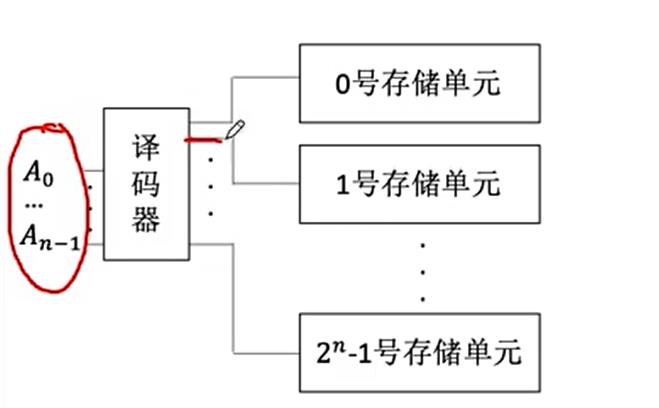

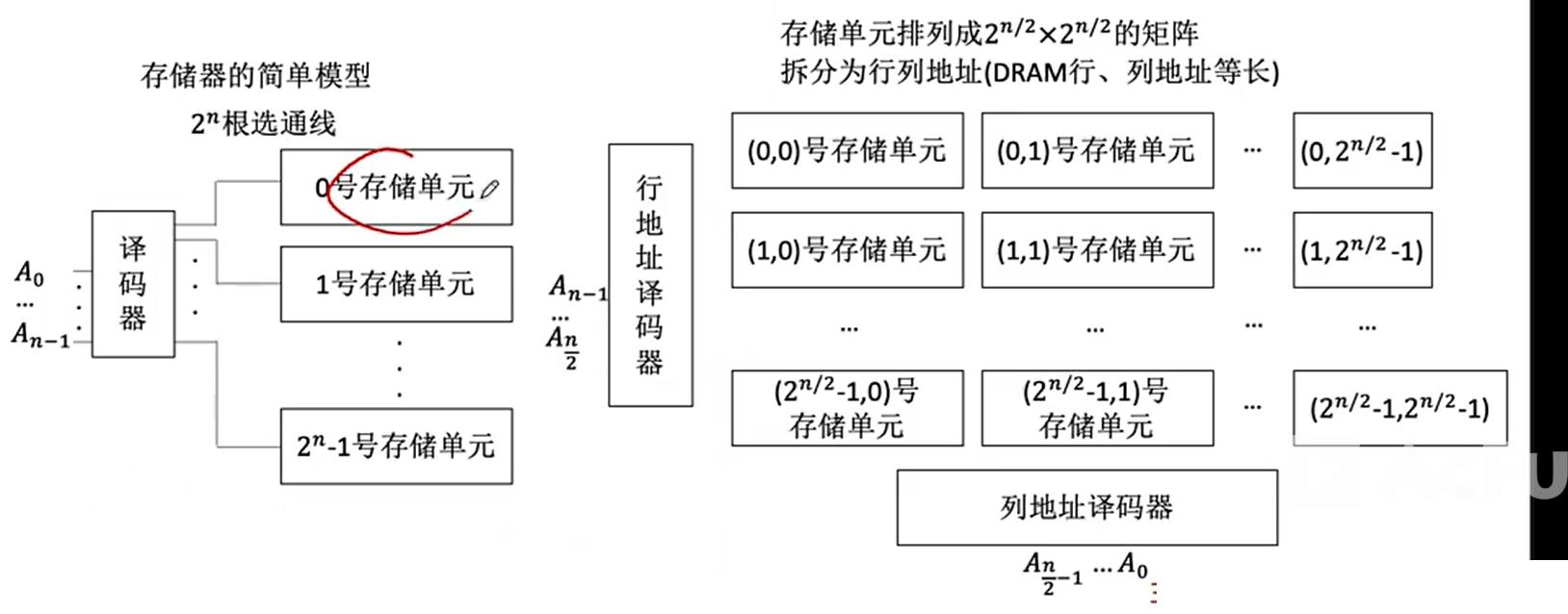

(1)译码器需要使用行列地址

上一节我们再讲原理的时候就说过,译码器的作用就是把某位的地址,转化为相应的选通线的高电平信号, n n n位地址就对应 2 n 2^{n} 2n个地址。

这个数量级其实相当大,即使只有20个地址,就要对应

2

2

0

=

1048576

2^20=1 048 576

220=1048576根选通线,接近百万,因此工程难度极大。

解决方法就是:将原来的单纯的一维的地址,改变为行列地址,也就是一个矩阵,分别交给行地址译码器和列地址译码器管理,这样的话每个译码器只需处理一半的地址信息,也就是1024根选通线,这样的话难度就大大降低了。

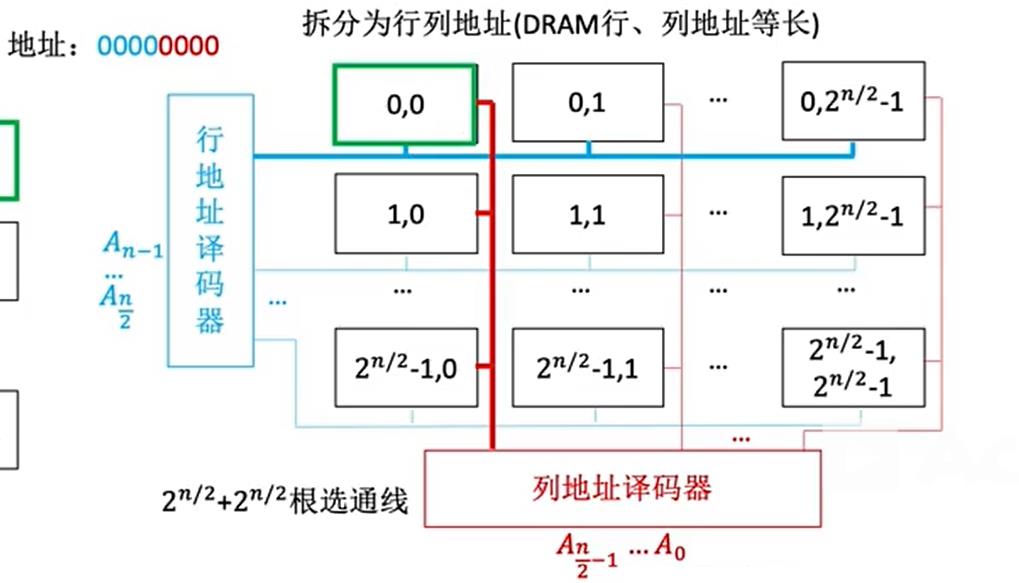

以地址0000 0000为例,如果采用之前的方案,那么经过译码器后,第0根选通线会被选中。

而如果采用矩阵的方案,地址0000 0000的低四位将会交给列地址译码器,高四位将会交给行地址译码器,每个存储单元只有列选通线和行选通线同时被选中时才能被选中,因此(1,1)位置的存储单元此时被选中

因此对于八位地址,原本需要使用

2

8

=

256

2^{8}=256

28=256根选通线就会被降低为

2

4

+

2

4

=

16

+

16

=

32

2^{4}+2^{4}=16+16=32

24+24=16+16=32根选通线了,所以使用行列地址的本质就是要减少选通线数量

(2)如何刷新

- 多久刷新一次:一般为2ms

- 每次刷新多少存储单元:以行为单位,每次刷新一行存储单元

- 如何刷新:有硬件支持,读出一行的信息后重新写入,占用1个读写周期

- 什么时候刷新:分散刷新、集中刷新和异步刷新(见下)

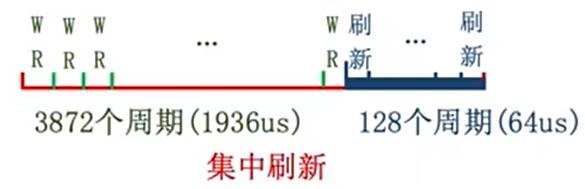

假设DRAM内部结构排列形式为128×128,存储周期为0.5 u s us us,电容最多坚持2ms,因此对应2ms/0.5 u s us us=4000个周期,因此有128行,刷新每一行都需要0.5 u s us us,共两种思路

(3)分散刷新、集中刷新和异步刷新

-

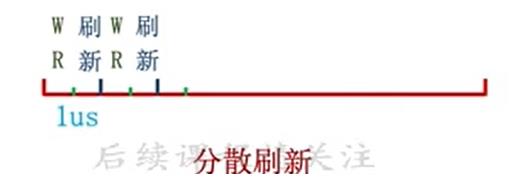

分散刷新:把对每行的刷新分散到各个工作周期当中,这样,一个存储器的系统工作周期就分为了两个部分,前半部分用于正常读写或保持;后半部分用于刷新某一行。这种刷新方式增加了系统的存取周期,增加为1 u s us us

-

集中刷新:是指利用一段固定的时间,依次对存储器的所有行进行逐一再生,存储周期不变,在刷新期间内会停止对存储器的访问,因此称之为“死时间”,又称访存“死区”

-

异步刷新:它是前两种刷新方式的结合。具体做法是将刷新周期除以行数,得到两次刷新操作之间的时间间隔t(2ms/128=15.6 u s us us),接着利用逻辑电路每隔该时间间隔t(15.6 u s us us)产生一次刷新请求,因此每15.6 u s us us内会有0.5 u s us us的死时间。所以死时间会分散在整个过程中,而且可以在译码阶段刷新

集中刷新优点是读写操作不受刷新工作的影响,因此系统的存取速度较高;缺点是在集中刷新期间(死区)不能访问存储器

分散刷新优点是没有死区;缺点是加长了系统的存取周期降低了整体速度

异步刷新可以避免使CPU连续等待过长的时间,而且减少了刷新次数,从根本上上提高了整机的工作效率;同时如果将刷新安排在不需要访问存储器的译码阶段,则既不会加长存取周期,又不会产生“死时间”,这是分散刷新的方式的发展,也称之为“透明刷新”

关于刷新还需要注意以下问题

- 刷新对CPU是透明的,也即刷新不依赖于外部的访问

- RAM刷新单位是行,因此刷新操作时仅需要行地址

- 刷新操作类似于读操作,但又有所不同-刷新操作仅给栅极电容补充电荷,不需要信息输出,另外刷新时不需要进行选片,即整个存储器中的所有芯片同时被刷新

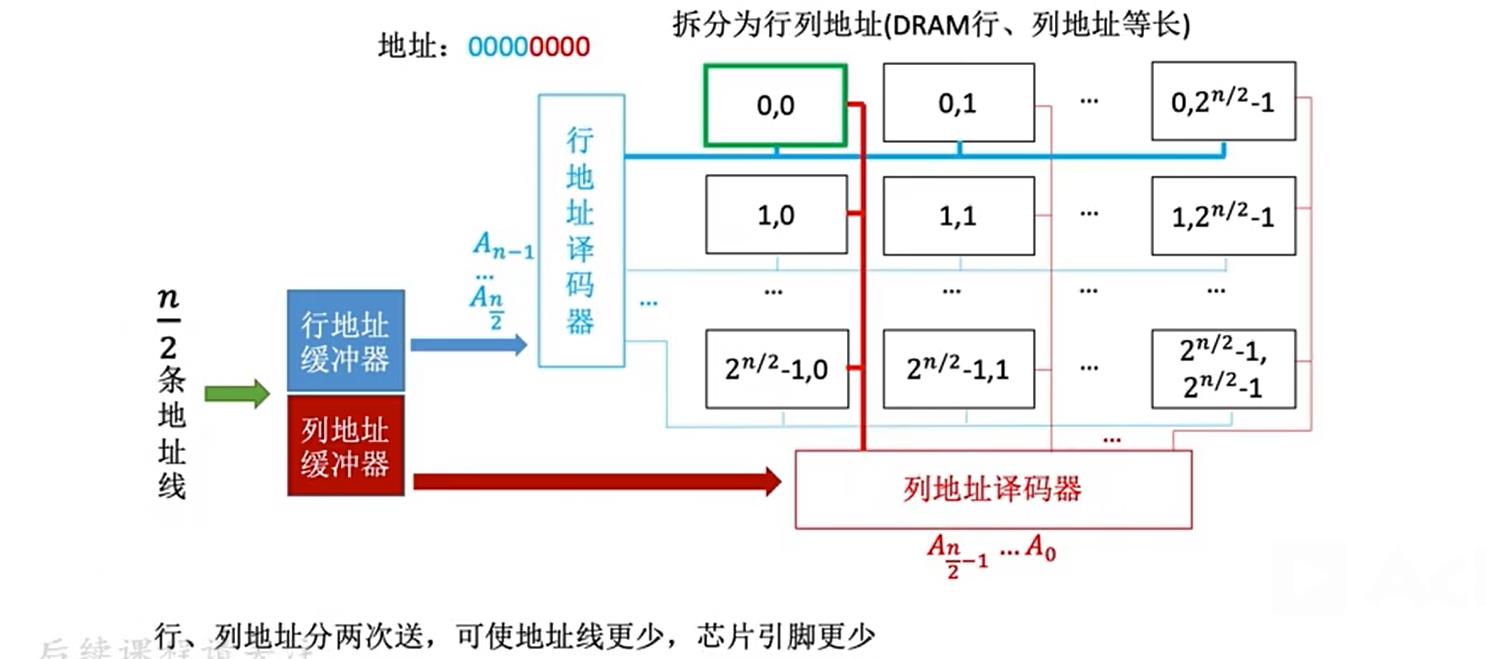

三:DRAM的地址线复用技术

前面说过SRAM需要同时送行列地址,而DRAM需要分两次

- 同时送:行列地址信息会同时丢给行译码器和列译码器

采用这种方式就有意味着地址线有多少位就要设计多少根地址线。DRAM由于用于主存,因此容量可能较大,因此地址线可能会更多,所以为了使地址线电路变得更简单,会采用一种地址线的复用技术,也就是分两次送

这种技术可以使行列地址分两次前后进行传送,传送时只需要一半地址,先传送至缓冲区,再传送给译码器即可,这样会使得地址线更少,相应引脚变少

以上是关于(计算机组成原理)第三章存储系统-第三节1:SRAM和DRAM芯片以及DRAM的属性和地址线复用技术的主要内容,如果未能解决你的问题,请参考以下文章