计算机组成与体系结构期末题目解析

Posted 宝山的博客

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了计算机组成与体系结构期末题目解析相关的知识,希望对你有一定的参考价值。

计算机组成与系统结构期末备考

复习题目分析

-

前言

hello,大家好,最近由于面临期末,已经快半个月没更新了。因为明天就要考计组了,所以,今天我就和大家一起分享下计算机组成的期末复习大题,内容涉及的基本是课后习题。最后也祝福大家顺利渡劫。

特此声明:以下题目均来自课本和学习通题目。经过自己多次复习,简化出每一章节具有代表性的题目。

-

1.假定某编译器对某段高级语言程序编译生成两种不同的指令序列S1和S2,在时钟频率为500MHz的机器M上运行,目标指令序列中用到的指令类型有A、B、C和D四类。四类指令在M上的CPI和两个指令序列所用的各类指令条数如下表所

A B C D 各指令的CPI 1 2 3 4 S1的指令条数 5 2 2 1 S2的指令条数 1 1 1 5 请问:S1和S2各有多少条指令?CPI各为多少?所含的时钟周期数各为多少?执行时间各为多少?

(注:从上述结果来看,对于同一个高级语言源程序,在同一台机器上所生成的目标程序不同,其执行时间可能不同,而且,并不是指令条数少的目标程序执行时间就一定少。)解析:此题目主要需要掌握几个公式: 1.程序总时钟周期数=CPI*指令条数 2.CPU的执行时间=时钟周期数/时钟频率(或*时钟周期--就是频率的倒数) s1指令的条数有:5+2+2+1=10条 S1的平均cpi=时钟周期数/指令条数 =(5*1+2*2+2*3+1*4)/10 =1.9 S1所含时钟周期数=CPI*指令条数=1.9*10=19 S1的执行时间=时钟周期数/时钟频率 =19/500MHz =38ns 注意:M=10^6。 同样,S2也是这样计算。这里就不在赘述了

-

2.有如下C语言程序:

#include <stdio.h> union test{ float x; int y; }z; void main(){ z.y=0x C0A0 0000 printf("%f",z.x); } -

假定z.y 采用IEEE754 单精度浮点数格式表示,变量z在内存中存放的地址为0000 A001H, z 中的成员 均采用小端存储方式,按字节编制,回答下列问题。

-

(1) 程序输出的结果是什么(采用十进制表示)?描述完整的计算与分析过程

-

(2)地址为 0000A004H 的字节单元中存放的内容是什么?(用十六进制表示)

解析:当我们第一次看到这个题目时,或许不知道怎么做,其实仔细阅读后,就是让我们做IEEE754的逆运算。这里我会采用4步,写出答案: 1.将16进制数,转2进制。 COAO 0000 = 1 100 0000 1 010 0000 0000 0000 0000 0000 2.求出指数阶码 e=E-127 E=128+1=129 e=129-127=2= 0000 0010 从符号为S可以看出 答案为负数。 3.求包含隐藏位1的尾数1.M 所以M=(1.01)2 4.X=(-1)^s*1.M*2^e =-1.01*2^2 =-101.0 =-5.0 程序输出的结果是 -5.0 ------ 关于第二问,主要考察我们队大端、小端的理解,这里我说下我的记忆方法:(C0A0 0000H) 大端:就是从左向右写,c0 a0 00 00 小端,就是从右往左写。00 00 a0 c0 所以根据题目,我们列出表格如下: 0000 A001 00 0000 A002 00 0000 A003 A0 0000 A004 C0 发现 0000A004H 存放的是 c0

-

3.假设要传送的数据信息为:100011,若约定的生成多项式为:G(x)= x3+1,则校验码为多少?假定在接收端接收到的数据信息为100010,说明如何正确检测其错误,写出检测过程。

解析:关于CRC校验,这里只需要细心,基本都不会出错。这里我说下我的解题步骤: 1) 求CRC校验码: 1.展开多项式,写出除数 G(x)= x3+1 =1*x^3+0*x^2+0*x^1+1*x^0 =1001 2.原数据末端加0(添加最高次项 数个0),此题3个0 原数据=100011,加3个0得: 100011 000 3.从左往右,一次进行亦或运算。得出余数 100 111 ---------- 1001 100011 000 1001 --------- 111 0 100 1 ----------- 111 0 100 1 --------- 11 10 10 01 ------ 1 11 余数111 所以,CRC校验码是:100011 111 2) 检测时, 用接收到的CRC码去模2除生成多项式1001,若得到的余数为0,则表明正确,否则说明传输时发生了错误。此题中接收到的CRC码为100010 111(即数据100010加检验位111),显然,用100010 111 模2除 1001,得到余数为001,不为0,说明传输时发生错误。

- 4假设某信息码为:0100 1101,请按偶校验原则求其海明码

-

6.假设某计算机字长32位,CPU有32个32位的通用寄存器,指令长度为单字长,指令操作码占6位。请回答以下问题,注意写出分析过程:

-

(1)对于存储器直接寻址方式的RS型指令,能直接寻址的最大主存空间是多少?

-

(2)对于采用通用寄存器作为基址寄存器的RS型指令,则能直接寻址的最大主存空间是多少?

解析:关于指令系统的话,我觉得很可能考教材115页,例题4-1。那道题能搞懂就搞懂,搞不懂就寄一个公式。 K0=[(2^4-K2)*2^6-K1]*2^6 如果看不懂,可以qq或博客私信我 如果考察这个题目的话,考试很可能变下数字,所以我们需要搞清楚指令的基本格式即可算出。 分析:计算机字长 32位,说明一共32位。32位的通用寄存器,说明有5位寄存器编号,同时还指明了操作码占6位 所以 块内地址占 32-5-6=21位,- 能直接寻址的最大主存空间是2^21 --- 第二问,他说采用通用寄存器 基址寻址的R-S型指令的一个操作数在寄存器中,另外一个操作数在基址寻址的内存单元中,因为采用通用寄存器作为基址寄存器,所以必须在指令中明显指出基址寄存器是哪个通用寄存器,所以基址寄存器的编号占5位,剩下的位数(32 – 6 - 5 – 5 = 16位)是位移量。通用寄存器的位数是32位,所以基址寄存器中的基准地址位数是32位。一个32位的数加上一个6位的数,其结果还是一个32位的数。所以,能直接寻址的最大主存空间是2^32字。 -

-

知识点补充:

本章主要靠指令系统: 1.指令的基本格式: 操作码 地址码A1 地址码A2 地址码A3 2.零地址指令,只有操作码,不需要数据(常用的有开机、关机、重启) 一地址指令,操作码 一个地址指令。(单目运算、隐含寻址) 二地址指令,操作码 2个地址指令 三地址值指令 操作码 3个地址指令 3.指令设计 定长操作码 指令格式:操作码的长度,固定的 2^k 条不同指令 若操作码 为4位,最多只能有2^4=16条不同指令 扩展操作码指令格式: 操作码的长度可以变, 基本思想,操作码最短--->操作码最长。一般从3地址到 0地址设计 让操作码逐渐去侵占 地址码。 比如:4位到8位,到12位。 0001~1111 16个,但是只用15个。所以1111用来侵占第一个地址码A1 所以,此时操作码为:1111 1110,前面4位是不能用的,所以从后面4位用。还是 从0001~1110

-

7.假设地址为1200H的内存单元中的内容为12FCH,地址为12FCH的内存单元的内容为38B8H,而38B8H单元的内容为88F9H。说明以下各情况下操作数的有效地址和操作数各是多少?

1)操作数采用变址寻址,变址寄存器的内容为12,指令中给出的形式地址为1200H。

(2)操作数采用一次间接寻址,指令中给出的地址码为1200H。(3) 操作数采用寄存器间接寻址,指令中给出的寄存器编号为8,8号寄存器的内容为1200H。

解析: (1)有效地址EA=000CH+1200H=120CH,操作数未知。 (2)有效地址EA=(1200H)=12FCH,操作数为38B8H。 (3)有效地址EA=1200H,操作数为12FCH。

-

8.指令流水线

下面是一段指令序列:

add $t1, $s1, $s0

sub $t2, $s0, $s3

add $t1, $t1, $t2

以上指令序列中,哪一条指令发生数据相关?

假定采用"取指、译码/取数、执行、访存、写回"这种五段流水线方式,那么不用"转发"技术的话,需要在发生数据相关的指令前加入几条nop指令才能使这段程序避免数据冒险?

如果采用"转发"是否可以完全解决数据冒险?

解析:这个题目记住就好了,理解题,理解了数据冒险就好了。 因为第一条和第二条指令会更新第三条指令用到的寄存器的值,有可能导致第三条指令取操作数时得到的是更新前的数据,这样第三条指令就不能正确执行,所以第三条指令发生数据相关。 不进行“转发”的话,就只能通过在第三条指令前加nop指令来延迟第三条指令的执行。因为只有第二条指令把数据写回到$t2,第三条指令才能从$t2取到正确的值,所以,第二条指令的“回写”流水段后面是第三条指令的“译码/取数”流水段,为此,在第二和第三条指令之间必须插入三条nop指令。

-

9.用256×8位的RAM芯片扩展为1k×8位的RAM,请回答以下问题:

a. 共需要几块芯片,采用何种扩展方式?

b. 请将以下CPU与存储器的连接图补充完整。

c. 请写出各芯片的地址范围。

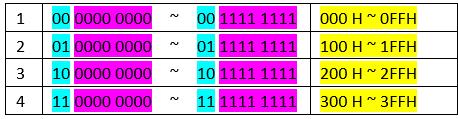

解析:需要几片芯片,如果你是在不会算,题目会给你图,让你连接线。可以直接看出几块芯片。这里我按正常算法去做题: a:共需要的芯片 =1k*8/256*8=2^2=4(片) 又256*8 和1k*8 ,都是8位,位没变,所以是字扩展 -

b 绘图题:

-

c 地址范围:

-

10.假设某计算机的主存地址空间大小为128MB,采用字节编制方式,其Cache数据区容量为4KB,采用直接相关联映射方式,块大小为 64B

(1) 主存地址字段如何划分?说明每个字段的含义,位数

(2)若只考虑每个Cache行包括1个有效位,标记字段和数据区,该Cache的总容量有多少位?

(3)假设 Cache初始为空,CPU一次从0号地址单元顺序访问到1023单元,重复访问10次。若cache命时间为 1个时钟周期,缺失时间为10个时钟周期,求CPU访存的平均时间为多少时钟周期?

解析:在我整理的8个题目里,我觉得这个题目是最难的,难于它的命中率。下面我尽量写详细它的过程及思路。 (1) 首先,他说采用直接相关映射。所以主存格式为: 标记位 行索引 块内地址 三个组成 题目说主从地址空间 128MB,那么说明它有 20+7=27位。 假如这里换成 256MB 那么它有 20+8=28位 Cache数据区容量 4KB,采用直接映射,块大小64B。所以它的行数有: 4KB/64B =2^12/2^6=64(行)。 所以,它需要2^6=64,6位做行 索引。 又因为快大小64B。块内地址占的位数为:2^6=64,块内地址占 6位。、 综上:标记 占的位数有:27-6-6=15 (2)由题意只考虑有效位,标记字段和数据区,标记字段为15bit和有效位1bit,数据阵列为64B=64*8bit,cache行有4K/64B=64,则 Cache的总容量为:64*(15+1+64*8) = 33792bit4 (3)内存0~1023单元大小为1024B,由于块大小为64B,则1024B/64B=16块,即内存0~1023单元为内存的前16块,则一共只有16次访问内存,可得命中率为: R=(1024*10-16)/(1024*10) = 1 – 16/(1024*10) cpu的平均访存时间周期ta = tc + (1-R)* tm (该公式见教材P256) ta = tc + (1-R)* tm = 1 + (16*10)/(1024*10) = 10400/10240 = 1.016时钟周期

-

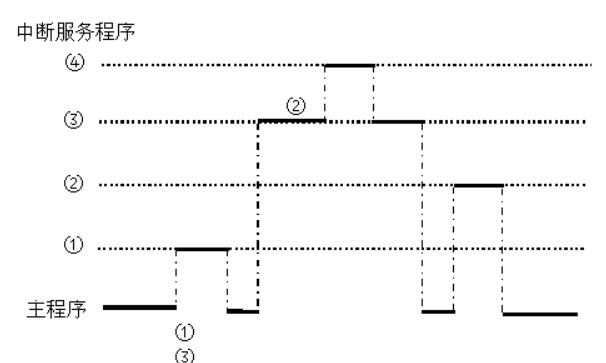

11.若某计算机有4级中断,中断响应优先级为1>2>3>4,而中断处理优先级为1>4>3>2。要求:

(1)设计各级中断处理程序的中断屏蔽位(假设1为屏蔽,0为开放);

(2)若在运行主程序时,同时出现第1、3、4中断请求,而在处理第2级中断过程中,又同时出现1、3、5级中断请求,试画出此程序运行过程示意图。

关于这个题目,要多看教材描述,相信肯定可以看懂,这个题目看懂了,就不难了。这里我截取了教材一部分题目,做个描述,尽量让你明白。 -

中断屏蔽

-

运动轨迹

对于这里,我直接写分析过程。 关于屏蔽字,首先自己屏蔽自己,其次是根据处理优先级屏蔽。前面的开放,后面的屏蔽。

温馨提示

-

考前准备

明天考试时间是上午 9:00~11:00。 考试一定要备好考试工具,当做高考就行 需要准备的有: 1.准考证 2.身份证 3.学生证 4.B+B铅笔 5.黑色中性笔 6.最好带上尺子,涉及画图

总结

ok!如果你看到这篇文章,请不要快速划过,它会让你期末不挂科。如果题目中有不会的可以私信我。我们一起讨论.大家也可以根据自己情况复习,我挑的是个人觉得重点,不一定会考

最近我已经把计算机网络复习的整理出来了,需要的伙伴,点个赞,关注下,考前会发布哦!

以上是关于计算机组成与体系结构期末题目解析的主要内容,如果未能解决你的问题,请参考以下文章