开源示波器Scopefun介绍原理图学习

Posted qlexcel

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了开源示波器Scopefun介绍原理图学习相关的知识,希望对你有一定的参考价值。

介绍

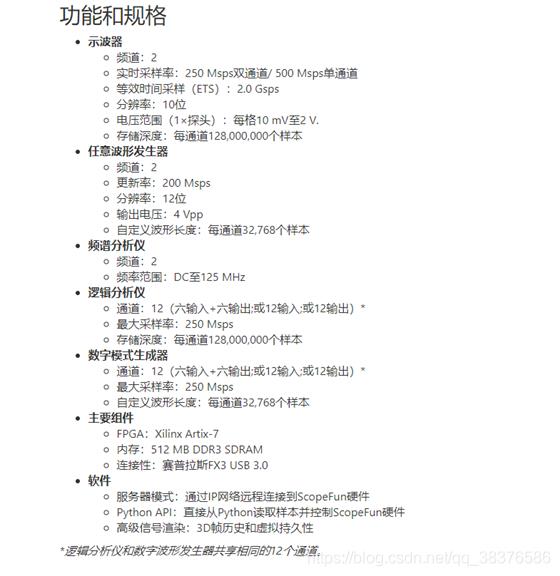

Scopefun是网上开源的示波器,他的功能和规格如下:

-

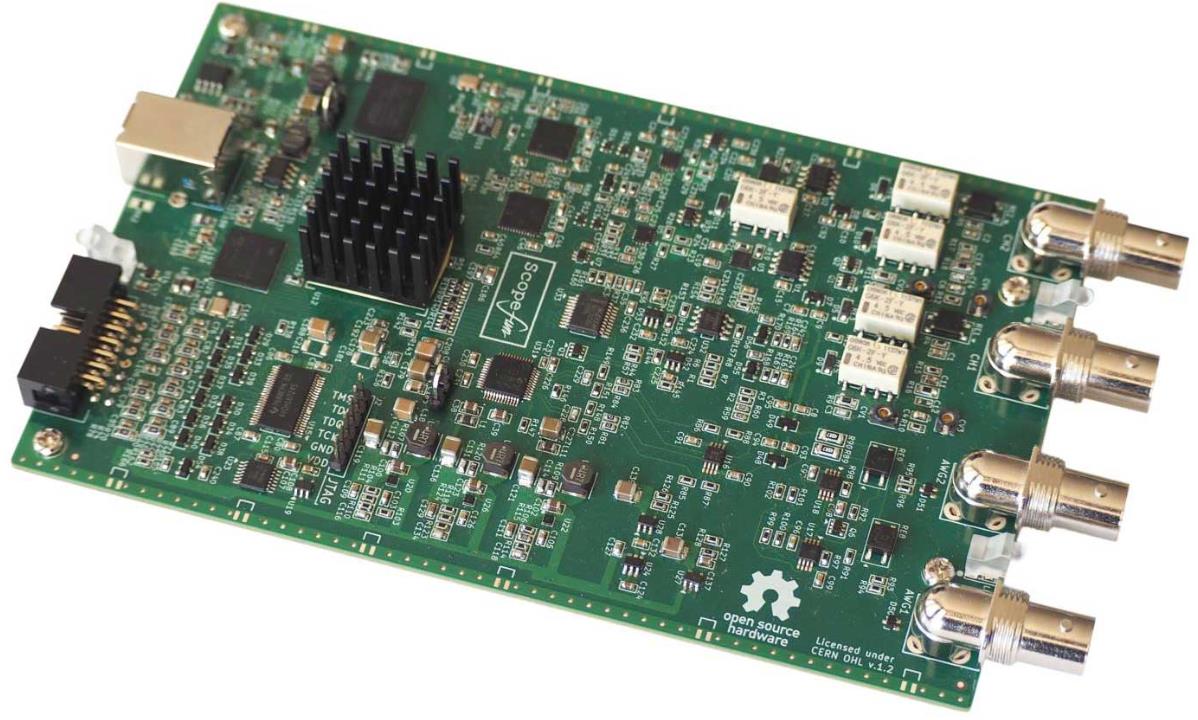

固件、软件、硬件都可以在gitlab上下载:https://gitlab.com/scopefun,PCB需要使用开源的画图软件kicad打开。

-

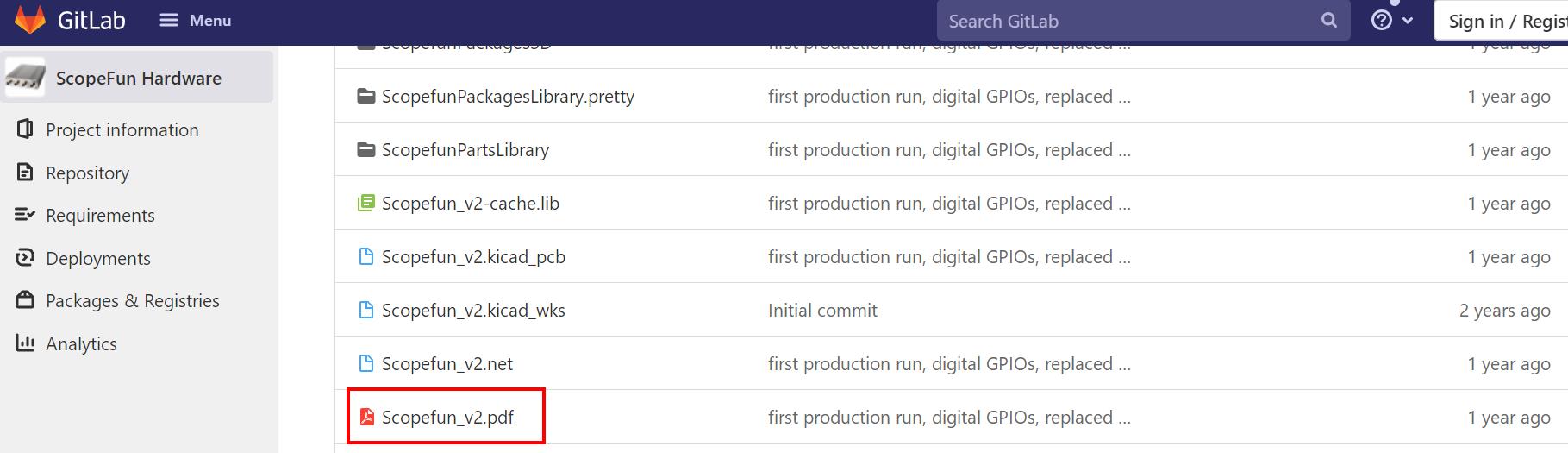

原理图的PDF,在这里下载,推荐下载下来然后再跟着我后面的讲解来一起学习。

-

因为此示波器是通过USB把数据传到PC进行显示,因此还有个配套的上位机。可以在如下地址下载:https://link.csdn.net/?target=https%3A%2F%2Fwww.scopefun.com%2Fdownload

原理图学习

接下来学习下此示波器的原理图。

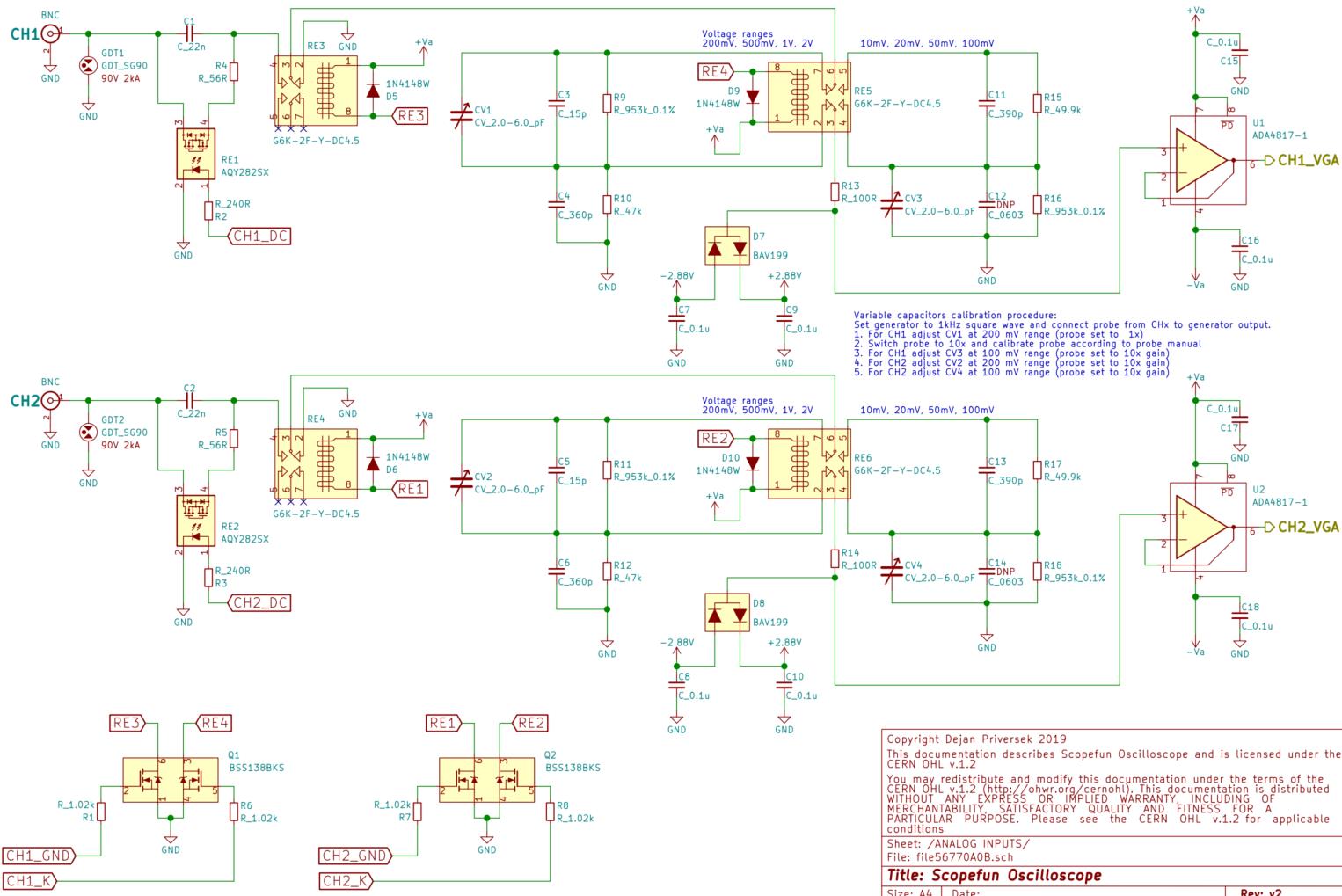

模拟信号输入接口

- 通道输入有防雷管保护

- 通过松下的光电固态继电器AQY282SX控制直流耦合或交流耦合。

- 通过电磁继电器RE3控制接地或信号输入。

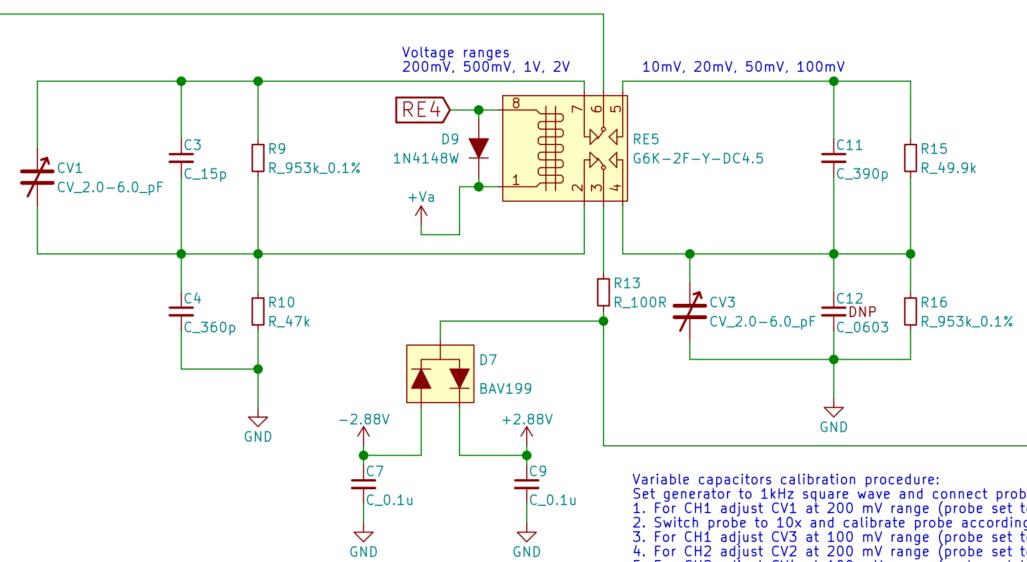

- 当RE5的6、7触点和2、3触点接触,输入信号从RE5的6脚进,7脚出,流过R9、R10分压(总阻值1M),分压后信号从2脚进,3脚出。对应大于等于200mV的量程。

- 当RE5的5、6触点和3、4触点接触,输入信号从RE5的6脚进,5脚出,流过R15、R16分压,分压后信号从4脚进,3脚出。对应小于200mV的量程。

- 最后信号流入ADA4817构成的电压跟随器,从CH1_VGA出。

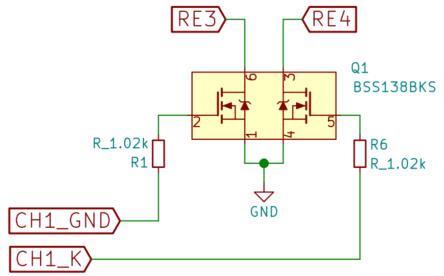

- 通过NMOS来驱动电磁继电器。

信号增益反馈处理

- CH1_VGA流入AD8337,AD8337是压控增益放大器,通过CH1_GAIN的输入电压值来控制CH1_VGA到VOUT的电压放大倍数。

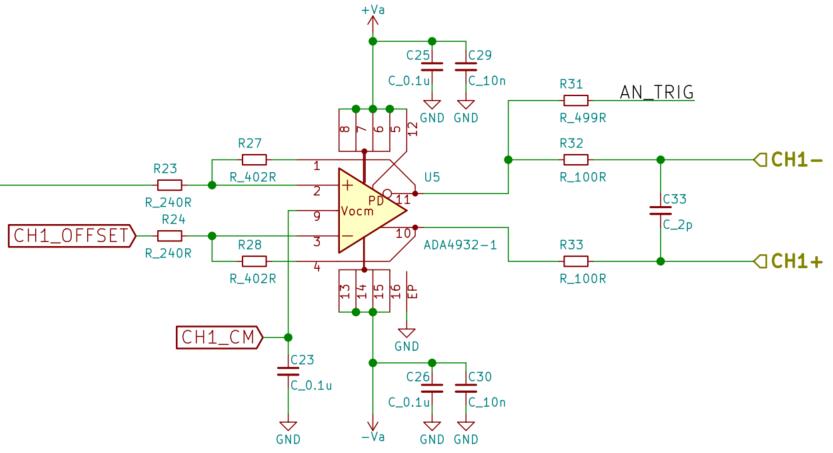

- 信号继续流入ADA4932,ADA4932是单端转差分放大器,把输入转成差分信号,然后再输入ADC。输出差分信号的负端还引出了AN_TRIG信号,用做触发信号,触发通道采样。

- AN_TRIG信号和FPGA输出的模拟信号AN_TRIG_LEVEL一起送入LTC6754,LTC6754是高速比较器,输入信号值和FPGA设置的触发参考值做比较,如果满足触发条件就触发采样。

- 左下角的RE7,当触点6、7接触,CH1_VGA会被同时送入两个ADC进行采样。当触点5、6接触,CH1_VGA被送入ADC1,CH2_VGA被送入ADC2。

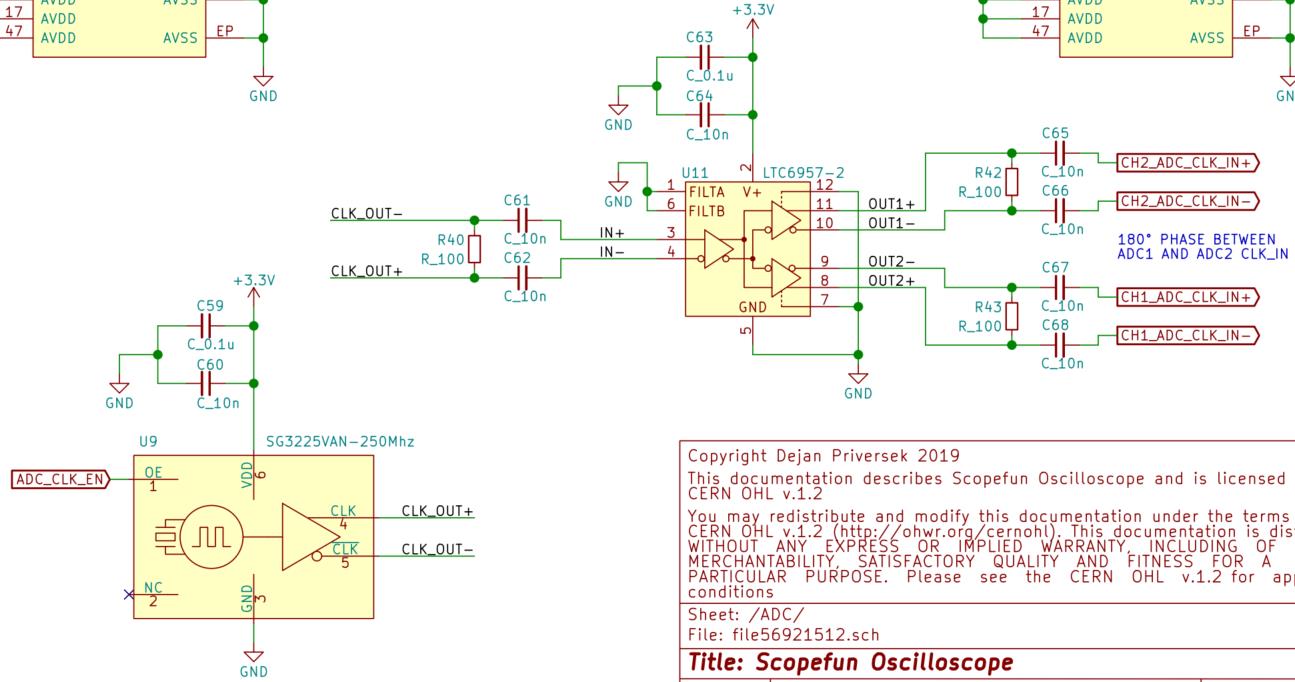

ADC模块

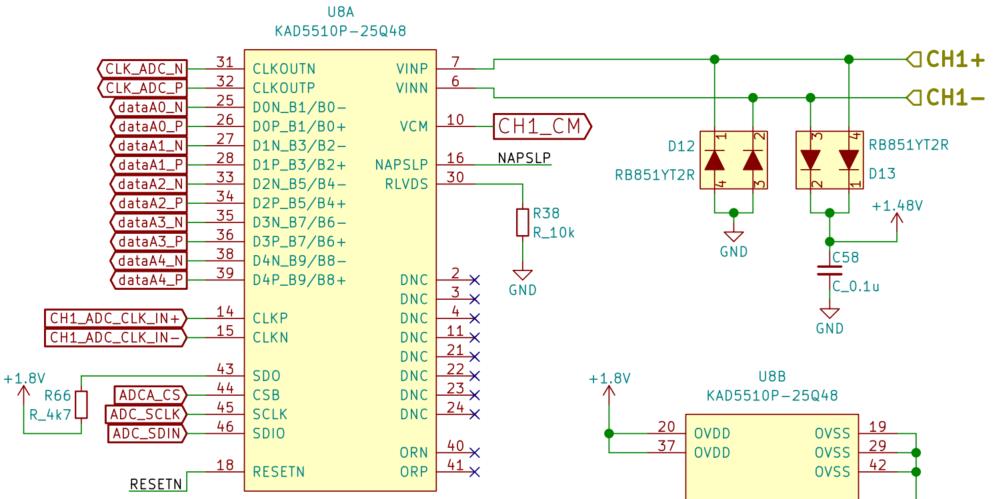

- 前面产生的差分信号送入KAD5510P,KAD5510P是250M的ADC。

- 这里是两个通道ADC的时钟电路,有源晶振SG3225VAN产生250MHz的频率,然后送入LTC6957分成两路,再分别供给两个ADC,这样可以保证两个通道的采样是同步的。

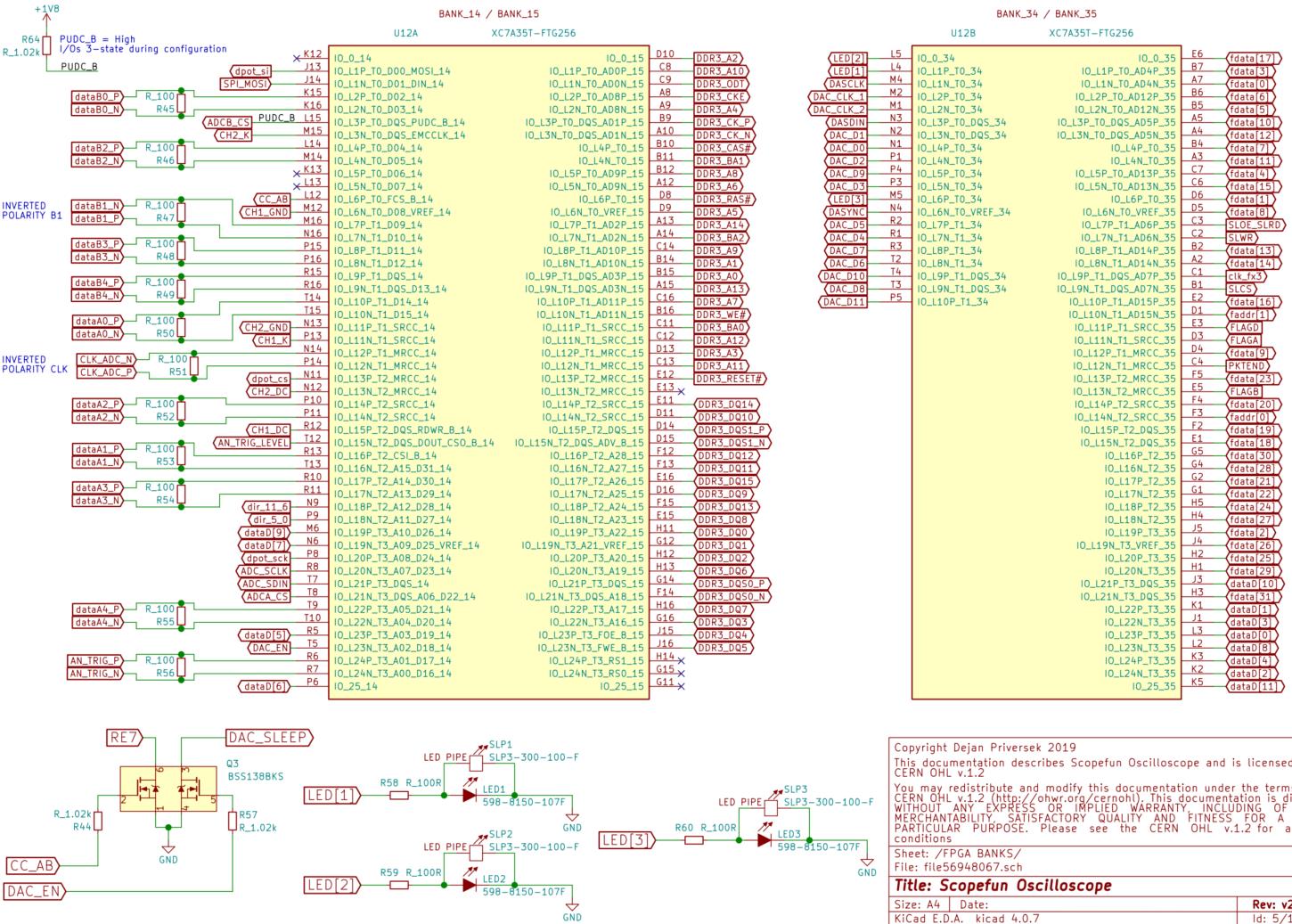

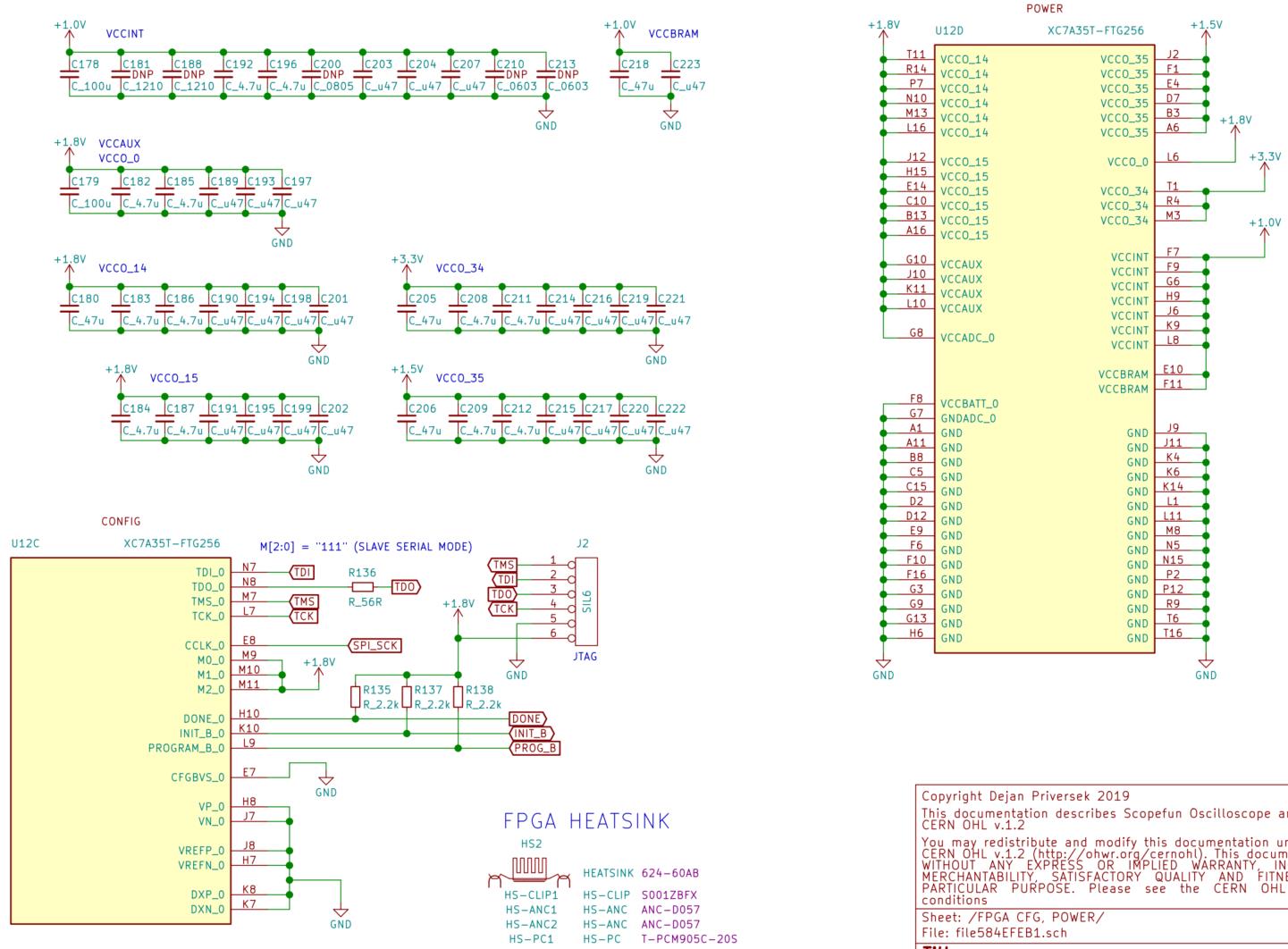

FPGA 模块

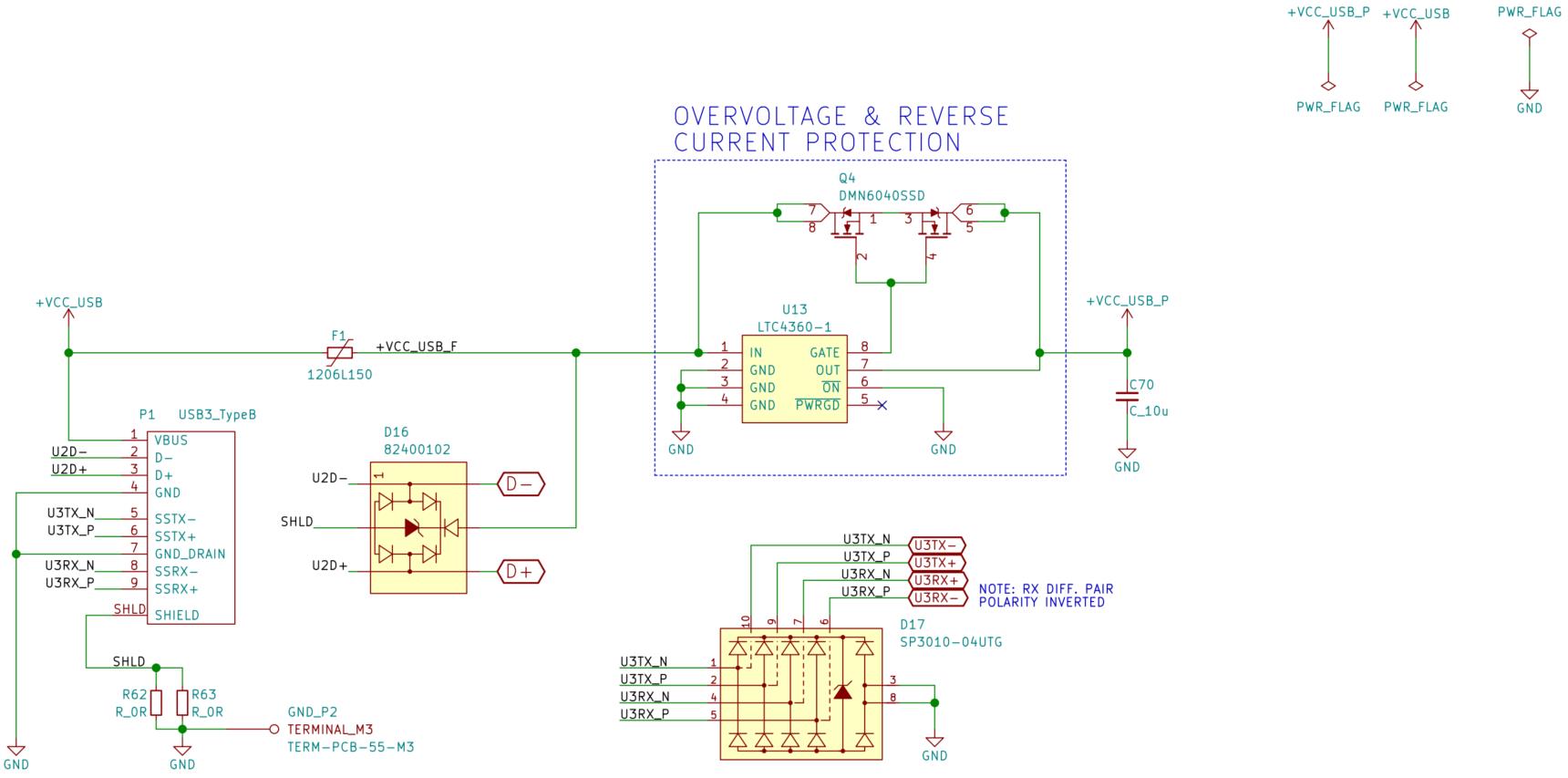

USB接口部分

- USB3.0协议,type-B接口,输入经过保险丝F1,TVS阵列芯片82400102,再输入LTC4360,LTC4360具有过压、反接保护。

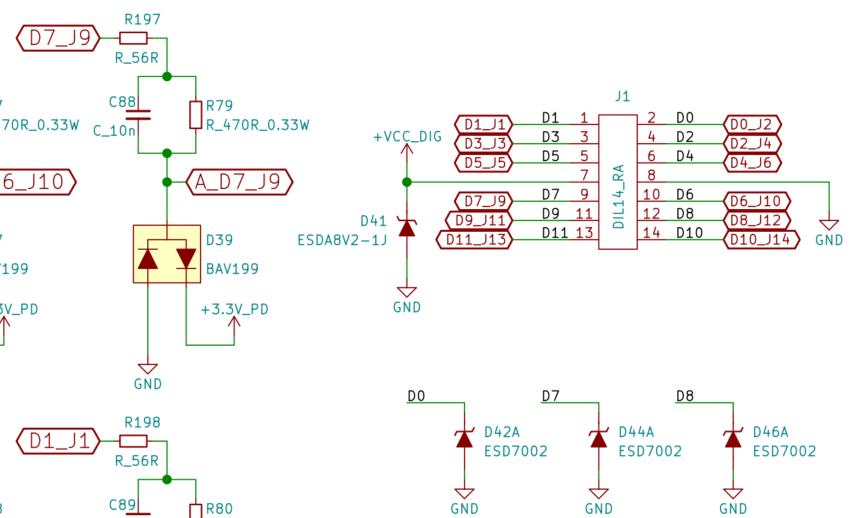

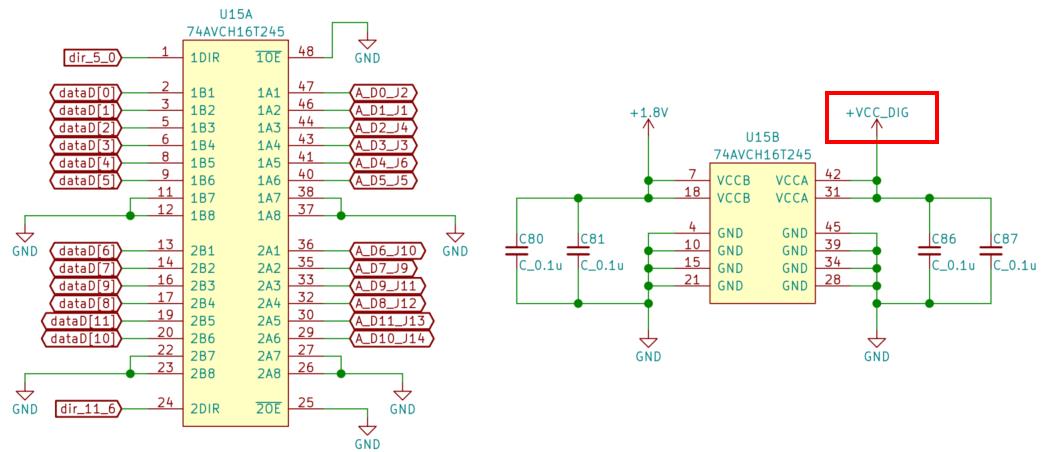

数字输入接口

这里是逻辑分析仪信号输入的处理电路部分。

- J1是外部信号输入接口,D0信号进来首先经过ESD7002,然后经过56R、470R的电阻,再经过BAV199进行电压限幅,最后流入缓冲器74AVCH16T245。信号经过74AVCH16T245后再输入FPGA。245主要起到保护FPGA的IO口的目的。

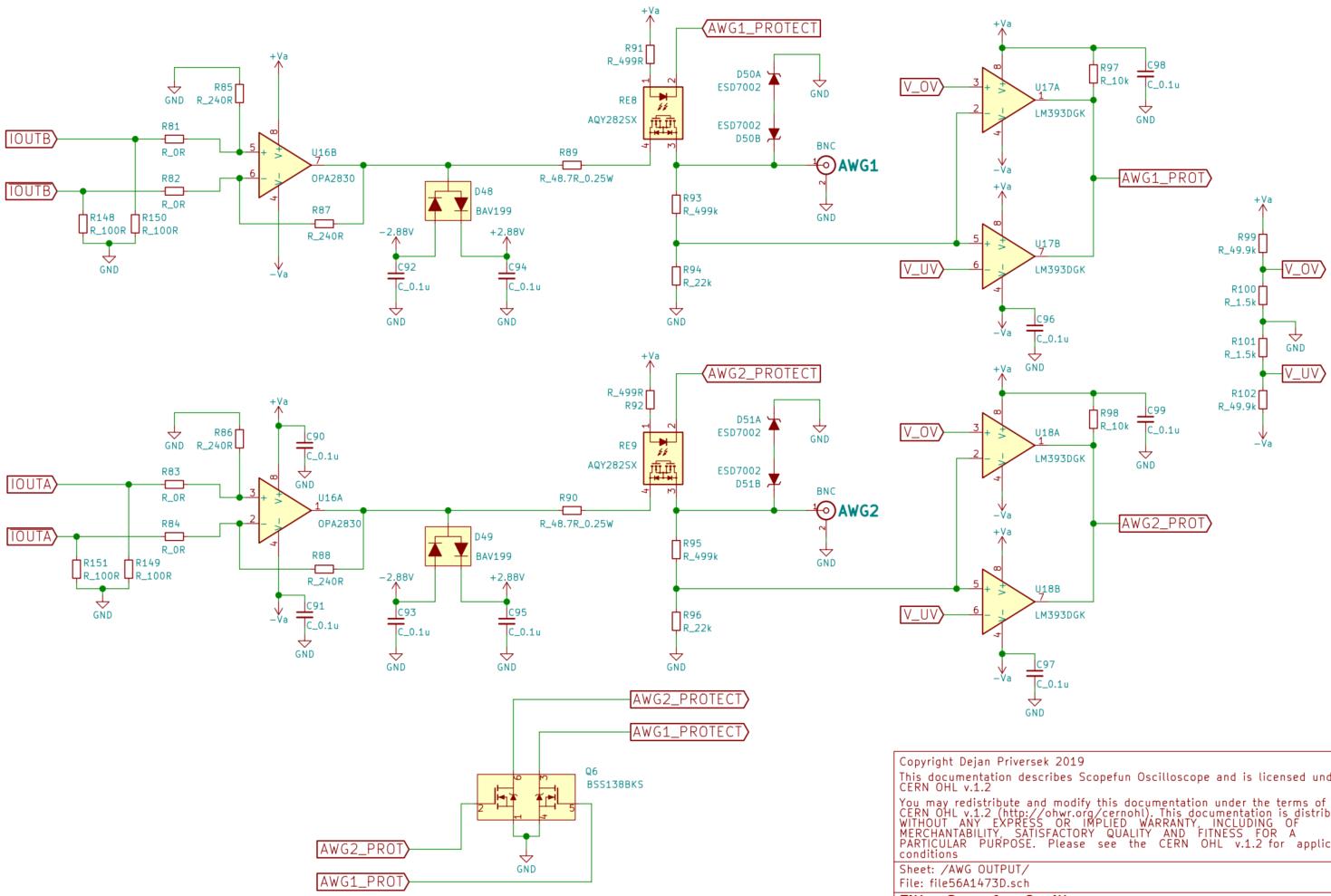

信号发生器输出电路

- DAC的输出信号进入运放OPA2830,信号经过BAV199限幅,再经过光耦继电器控制输出与否。

- 输出电压经过499K、22K分压,送入两个LM393电压比较器进行电压的上下限值比较。

系统电源

- 使用USB输入的5V产生+Va(+3.71V)、+3.3V、+1.8V、+1.5V、+1.2V、+1V、-Va(-3.71V)。

- 通过LDO SPX3819配合数字电位器MCP4251输出可变电压给逻辑分析仪输入口的245使用,以适配输入信号的不同电平值。

USB3.0芯片

FPGA的电源、JTAG部分

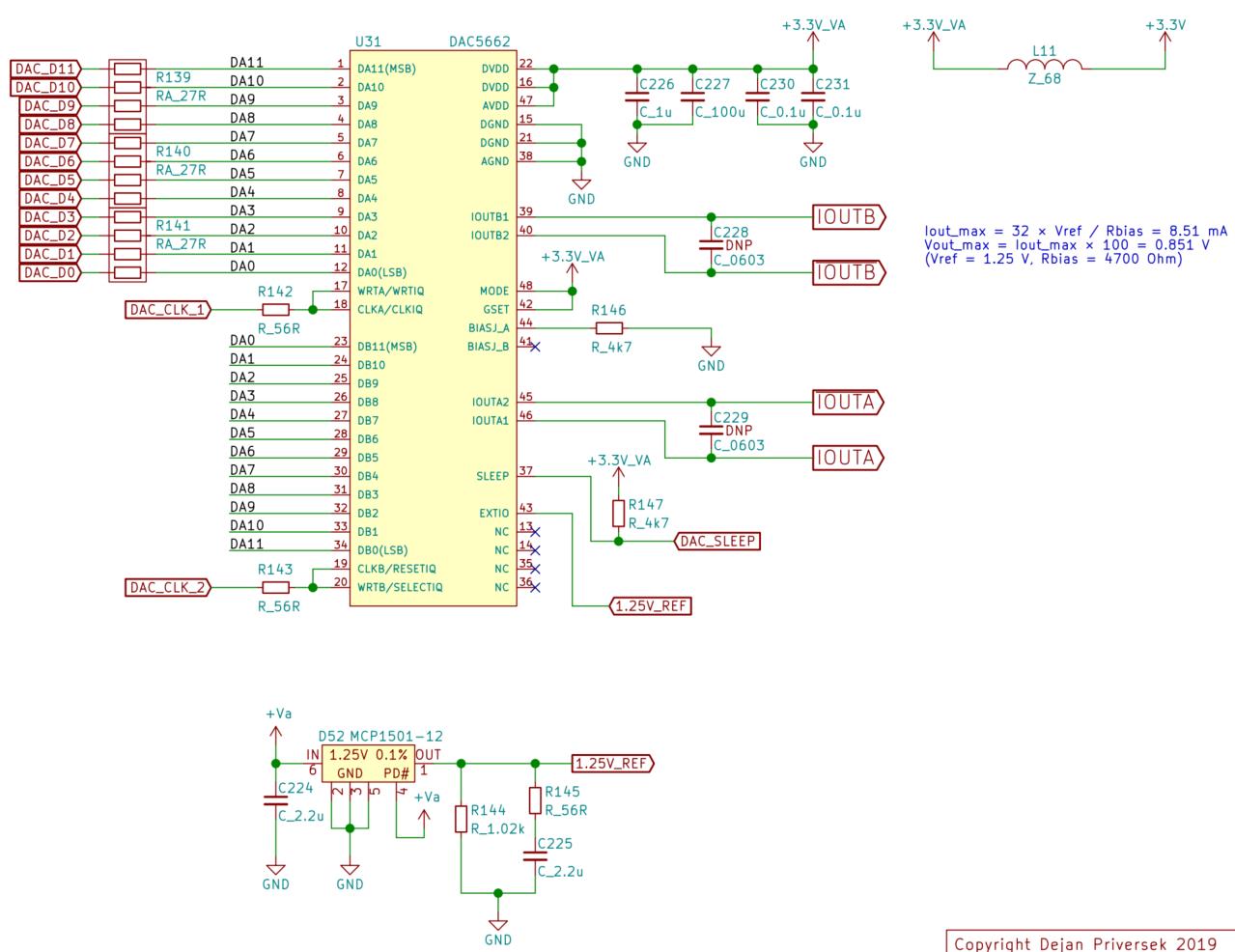

逻辑分析仪的DAC电路

- 信号发生器使用了DAC5662。

DAC控制电路

参考电压基准

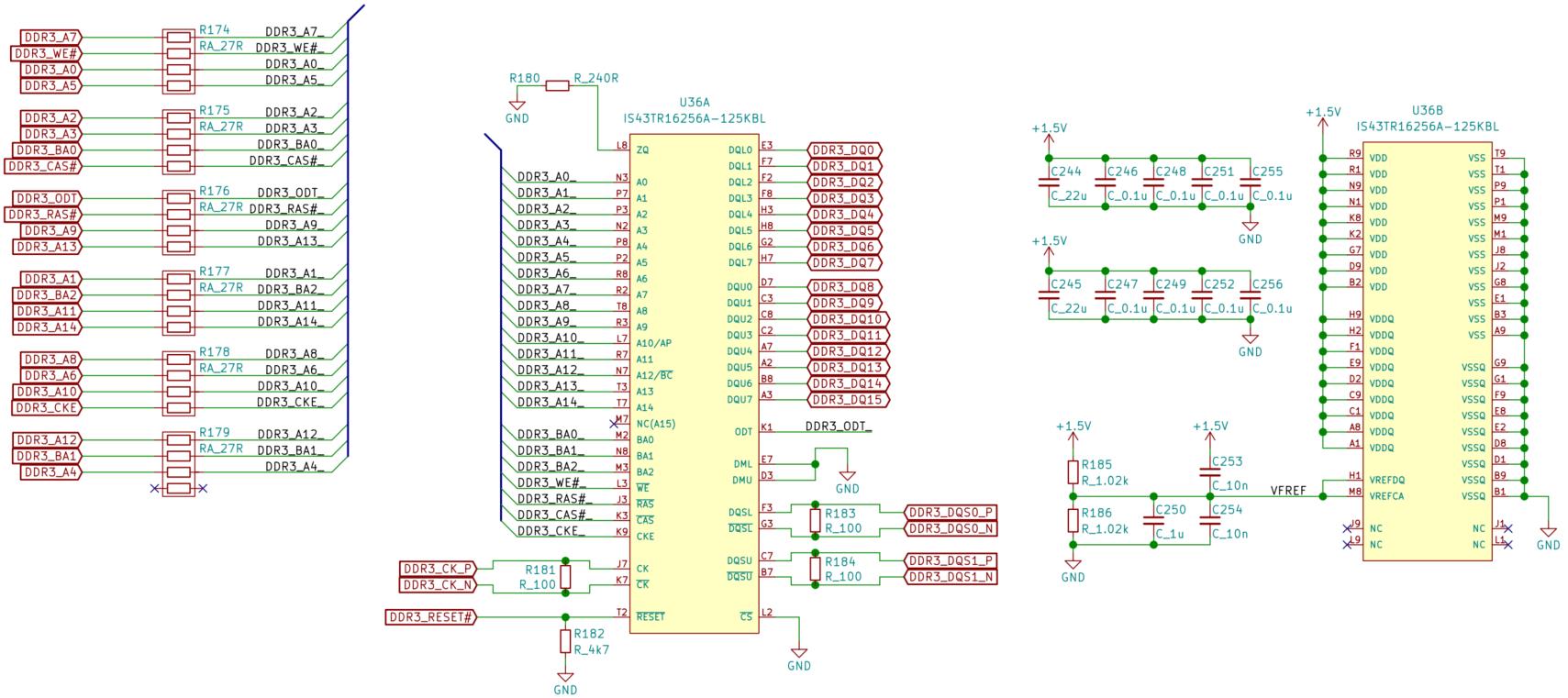

DDR3电路

以上是关于开源示波器Scopefun介绍原理图学习的主要内容,如果未能解决你的问题,请参考以下文章

深入浅出图神经网络|GNN原理解析☄学习笔记图信号处理与图卷积神经网络

深入浅出图神经网络|GNN原理解析☄学习笔记图信号处理与图卷积神经网络