贴片晶振邻层挖空背后的原理

Posted 记得诚

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了贴片晶振邻层挖空背后的原理相关的知识,希望对你有一定的参考价值。

大家好,我是记得诚。

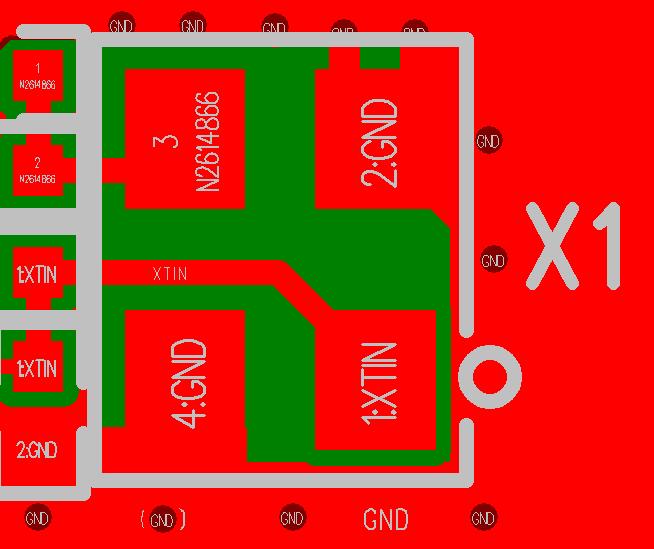

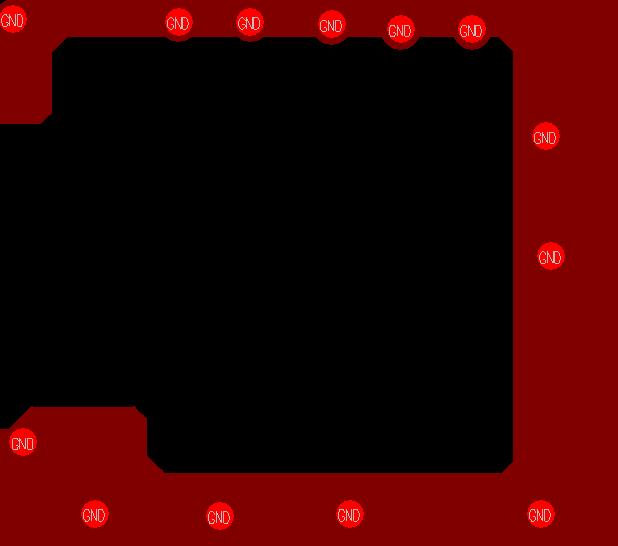

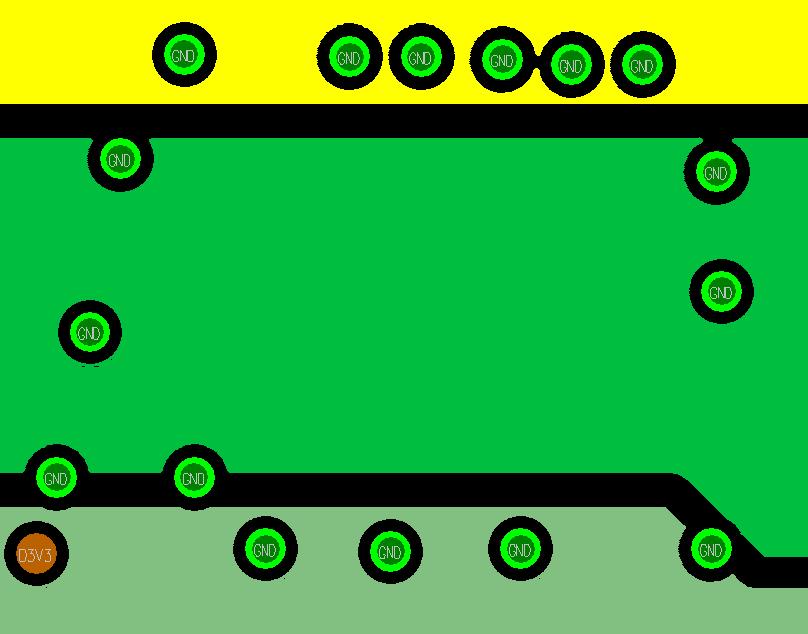

在一些多层PCB设计中,经常能看到贴片晶振在设计时,会在相邻平面层做挖空处理,如下所示:

以一块四层板为例,TOP layer有一个贴片晶振;

Layer2为GND层,在设计时用禁止区域将晶振正下方做了挖空处理;

Layer3晶振下方未进行处理;

BOTTOM layer也未做处理。

在贴片晶振邻层挖空的究竟是何用意呢?

很多人的理解是防止干扰,因为感性的认识中晶振是强大的能量体,会污染邻层平面层。

其实并不是这样的,因为即使晶振的辐射能量很强,相对于平面层来说也是微不足道的。

那么究竟是什么原因呢,本文将从负载电容恒定和抑制频偏两点进行详细分析。

1、保持负载电容的恒定

根据电容器形成原理可知,任何两个彼此绝缘且相隔很近的导体(包括导线)间都能构成一个电容器。

因为贴片晶振的焊盘是方形的,刚好可以和邻近的平面形成一个电容器。

由电容计算公式C=εs/4πkd可知,焊盘与邻近的地平面之间寄生的电容量和焊盘面积S、焊盘到平面的距离d有关。

由于焊盘面积S固定,所以晶振的方形焊盘与邻近的地平面之间寄生的电容量主要由焊盘到平面的距离d决定,d一般都很小。

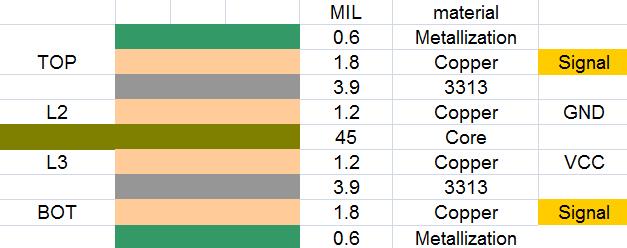

以1.6MM的四层板层压结构为例。

由图可知,芯板占了主要的厚度,焊盘到平面的距离d只有3.9mil,非常的小,如果用电容计算公式C=εs/4πkd计算出来的寄生电容在数pF-数十pF间。

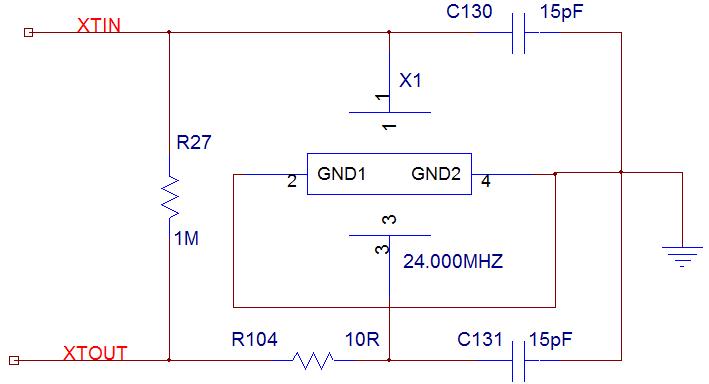

有一个实际案例是这样的:原厂参考原理图中晶振的负载电容是15pF。

但是实测发现芯片工作很不稳定,最终测试发现晶振的频偏很大,跟spec差距较大,后来把晶振的两个负载电容改小后,频偏才有所改善。

由此可见,贴片晶振的两个焊盘与其下方的平面存在着寄生电容。那寄生电容又是如何影响到晶振频偏的呢?

我们知道晶振的负载电容是由以下公式得出:

CL=C1*C2/(C1+C2)+Cparasitic;

其中Cparasitic就是寄生电容,如果这个电容过大,会直接导致晶振振荡偏离,在频偏过大时,系统很有可能工作不正常。

如果贴片晶振的两个焊盘与其下方的平面存在的寄生电容很大,超过了负载电容值,即使负载电容不贴,晶振的频偏依然很大。

因此在设计当中,尤其是对于晶体设计,更加需要控制对地的寄生电容。

一般这个数值是要保证晶体到地的距离大于250um,所以一般都要挖掉一层到两层来达到设计要求。

2、抑制热传导导致的频偏

除了负载电容会影响到晶振频偏外,但大家似乎都忘了,高温也会影响频偏。

下图是Qualcomm建议的晶振Layout Guide。

Layer 1:晶振周围不得铺铜;

Layer 2:晶振下方区块不得铺铜;

Layer 3:晶振下方区块不得铺铜;

Qualcomm在其Layout Guide中有如下解释:

如高通说法,其实真正最主要用意是隔绝热传导,避免周围的PMIC或者其他发热体的热透过铜皮传导到晶振,以至于频偏。故直接不铺铜,以隔绝热的传递。

因此,在这种情况下,寄生效应不是不重要,但相较之下,热的危害更关键一些,特别对于非DCXO晶体。

综合以上分析,在设计PCB时,遇到贴片晶振,除了对于周围包地的处理,还应该考虑挖空晶振下方的平面层。

以上是关于贴片晶振邻层挖空背后的原理的主要内容,如果未能解决你的问题,请参考以下文章