HDLBits——Vectors

Posted Mount256

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了HDLBits——Vectors相关的知识,希望对你有一定的参考价值。

HDLBits(2)——Vectors

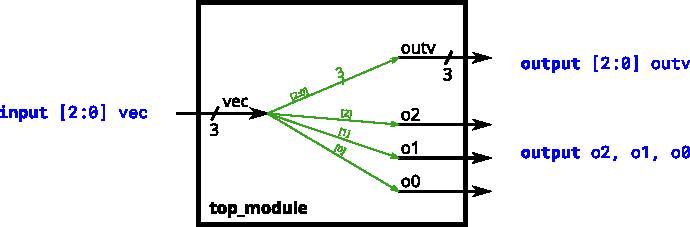

----- 11. Vector0 -----

Problem Statement

Build a circuit that has one 3-bit input, then outputs the same vector, and also splits it into three separate 1-bit outputs. Connect output o0 to the input vector’s position 0, o1 to position 1, etc.

In a diagram, a tick mark with a number next to it indicates the width of the vector (or “bus”), rather than drawing a separate line for each bit in the vector.

Answer

module top_module (

input wire [2:0] vec,

output wire [2:0] outv,

output wire o2,

output wire o1,

output wire o0 ); // Module body starts after module declaration

assign outv = vec;

assign o2 = vec[2];

assign o1 = vec[1];

assign o0 = vec[0];

endmodule

Note

- Notice that the declaration of a vector places the dimensions before the name of the vector, which is unusual compared to C syntax. However, the part select has the dimensions after the vector name as you would expect.(批注:向量的维度要放到向量的名称前进行声明,如

wire [99:0] my_vector;)

----- 12. Vector1 -----

Problem Statement

Build a combinational circuit that splits an input half-word (16 bits, [15:0] ) into lower [7:0] and upper [15:8] bytes.

Answer

`default_nettype none // Disable implicit nets. Reduces some types of bugs.

module top_module(

input wire [15:0] in,

output wire [7:0] out_hi,

output wire [7:0] out_lo );

assign out_hi = in[15:8];

assign out_lo = in[7:0];

endmodule

Note: Declaring Vectors

- Vectors must be declared:

type [upper:lower] vector_name; reg [4:1] x; // 4-bit regoutput reg [0:0] y; // 1-bit reg that is also an output port (this is still a vector)input wire [3:-2] z; // 6-bit wire input (negative ranges are allowed)wire [0:7] b; // 8-bit wire where b[0] is the most-significant bit.- The endianness (or, informally, “direction”) of a vector is whether the the least significant bit has a lower index (little-endian, e.g.,

[3:0]) or a higher index (big-endian, e.g.,[0:3]). In Verilog, once a vector is declared with a particular endianness, it must always be used the same way. e.g., writingvec[0:3]whenvecis declaredwire [3:0] vec;is illegal. (批注:向量可以从大的数字或小的数字开始,这称为向量的“大端”或“小端”。最好在一个程序中使用一致的大端或小端,否则容易出错) - Packed Arrays:

reg [7:0] mem [255:0]; // 256 unpacked elements, each of which is a 8-bit packed vector of reg.

Note: Implicit nets

- Implicit nets are always one-bit wires and causes bugs if you had intended to use a vector.

- Disabling creation of implicit nets can be done using the

`default_nettype nonedirective. - (批注:没有声明的wire为隐式声明的wire(例如下面程序的

b),它总是被默认为1位向量,这很可能会导致综合出错误的结果。可以在文件头部添加`default_nettype有助于综合器检查出隐式声明,例如下面程序,第4行程序就会报错Error,而非仅给出警告Warning)

`default_nettype none

wire [2:0] a, c; // Two vectors

assign a = 3'b101; // a = 101

assign b = a; // b = 1 implicitly-created wire

assign c = b; // c = 001 <-- bug

my_module i1 (d,e); // d and e are implicitly one-bit wide if not declared.

// This could be a bug if the port was intended to be a vector.

Note: Accessing Vector Elements: Part-Select

b[3:0] // Illegal. Vector part-select must match the direction of the declaration.(批注:数字的顺序必须与声明时的顺序相同)b[0:3] // The upper 4 bits of b.assign w[3:0] = b[0:3]; // Assign upper 4 bits of b to lower 4 bits of w. w[3]=b[0], w[2]=b[1], etc.x[1:1] // equal to x[1], also the lowest bit of xz[-1:-2] // Two lowest bits of z

----- 13. Vector2 -----

Problem Statement

A 32-bit vector can be viewed as containing 4 bytes (bits [31:24], [23:16], etc.). Build a circuit that will reverse the byte ordering of the 4-byte word.

AaaaaaaaBbbbbbbbCcccccccDddddddd => DdddddddCcccccccBbbbbbbbAaaaaaaa

This operation is often used when the endianness of a piece of data needs to be swapped, for example between little-endian x86 systems and the big-endian formats used in many Internet protocols(协议).

(批注:大端格式的数据和小端格式的数据的转换通常使用本题目的办法进行,在x86系统和许多网络协议间的数据传输中常常被使用)

Answer

module top_module(

input [31:0] in,

output [31:0] out );//

// assign out[31:24] = ...;

assign out[31:24] = in[7:0];

assign out[23:16] = in[15:8];

assign out[15:8] = in[23:16];

assign out[7:0] = in[31:24];

endmodule

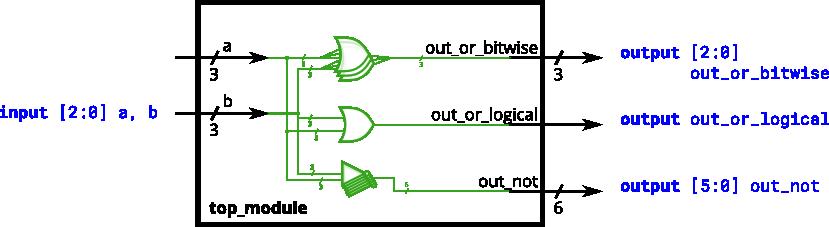

----- 14. Vectorgates -----

Problem Statement

Build a circuit that has two 3-bit inputs that computes the bitwise-OR of the two vectors, the logical-OR of the two vectors, and the inverse (NOT) of both vectors. Place the inverse of b in the upper half of out_not (i.e., bits [5:3]), and the inverse of a in the lower half.

Answer

module top_module(

input [2:0] a,

input [2:0] b,

output [2:0] out_or_bitwise,

output out_or_logical,

output [5:0] out_not

);

assign out_or_bitwise = a | b;

assign out_or_logical = a || b;

assign out_not[5:3] = ~b;

assign out_not[2:0] = ~a;

endmodule

Note

- A bitwise operation between two N-bit vectors replicates the operation for each bit of the vector and produces a N-bit output, while a logical operation treats the entire vector as a boolean value (true = non-zero, false = zero) and produces a 1-bit output.(批注:可参考“按位或”和“逻辑或”的区别:逻辑与(&&)、逻辑或(||)、按位与(&)、按位或(|)、按位异或(^)、按位取反(~))

----- 15. Gates4 -----

Problem Statement

Build a combinational circuit with four inputs, in[3:0].

There are 3 outputs:

- out_and: output of a 4-input AND gate.

- out_or: output of a 4-input OR gate.

- out_xor: output of a 4-input XOR gate.

Answer

module top_module(

input [3:0] in,

output out_and,

output out_or,

output out_xor

);

assign out_and = in[3] & in[2] & in[1] & in[0];

assign out_or = in[3] | in[2] | in[1] | in[0];

assign out_xor = in[3] ^ in[2] ^ in[1] ^ in[0];

endmodule

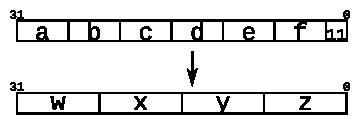

----- 16. Vector3 -----

Problem Statement

Given several input vectors, concatenate them together then split them up into several output vectors. There are six 5-bit input vectors: a, b, c, d, e, and f, for a total of 30 bits of input. There are four 8-bit output vectors: w, x, y, and z, for 32 bits of output. The output should be a concatenation of the input vectors followed by two 1 bits:

Answer

module top_module (

input [4:0] a, b, c, d, e, f,

output [7:0] w, x, y, z );

assign w[7:0] = {a[4:0], b[4:2]};

assign x[7:0] = {b[1:0], c[4:0], d[4]};

assign y[7:0] = {d[3:0], e[4:1]};

assign z[7:0] = {e[0] , f[4:0], 2'b11};

endmodule

Note: Concatenation Operator

- The concatenation operator {a,b,c} is used to create larger vectors by concatenating smaller portions of a vector together:

{1’b1, 1’b0, 3’b101} => 5’b10101 - Example:

input [15:0] in;

output [23:0] out;

assign {out[7:0], out[15:8]} = in; // Swap two bytes. Right side and left side are both 16-bit vectors.

4’ha= 0x0A,4’d10= 0x0A = 10 =8’b10101010

----- 17. Vectorr -----

Problem Statement

Given an 8-bit input vector [7:0], reverse its bit ordering.(批注:反转顺序)

Answer

module top_module(

input [7:0] in,

output [7:0] out

);

assign out[7:0] = {in[0], in[1], in[2], in[3], in[4], in[5], in[6], in[7]};

// other way: assign {out[0],out[1],out[2],out[3],out[4],out[5],out[6],out[7]} = in;

endmodule

----- 18. Vector4 -----

Problem Statement

One common place to see a replication operator is when sign-extending a smaller number to a larger one, while preserving its signed value. This is done by replicating the sign bit (the most significant bit) of the smaller number to the left. For example, sign-extending 4’b0101 (5) to 8 bits results in 8’b00000101 (5), while sign-extending 4’b1101 (-3) to 8 bits results in 8’b11111101 (-3).(批注:有符号数和无符号数的扩展位数所用的方法分别是算术右移和逻辑右移。请查阅算术右移和逻辑右移的区别)

Build a circuit that sign-extends an 8-bit number to 32 bits. This requires a concatenation of 24 copies of the sign bit (i.e., replicate bit[7] 24 times) followed by the 8-bit number itself.(提示:最高位复制24次即可)

Answer

module top_module (

input [7:0] in,

output [31:0] out );

assign out = { {24{in[7]}}, in[7:0]};

endmodule

Note: Replication Operator

{num{vector}}{5{1’b1}}// 5’b11111 (or 5’d31 or 5’h1f){2{a,b,c}}// The same as {a,b,c,a,b,c}{3’d5, {2{3’d6}}}// 9’b101_110_110.- This replicates vector by num times. num must be a constant. Both sets of braces are required.

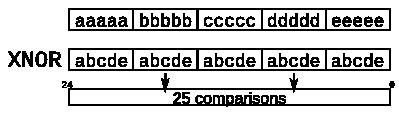

----- 19. Vector5 -----

Problem Statement

Given five 1-bit signals (a, b, c, d, and e), compute all 25 pairwise one-bit comparisons in the 25-bit output vector. The output should be 1 if the two bits being compared are equal.

out[24] = ~a ^ a; // a == a, so out[24] is always 1.

out[23] = ~a ^ b;

out[22] = ~a ^ c;

...

out[ 1] = ~e ^ d;

out[ 0] = ~e ^ e;

As the diagram shows, this can be done more easily using the replication and concatenation operators.

- The top vector is a concatenation of 5 repeats of each input

- The bottom vector is 5 repeats of a concatenation of the 5 inputs

Answer1

module top_module (

input a, b, c, d, e,

output [24:0] out );

wire [24:0] temp1, temp2;

assign temp1 = { {5{a}}, {5{b}}, {5{c}}, {5{d}}, {5{e}} };

assign temp2 = { {5{a, b, c, d, e}} };

assign out = ~temp1 ^ temp2;

endmodule

Answer2

module top_module (

input a, b, c, d, e,

output [24:0] out );

assign out = ~{ {5{a}}, {5{b}}, {5{c}}, {5{d}}, {5{e}} } ^ { {5{a, b, c, d, e}} };

endmodule

以上是关于HDLBits——Vectors的主要内容,如果未能解决你的问题,请参考以下文章