Cortex-A7 MPCore 架构详细介绍

Posted 行稳方能走远

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了Cortex-A7 MPCore 架构详细介绍相关的知识,希望对你有一定的参考价值。

目录

0.ARM架构的历史简介

摘自:「ARM 架构」是一种怎样的处理器架构? - 大狸的回答 - 知乎

https://www.zhihu.com/question/325679399/answer/692728301

打个比方,ARM一开始是一家盖房子的公司,后面这家公司盖房子业绩平平,于是就转变策略不盖房子了,转而开始卖盖房子所需要的设计图纸方案,同时还和买方案盖房子的客户一起盖房子。在这里,房子就是所谓的芯片,图纸方案就是指芯片的算法,架构等等的知识产权。

ARM向他的客户提供授权,软件包等,通过授权费和版税赚钱,然后因为这种模式,又因为很多公司也需要芯片处理器,于是ARM就与很多公司产生了合作关系,比如德州仪器,苹果,诺基亚等等。

90年代初,移动终端开始兴起,ARM认为移动终端的前景不错,就和诺基亚合作推出了第一款ARM处理器的手机。后面尝到了甜头,而且和乔布斯的关系也挺好,于是就专门为苹果产品设计了处理器,而乔布斯天才的产品能力,将iPod和iPhone打造成了改变世界的爆款。

由于各种应用都是建立在ARM的地基上的,ARM的处理器便理所应当的一跃成为移动终端中无法替代的核心。那么好吧,谷歌研发安卓的时候一看大家都是这么玩,也只能顺应潮流,就把房子盖在ARM的地基上了。

ARM的对手,因特尔在90年代初因为觉得手机没什么发展前景,不肯投入,把这块市场拱手让给了ARM,现在估计肠子都悔青了。ARM走到今天这一步,也是顺应了科技的潮流,因为移动终端的迅猛发展,将它推到了这个位置上。

ARM早些年的芯片分为ARMv1,2,3,4,5,6体系,每个体系下又有细分的产品,后来ARM觉得这个名字不好听,在做新的处理器ARMv7体系架构时就起了个听起来高大上的名字,叫大脑皮层Cortex,对应不同的市场分别有三个系列A,R,M。其中,A系列是对应智能移动终端的。

ARM的处理器所用的指令集为精简指令集RISC(Reduced Instruction Set Computing),其指令比较简单,ARM处理器的功耗是非常低的,所以是很适用于手机这种小型的移动设备上的。

现如今的手机芯片,都需要在ARM搭建好的框架里去"盖房子",要想去搭建框架,不是一朝一夕能够完成的,将会是一个漫长探索,大量投入过程。

1.Cortex-A7 MPCore 简介

参考了《Cortex-A7 Technical ReferenceManua.pdf》和《ARM Cortex-A(armV7)编程手册 V4.0.pdf》这俩份文档,这两份文档都是 ARM 官方的文档,详细的介绍了 Cortex-A7 架构和ARMv7-A 指令集。

Cortex-A7 MPcore 处理器支持 1~4 核,通常是和 Cortex-A15 组成 big.LITTLE 架构的,Cortex-A15 作为大核负责高性能运算,比如玩游戏啥的,Cortex-A7 负责普通应用,因为 Cortex-A7 省电。

Cortex-A7 本身性能也不弱,不要看它叫做 Cortex-A7 但是它可是比 Cortex-A8 性能要强大,而且更省电。ARM 官网对于 Cortex-A7 的说明如下:

“在 28nm 工艺下,Cortex-A7 可以运行在 1.2~1.6GHz,并且单核面积不大于 0.45mm 2 (含有浮点单元、NEON 和 32KB 的 L1 缓存),在典型场景下功耗小于 100mW, 这使得它非常适合对功耗要求严格的移动设备,这意味着 Cortex-A7 在获得与 Cortex-A9 相似性能的情况下,其功耗更低”。

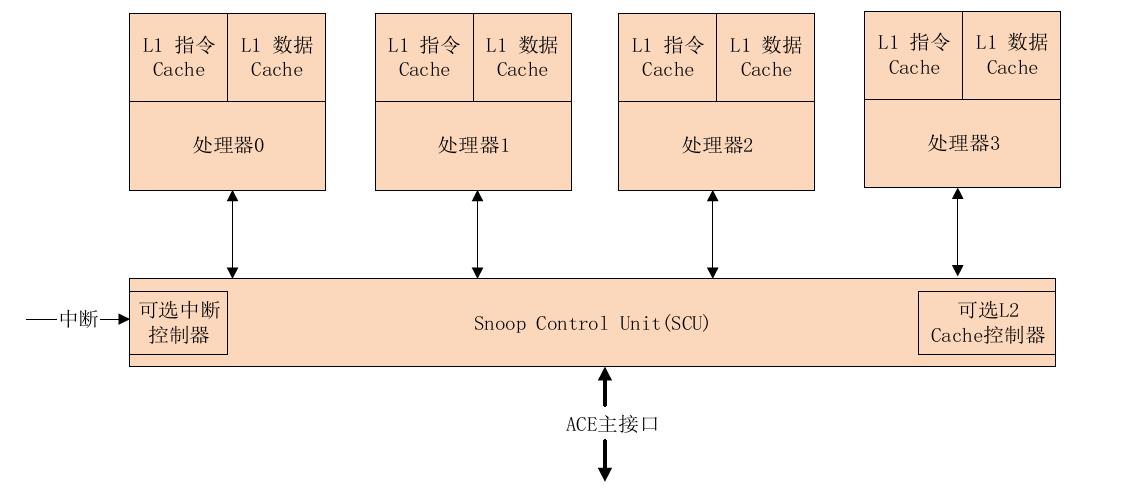

Cortex-A7 MPCore 支持在一个处理器上选配 1~4 个内核,Cortex-A7 MPCore 多核配置如图:

Cortex-A7 MPCore 的 L1 可选择 8KB、16KB、32KB、64KB,L2 Cache 可以不配,也可以选择 128KB、256KB、512KB、1024KB。I.MX6UL 配置了 32KB 的 L1 指令 Cache 和 32KB 的L1 数据 Cache,以及 128KB 的 L2 Cache。Cortex-A7MPCore 使用 ARMv7-A 架构,主要特性如下:

- ①、SIMDv2 扩展整形和浮点向量操作。

- ②、提供了与 ARM VFPv4 体系结构兼容的高性能的单双精度浮点指令,支持全功能的IEEE754。

- ③、支持大物理扩展(LPAE),最高可以访问 40 位存储地址,也就是最高可以支持 1TB 的内存。

- ④、支持硬件虚拟化。

- ⑤、支持 Generic Interrupt Controller(GIC)V2.0。

- ⑥、支持 NEON,可以加速多媒体和信号处理算法。

2.Cortex-A 处理器运行模型

以前的 ARM 处理器有 7 种运行模型:User、FIQ、IRQ、Supervisor(SVC)、Abort、Undef和 System,其中 User 是非特权模式(某些访问受限,比如你的开机密码),其余 6 中都是特权模式(访问不受限)。但新的 Cortex-A 架构加入了TrustZone 安全扩展,所以就新加了一种运行模式:Monitor,新的处理器架构还支持虚拟化扩展,因此又加入了另一个运行模式:Hyp,所以 Cortex-A7 处理器有 9 种处理模,如表(知道前3个即可):

| 模式 | 描述 |

|---|---|

| User(USR) | 用户模式,非特权模式,大部分程序运行的时候就处于此模式。 |

| FIQ | 快速中断模式,进入 FIQ 中断异常 |

| IRQ | 一般中断模式。 |

| Supervisor(SVC) | 超级管理员模式,特权模式,供操作系统使用。 |

| Monitor(MON) | 监视模式?这个模式用于安全扩展模式。 |

| Abort(ABT) | 数据访问终止模式,用于虚拟存储以及存储保护。 |

| Hyp(HYP) | 超级监视模式?用于虚拟化扩展。 |

| Undef(UND) | 未定义指令终止模式。 |

| System(SYS) | 系统模式,用于运行特权级的操作系统任务 |

注:‘?’表示为笔者翻译,不保证翻译的准确性。

除了 User(USR)用户模式以外,其它 8 种运行模式都是特权模式。这几个运行模式可以通过软件进行任意切换,也可以通过中断或者异常来进行切换。大多数的程序都运行在用户模式,用户模式下是不能访问系统所有资源的,有些资源是受限的,要想访问这些受限的资源就必须进行模式切换。但是用户模式是不能直接进行切换的,用户模式下需要借助异常来完成模式切换,当要切换模式的时候,应用程序可以产生异常,在异常的处理过程中完成处理器模式切换。

当中断或者异常发生以后,处理器就会进入到相应的异常模式种,每一种模式都有一组寄存器供异常处理程序使用,这样的目的是为了保证在进入异常模式以后,用户模式下的寄存器不会被破坏。

如果学过 STM32 和 UCOS、FreeRTOS 就会知道,STM32 只有两种运行模式,特权模式和非特权模式,但是 Cortex-A 就有 9 种运行模式。

3.Cortex-A 寄存器组

Cortex-A 的内核寄存器组,注意不是芯片的外设(RAM)寄存器

寄存器:指的是CPU内核里的寄存器,如r0,r1等

外设寄存器:一般是指一些某一特殊功能的物理地址,外设寄存器的物理地址都在0x48000000~0x5FFFFFFF。外设寄存器就是平常说的ARM中的特殊功能寄存器。

CPU,全名Central Processing Unit(中央处理器)。这是一块超大规模的集成电路,包含上亿的晶体管,是一台计算机的运算核心(Core)和控制核心(ControlUnit)。它的功能主要是解释计算机指令以及处理计算机软件中的数据。

它的主要构成是:运算器、控制器、寄存器

- 运算器:可以执行定点或浮点算术运算操作、移位操作以及逻辑操作,也可执行地址运算和转换。

- 控制器:主要是负责对指令译码,并且发出为完成每条指令所要执行的各个操作的控制信号。其结构有两种:一种是以微存储为核心的微程序控制方式;一种是以逻辑硬布线结构为主的控制方式。

- 寄存器:寄存器部件,包括寄存器、专用寄存器和控制寄存器。通用寄存器又可分定点数和浮点数两类,它们用来保存指令执行过程中临时存放的寄存器操作数和中间(或最终)的操作结果。通用寄存器是中央处理器的重要部件之一。

主要参考

《ARM Cortex-A(armV7)编程手册 V4.0.pdf》的“第 3 章 ARM Processor Modes And Registers”。

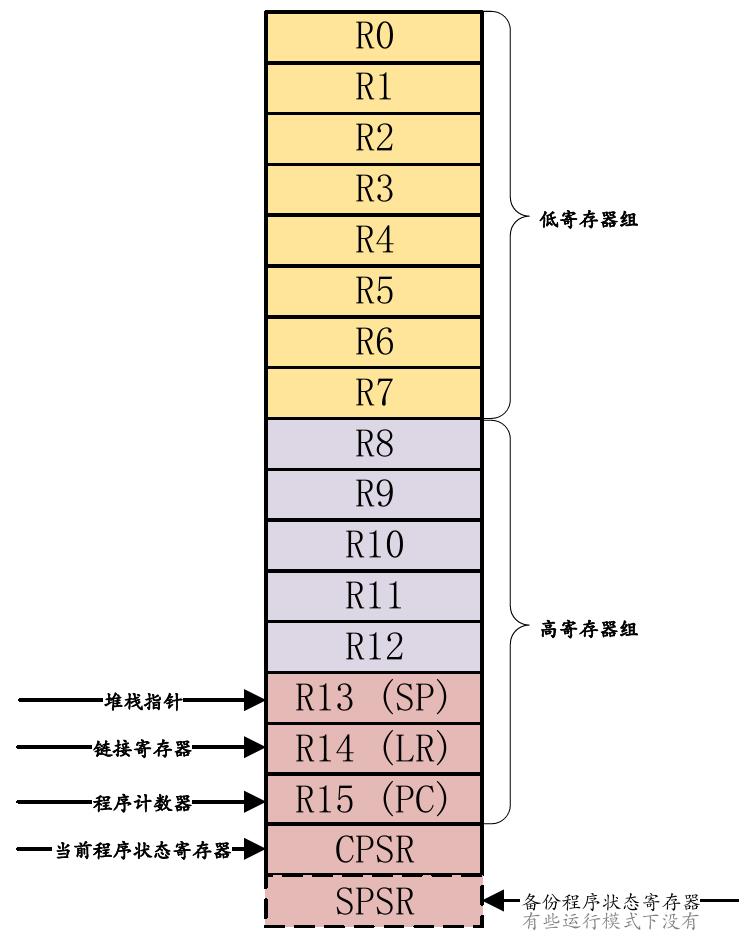

ARM 架构提供了 16 个 32 位的通用寄存器(R0~R15)供软件使用,前 15 个(R0~R14)可以用作通用的数据存储,R15 是程序计数器 PC,用来保存将要执行的指令。ARM 还提供了一个当前程序状态寄存器 CPSR 和一个备份程序状态寄存器 SPSR,SPSR 寄存器就是 CPSR 寄存器的备份(标了虚线,表示有些模式下是没有的)。

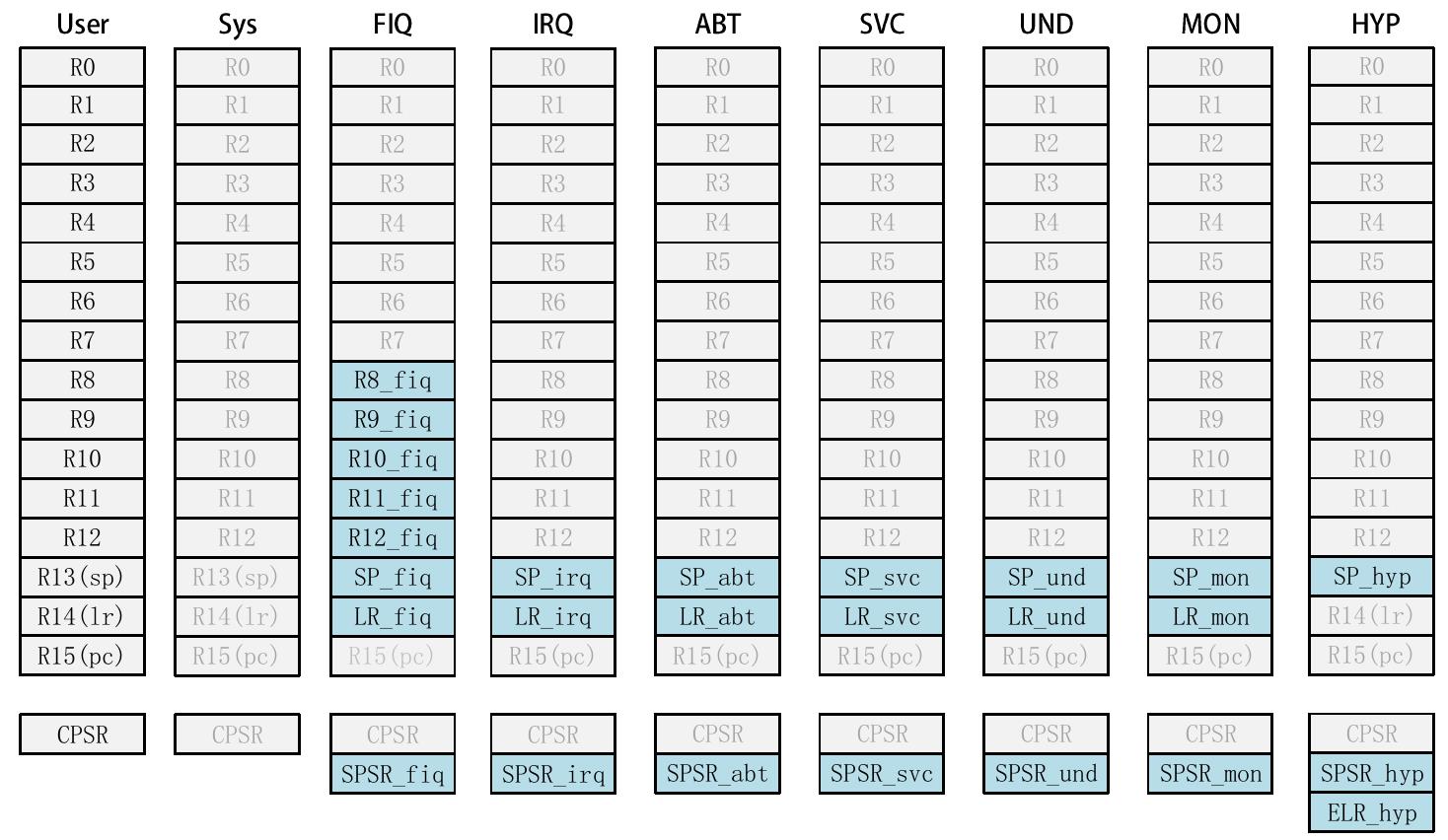

Cortex-A7 有 9 种运行模式,每一种运行模式都有一组与之对应的寄存器。每一种模式可见的寄存器包括 15 个通用寄存器(R0~R14)、一两个程序状态寄存器和一个程序计数器 PC。在这些寄存器中,有些是所有模式所共用的同一个物理寄存器,有一些是各模式自己所独立拥有的,各个模式所拥有的寄存器如表:

浅色字体的是与 User 模式所共用的寄存器,蓝绿色背景的是各个模式所独有的寄存器。可以看出,在所有的模式中,低寄存器组(R0~R7)是共享同一组物理寄存器的,只是一些高寄存器组在不同的模式有自己独有的寄存器,比如 FIQ 模式下 R8~R14 是独立的物理寄存器。假如某个程序在 FIQ 模式下访问 R13 寄存器,那它实际访问的是寄存器 R13_fiq,如果程序处于 SVC 模式下访问 R13 寄存器,那它实际访问的是寄存器 R13_svc。总结一下,Cortex-A 内核寄存器组成如下:

- ①、34 个通用寄存器,包括 R15 程序计数器(PC),这些寄存器都是 32 位的。

- ②、8 个状态寄存器,包括 CPSR 和 SPSR。

- ③、Hyp 模式下独有一个 ELR_Hyp 寄存器。

注意:ARM的CPU 不能直接访问存储器(RAM)中的数据,必须要通过中间的寄存器R0(还是RX?),在后面的汇编章节会讲到。

3.1通用寄存器

R0~R15 就是通用寄存器,通用寄存器可以分为以下三类:

①、未备份寄存器,即 R0~R7。

②、备份寄存器,即 R8~R14。

③、程序计数器 PC,即 R15。

3.1.1未备份寄存器

未备份寄存器指的是 R0~R7 这 8 个寄存器,因为在所有的处理器模式下这 8 个寄存器都是同一个物理寄存器,在不同的模式下,这 8 个寄存器中的数据就会被破坏。所以这 8 个寄存器并没有被用作特殊用途

3.1.2备份寄存器

备份寄存器中的 R8~R12 这 5 个寄存器有两种物理寄存器,在快速中断模式下(FIQ)它们对应着 Rx_irq(x=8~12)物理寄存器,其他模式下对应着 Rx(8~12)物理寄存器。FIQ 是快速中断模式,看名字就是知道这个中断模式要求快速执行! FIQ 模式下中断处理程序可以使用 R8~R12寄存器,因为 FIQ 模式下的 R8~R12 是独立的,因此中断处理程序可以不用执行保存和恢复中断现场的指令,从而加速中断的执行过程。

备份寄存器 R13 一共有 8 个物理寄存器,其中一个是用户模式(User)和系统模式(Sys)共用的,剩下的 7 个分别对应 7 种不同的模式。R13 也叫做 SP,用来做为栈指针。基本上每种模式都有一个自己的 R13 物理寄存器,应用程序会初始化 R13,使其指向该模式专用的栈地址,这就是常说的初始化 SP 指针。

备份寄存器 R14 一共有 7 个物理寄存器,其中一个是用户模式(User)、系统模式(Sys)和超级监视模式(Hyp)所共有的,剩下的 6 个分别对应 6种不同的模式。R14 也称为连接寄存器(LR),LR 寄存器在 ARM 中主要用作如下两种用途:

- ①、每种处理器模式使用 R14(LR)来存放当前子程序的返回地址,如果使用 BL 或者 BLX来调用子函数的话,R14(LR)被设置成该子函数的返回地址,在子函数中,将 R14(LR)中的值赋给 R15(PC)即可完成子函数返回,比如在子程序中可以使用如下代码:

MOV PC, LR 寄存器 LR 中的值赋值给 PC,实现跳转\\

或者可以在子函数的入口出将 LR 入栈:

PUSH {LR} 将 LR 寄存器压栈

在子函数的最后面出栈即可:

POP {PC} 将上面压栈的 LR 寄存器数据出栈给 PC 寄存器,严格意义上来讲应该是将LR-4 赋给 PC,因为 3 级流水线,这里只是演示代码。

- ②、当异常发生以后,该异常模式对应的R14寄存器被设置成该异常模式将要返回的地址,R14 也可以当作普通寄存器使用。

3.1.3程序计数器 R15

程序计数器 R15 也叫做 PC,R15 保存着当前执行的指令地址值加 8 个字节,这是因为 ARM的流水线机制导致的。ARM 处理器 3 级流水线:取指->译码->执行,这三级流水线循环执行,比如当前正在执行第一条指令的同时也对第二条指令进行译码,第三条指令也同时被取出存放在 R15(PC)中。

我们喜欢以当前正在执行的指令作为参考点,也就是以第一条指令为参考点,那么 R15(PC)中存放的就是第三条指令,换句话说就是 R15(PC)总是指向当前正在执行的指令地址再加上 2 条指令的地址。对于 32 位的 ARM 处理器,每条指令是 4 个字节,所以:

R15 (PC)值 = 当前执行的程序位置 + 8 个字节。

3.2程序状态寄存器

所有的处理器模式都共用一个 CPSR 物理寄存器,因此 CPSR 可以在任何模式下被访问。CPSR 是当前程序状态寄存器,该寄存器包含了条件标志位、中断禁止位、当前处理器模式标志等一些状态位以及一些控制位。所有的处理器模式都共用一个 CPSR 必然会导致冲突,为此,除了 User 和 Sys 这两个模式以外,其他 7 个模式每个都配备了一个专用的物理状态寄存器,叫做 SPSR(备份程序状态寄存器),当特定的异常中断发生时,SPSR 寄存器用来保存当前程序状态寄存器(CPSR)的值,当异常退出以后可以用 SPSR 中保存的值来恢复 CPSR。

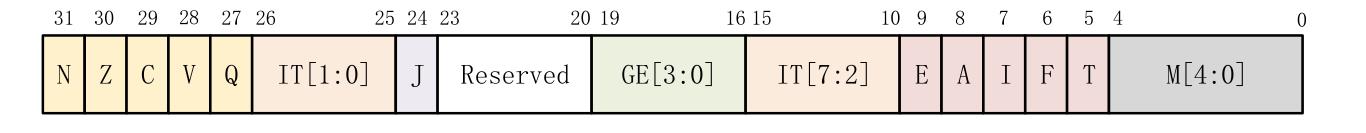

因为 User 和 Sys 这两个模式不是异常模式,所以并没有配备 SPSR,因此不能在 User 和Sys 模式下访问 SPSR,会导致不可预知的结果。由于 SPSR 是 CPSR 的备份,因此 SPSR 和CPSR 的寄存器结构相同,如图

-

N(bit31):当两个补码表示的 有符号整数运算的时候,N=1 表示运算对的结果为负数,N=0表示结果为正数。

-

Z(bit30) :Z=1 表示运算结果为零,Z=0 表示运算结果不为零,对于 CMP 指令,Z=1 表示进行比较的两个数大小相等。

-

C(bit29):在加法指令中,当结果产生了进位,则 C=1,表示无符号数运算发生上溢,其它情况下 C=0。在减法指令中,当运算中发生借位,则 C=0,表示无符号数运算发生下溢,其它情况下 C=1。对于包含移位操作的非加/减法运算指令,C 中包含最后一次溢出的位的数值,对于其它非加/减运算指令,C 位的值通常不受影响。

-

V(bit28) :对于加/减法运算指令,当操作数和运算结果表示为二进制的补码表示的带符号数时,V=1 表示符号位溢出,通常其他位不影响 V 位。

-

Q(bit27) :仅 ARM v5TE_J 架构支持,表示饱和状态,Q=1 表示累积饱和,Q=0 表示累积不饱和。

-

IT[1:0] (bit26:25) :和 IT[7:2] (bit15:bit10) 一起组成 IT[7:0],作为 IF-THEN 指令执行状态。

-

J(bit24): 仅 ARM_v5TE-J 架构支持,J=1 表示处于 Jazelle 状态,此位通常和 T(bit5)位一起表示当前所使用的指令集,如表

| J | T | 描述 |

|---|---|---|

| 0 | 0 | ARM |

| 0 | 1 | Thumb |

| 1 | 1 | ThumbEE |

| 1 | 0 | Jazelle |

- GE[3:0 ] (bit19:16):SIMD 指令有效,大于或等于。

- IT[7:2] (bit15:10) :参考 IT[1:0]。

- E(bit9) :大小端控制位,E=1 表示大端模式,E=0 表示小端模式。

- A(bit8) :禁止异步中断位,A=1 表示禁止异步中断。

- I(bit7) :I=1 禁止 IRQ,I=0 使能 IRQ。

- F(bit6) :F=1 禁止 FIQ,F=0 使能 FIQ。

- T(bit5) :控制指令执行状态,表明本指令是 ARM 指令还是 Thumb 指令,通常和 J(bit24)一起表明指令类型,参考 J(bit24)位。

- M[4:0] :处理器模式控制位,含义如表

| M[4:0] | 处理器模式 |

|---|---|

| 10000 | User 模式 |

| 10001 | FIQ 模式 |

| 10010 | IRQ 模式 |

| 10011 | Supervisor(SVC)模式 |

| 10110 | Monitor(MON)模式 |

| 10111 | Abort(ABT)模式 |

| 11010 | Hyp(HYP)模式 |

| 11011 | Undef(UND)模式 |

| 11111 | System(SYS)模式 |

以上是关于Cortex-A7 MPCore 架构详细介绍的主要内容,如果未能解决你的问题,请参考以下文章

iMX6ULL使用的Cortex-A7 MPCore内核架构基础总结(内核配置处理器运行模型寄存器组)

iMX6ULL使用的Cortex-A7 MPCore内核架构基础总结(内核配置处理器运行模型寄存器组)

iMX6ULL使用的Cortex-A7 MPCore内核架构基础总结(内核配置处理器运行模型寄存器组)