SystemVerilog 采样和数据驱动

Posted JustKeen

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了SystemVerilog 采样和数据驱动相关的知识,希望对你有一定的参考价值。

modport是限制信号传输方向的,避免端口连接的错误。

可以在接口声明clocking(时序块)和采样的时钟信号,用来做信号的同步和采样。

clocking块基于时钟周期对信号进行驱动或者采样的方式,使得testbench不在苦恼于如何准时及时的对信号驱动或者采样,消除了信号竞争的问题。(解决delt-cycle,不用人为的添加delay)

自己用的时钟块都是出现在interface里面,但是规定可以使得他在module和interface和program中使用。

clocking中列举的信号不是自己定义的,而是由interface或者其他声明clocking的module定义的。

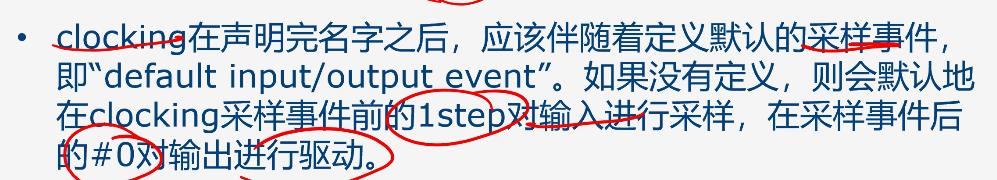

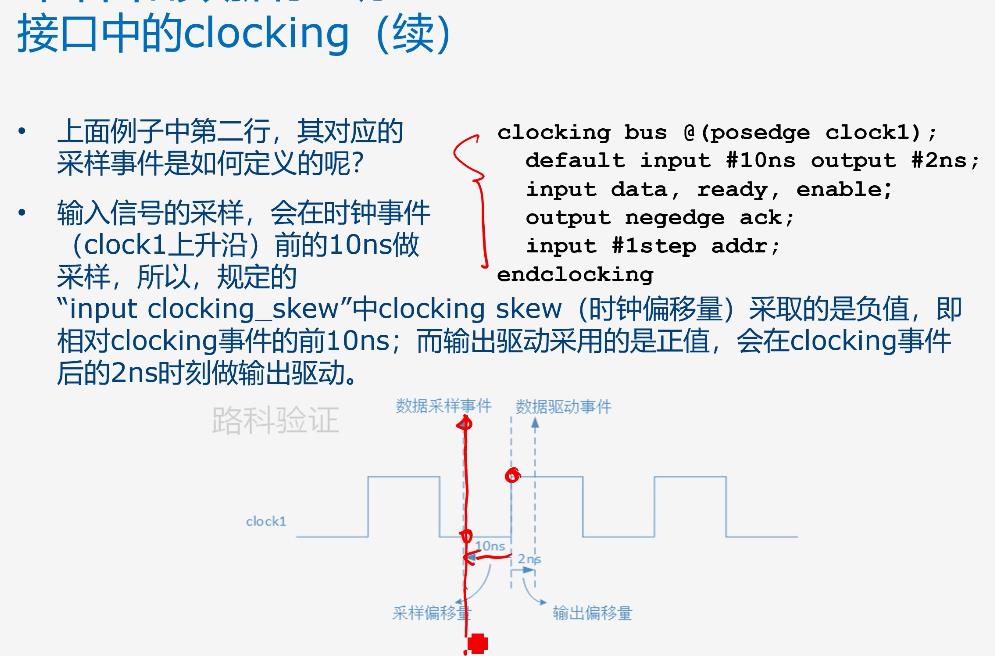

clocking bus @(posedge clock1);//定义了一个clocking块bus由clock1的上升沿驱动和采样。

default input #10ns output #2ns;//clocking的所有信号默认情况下会在clocking时间(clock1上升沿)前10ns来对其进行输入采样,在时间的后面2ns对其进行输出驱动。

#0是包含很多个delt-cycle的。

新的事件会对默认的事件进行覆盖。

input data,ready,enable;//采用的默认输入事件,即提前10ns

output negedge ack;//驱动ack事件是clock1的下降沿但是仍然延后2ns,覆盖了原有的默认输出事件(上升沿后的2ns)

input #1step addr;//自身的定义采样事件,clock1上升沿前的1step。

//1step会是的采样发生在clock1上升沿的上一个时间片的采样区域,可以保证采样到的数据是上一个时钟周期的数据。

input是在之前,output是在之后。

endclocking

习题:

答案:C

不同的clocking可以声明不同的方向

利用clocking的采样:

module clocking1;

bit vld;

bit grt;

bit clk;

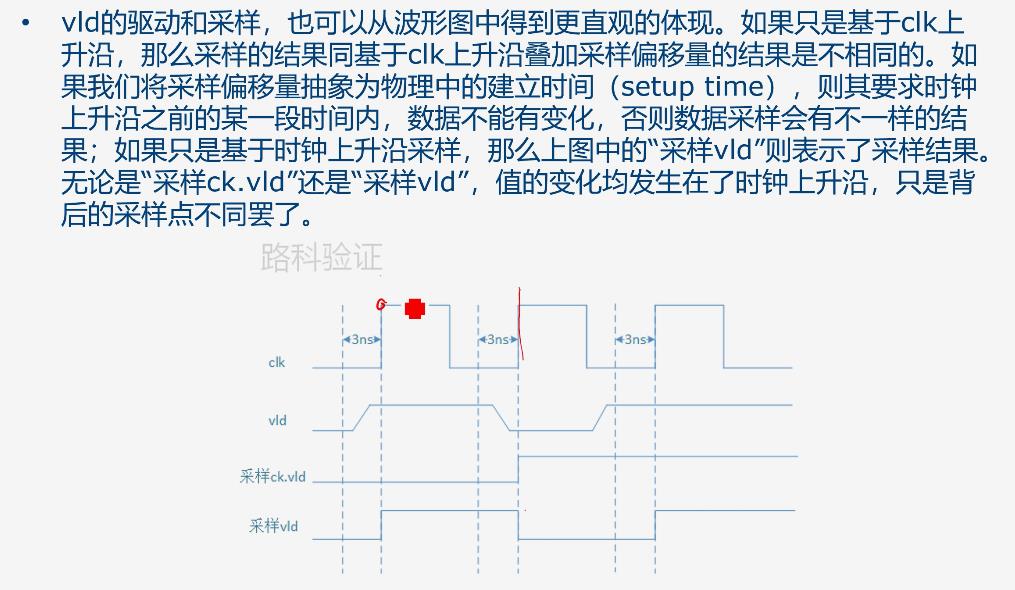

clocking ck @(posedge clk);

default :input #3ns output #3ns;

input vld;

output grt;

endclocking

initial forever #5ns clk < =~clk;

iinitial begin :drv_vld

$display(" ");

#3ns vld = 1; $display(" ");

#10ns vld=0; $display(" " );

#8ns vld = 1;$display(" ");

end

initial forever

@ck $display(" .....",vld,$time);

initial forever

@ck $display(" ..",ck.vld,$time-3 );//此处调用了ck块进行的采样

endmodule

在这个例子里面@ck等价于@(posedge clk)

建议使用clocking块进行采样

例子:用clocking块做驱动

module clocking2;

bit vld;

bit grt;

bit clk;

clocking ck @(posedge clk);

default input #3ns output #3ns;

input vld;

output grt;

endclocking

initial forever #5ns clk<=~clk;

initial begin:drv_grt

$display("...",$time,grt);

@ck ck.grt<=1;

$display(".....",$time);

@ck ck.grt<=0;$display(" ",$time);

@ck ck.grt<=1;$display(" ",$time);

end

initial forever

@grt $display(" ..",$time,grt);

endmodule

可以从根本上消除掉采样产生的竞争

以上是关于SystemVerilog 采样和数据驱动的主要内容,如果未能解决你的问题,请参考以下文章