层次建模的概念

Posted 辰风阆苑

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了层次建模的概念相关的知识,希望对你有一定的参考价值。

理解数字电路设计中的自底向上和自顶向下的设计方法。

解释verilog中模块和模块实例之间的区别。

学习四种不同的抽象角度来描述同一个模块。

解释数字电路仿真中的各个组成部分,定义激励块和功能块,说明两种使用激励进行仿真的方法。

1. 设计方法学

数字电路设计中有两种基本的设计方法:自底向上和自顶向下。在典型的设计中,这两种方法是混合使用的。设计人员首先根据电路的体系结构定义顶层模块。逻辑设计者确定如何根据功能将整个设计划分为子模块;与此同时电路设计者对底层模块进行优化,并进一步使用这些底层模块来搭建其高层模块。两者的工作按相反的方向独立进行,直至在某一中间点会和。

2. 四位脉动计数器

3. 模块分解

将整个设计进行层次化建模。

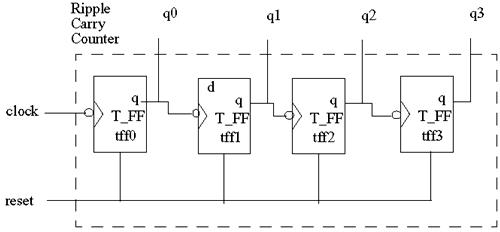

(1) 脉动进位计数器顶层

首先顶层将四个T_FF相连接,下一步就是T_FF 触发器子层设计。

1 module ripple_carry_counter ( 2 input wire clk, 3 input wire rst_n, 4 output wire [3:0] q 5 ); 6 7 T_FF tff0 ( .clk(clk), .rst_n(rst_n), .q(q[0]) ); 8 T_FF tff1 ( .clk(q[0]), .rst_n(rst_n), .q(q[1]) ); 9 T_FF tff2 ( .clk(q[1]), .rst_n(rst_n), .q(q[2]) ); 10 T_FF tff3 ( .clk(q[2]), .rst_n(rst_n), .q(q[3]) ); 11 12 endmodule

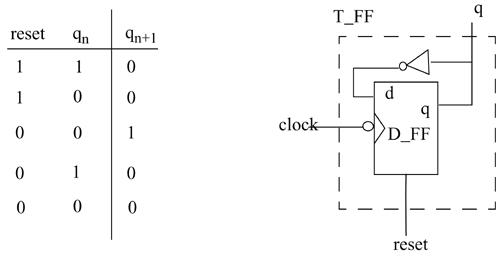

(2) 触发器 T_FF

在T_FF层中有两个模块,一个是D_FF 还有一个是非门。

1 module T_FF ( 2 input wire clk, 3 input wire rst_n, 4 output wire q 5 ); 6 7 D_FF dff0 ( .clk(clk), .rst_n(rst_n), .d(d), .q(q) ); 8 not n1 ( d,q ); 9 10 endmodule

(3)触发器 D_FF

最后一层就是D_FF。

1 module D_FF ( 2 input wire clk, 3 input wire rst_n, 4 input wire d, 5 output reg q 6 ); 7 always @(negedge clk or negedge rst_n) begin 8 if(!rst_n) 9 q <= 1\'b0; 10 else 11 q <= d; 12 end 13 14 endmodule

(4) 测试激励模块

1 `timescale 1ns/1ps 2 module ripple_carry_counter_tb ; 3 reg clk; 4 reg rst_n; 5 wire [3:0] q; 6 7 ripple_carry_counter ripple_carry_counter0( 8 .clk (clk), 9 .rst_n (rst_n), 10 .q (q) 11 ); 12 13 initial begin 14 clk = 0; 15 end 16 always #5 clk = ~clk; 17 18 initial begin 19 rst_n = 1\'b0; 20 #15 21 rst_n = 1\'b1; 22 #180 23 rst_n = 1\'b0; 24 #10 25 rst_n = 1\'b1; 26 #20 27 $finish; 28 end 29 30 initial begin 31 $monitor ($time, "\\toutput q = %d", q); 32 end 33 34 endmodule

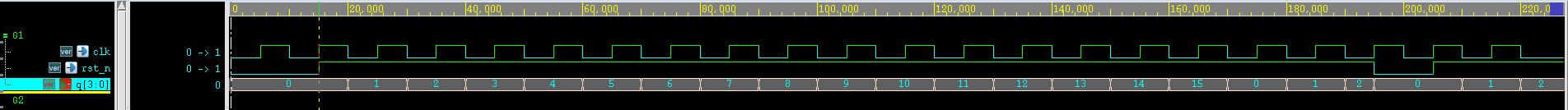

4. 仿真结果

5. 小结

在本章中,讨论了以下概念:

- 用于数字电路设计的两种方法:自顶向下和自底向上。在当今数字电路设计中,这两种方法经常组合使用。随着设计复杂性的增加,使用这些结构化的方法来进行设计管理变得越来越重要。

- 模块是verilog中的基本单元。模块通过调用(实例引用)来使用,模块的每个实例都被唯一标识,以区别于同一模块的其他实例。每个实例都拥有其模板模块的不同副本。需将模块和实例区分开来。

- 仿真有两个不同的组成部分:设计块和激励块,激励用于测试设计块。激励块通常是顶层模块。对设计块施加激励有两种不同的模式。

- 以脉动进位计数器为例,一步步地解释了各个部分创建仿真的过程。

以上是关于层次建模的概念的主要内容,如果未能解决你的问题,请参考以下文章