吃透MIPI接口,你必须了解它这三种PHY规范的区别

Posted 浩瀚之水_csdn

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了吃透MIPI接口,你必须了解它这三种PHY规范的区别相关的知识,希望对你有一定的参考价值。

MIPI接口及其物理层特性

MIPI(移动行业处理器接口)是专为移动设备(如智能手机、平板电脑、笔记本电脑和混合设备)设计的行业规范的标准定义。MIPI标准定义了三个通用的唯一物理(PHY)层,即MIPID-PHY、C-PHY和M-PHY。我们可以通过应用各规范来支持多种协议层和应用。

MIPI D-PHY

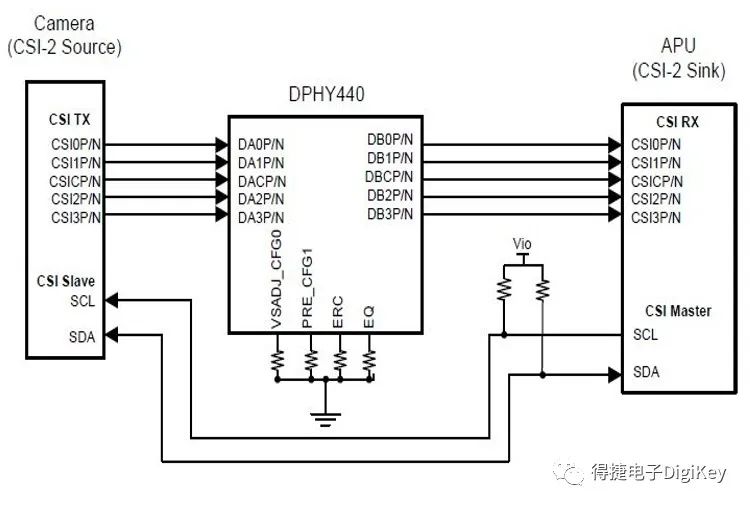

MIPI D-PHY更常用于智能手机的相机和显示屏,因为它具有灵活、高速、低功耗和低成本的特点。对于非移动行业,该物理层还可应用于汽车摄像头传感系统、防撞雷达、车内信息娱乐系统和仪表盘显示器。例如,德州仪器(TI)的SNx5DPHY440SS系列,如下图所示。DHY芯片能够自动补偿信号源与应用级端口各输入引脚的数据通道之间的偏差,因此可以减少电路冗余。

MIPI C-PHY

MIPI C-PHY通过带宽受限通道来实现高吞吐量性能,例如将显示器和摄像头连接到应用处理器。它可为MIPI相机串行接口(MIPICSI-2)和MIPI显示接口(MIPI DSI-2)生态系统提供PHY,帮助设计人员扩展其实现,以支持各种更高分辨率的图像传感器和显示器。

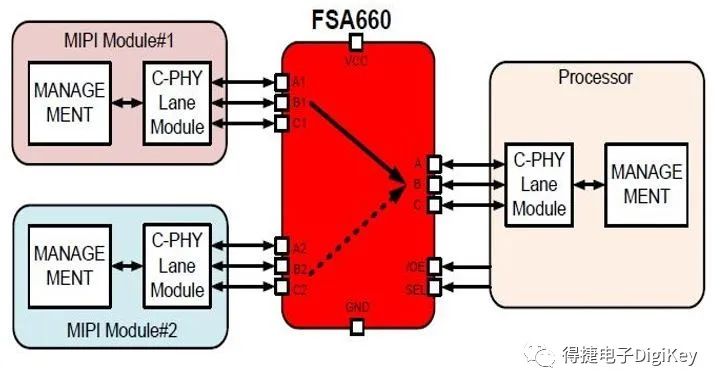

例如,安森美(ONSEMI)的FSA660TMX(如下图所示)可实现高速源交换功能。

图1 FSA660TMX的应用示意图

MIPI M-PHY

MIPI M-PHY专为需要快速通信通道以支持高分辨率图像、高视频帧速率和大型显示器或存储器的数据密集型应用而设计。这是一款多功能PHY,能够为工程师提供可跨行业平台开发的配置选项和功能,以有效解决多个市场和用例。

下面来简单地对比一下这三种物理层规范。

| 特性 | M-PHY | D-PHY | C-PHY |

| 主要用例 | 性能驱动、双向通信/网络接口 | 高效单向流式接口,带内低速反向通道 | 高效单向流式接口,带内低速反向通道 |

| HS时钟方法 | 嵌入式时钟 | DDR源同步时钟 | 嵌入式时钟 |

| 通道补偿 | 均衡化 | 数据偏斜控制,相对于时钟 | 编码以减少数据,计时频率 |

| 最小配置和引脚 | 各方向上1个通道,双单工,各通道上2个引脚(共4个) | 1个通道加时钟,单工,4个引脚 | 1个通道(三路),单工,3个引脚 |

| 最大发射器摆动幅度 | SA:250mV(峰值),LA:500mV(峰值) | LP:1300mV | (峰值),HS:360mV(峰值) |

| 各通道的数据速率(HS) | HS-G1:1.25,1.45 Gb/s,HS-G2:2.5,2.9 Gb/s,HS-G3:5.0,5.8 Gb/s;(线路速率为8b10b编码) | 80 Mbps至约2.5 Gbps(合计) | 80 Msym/s至2.5 Gsym/s乘以2.28 bits/sym,或最大5.7 Gbps(合计) |

| 各通道的数据速率(LS) | 10kbps – 600 Mbps | < 10 Mbps | < 10 Mbps |

| 各端口的带宽(3或4个通道) | 约为4.0 - 18.6 Gb/s(总带宽) | 每个4通道端口最大约为10 Gbps(合计) | 每个3通道端口最大约为17.1 Gbps(合计) |

| 每个端口的典型引脚(3或4个通道) | 10(4个通道TX,1个通道RX) | 10(4个通道,1个通道时钟)9(3个通道) | |

| 版本 | v4.1(2017年3月) | v2.1(2017年3月) | v1.2(2017年3月) |

以上是关于吃透MIPI接口,你必须了解它这三种PHY规范的区别的主要内容,如果未能解决你的问题,请参考以下文章