低频能不能采到高频?采样定理指导硬件设计

Posted 工程师看海

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了低频能不能采到高频?采样定理指导硬件设计相关的知识,希望对你有一定的参考价值。

原文来自公众号:工程师看海

香浓采样定理或者说奈奎斯特采样定理告诉我们,要以信号频率2倍以上的采样率对该信号进行采样,否则会出现频率混叠,比如对1Khz信号进行采样的话,采样率要高于2Ksps,

采样定理与傅里叶变换的具体原理请见往期文章:

https://www.dianyuan.com/eestar/article-1734.html

这东西看似简单,实际可以深度挖掘出很多内容,有助于指导我们进行硬件电路、软件算法的设计。

那么问题来了,如果面试官问:采样率低于信号的频率,我们可以采集到信号吗?你该怎么回答呢?

说可以采到不行,说不能采到也不行,这个问题里有隐藏的陷阱,稍不注意,就容易进坑,就中了面试官的套了。

今天咱们好好聊聊,看看采样定理与傅里叶变换如何指导我们设计硬件的。

-

能采的到?

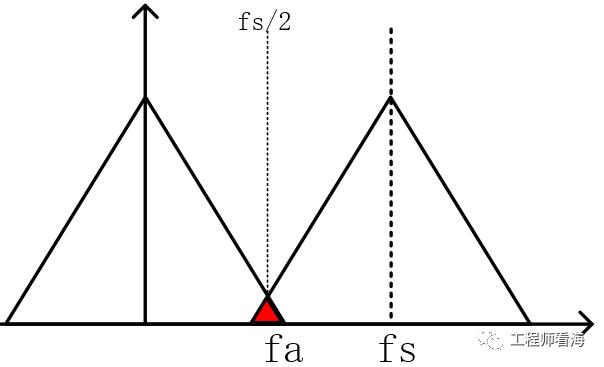

接着上文,采样定理除了告诉我们,采样率要超过信号带宽的2倍之外,还告诉我们,连续的周期信号,经过采样离散化后,会按照采样频率,进行周期性变化,比如下图,信号的带宽为fa,采样频率是fs,采样离散化后的结果,就是fa这个信号,在频谱上,以fs为频率周期进行周期性延拓,采样回的信号,就变成了0±fa、fs±fa、2fs±fa、3fs±fa。。。

重构采样后的信号最直接粗暴的方法,是将各个采样点依次连接,作为最终结果。

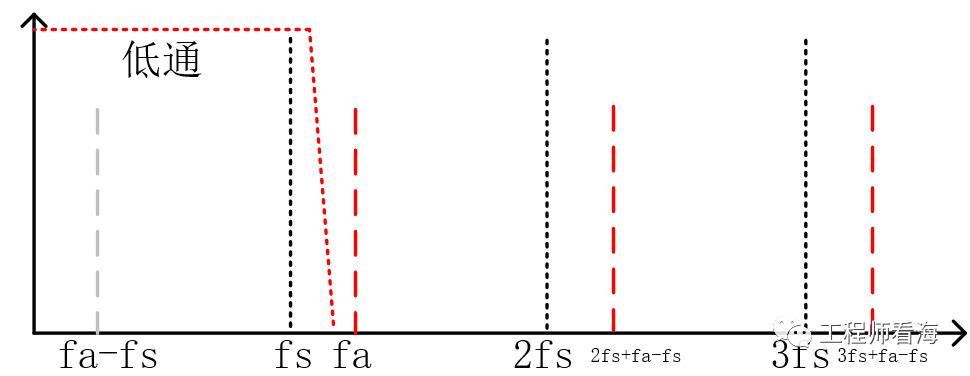

上面说的是正常采样或者过采样,下面我们低采样率的情况,为简化分析,我们只介绍单边频谱。按照前文理论的介绍,采样后的信号按照fs进行周期性延拓,比如下面在频谱上的介绍,采样率fs=900 sps,信号的频率fa=1000Hz,fs不满足刚开始提到的采样定理要求,而且fs<fa,采样后的信号按照fs进行周期延拓后,如下图所示,得到了0+(fa-fs)、fs+(fa-fs)、2fs+(fa-fs)、3fs+(fa-fs)。。。离散序列,在采样率fs频带内,1Khz原始信号就变成了100Hz。

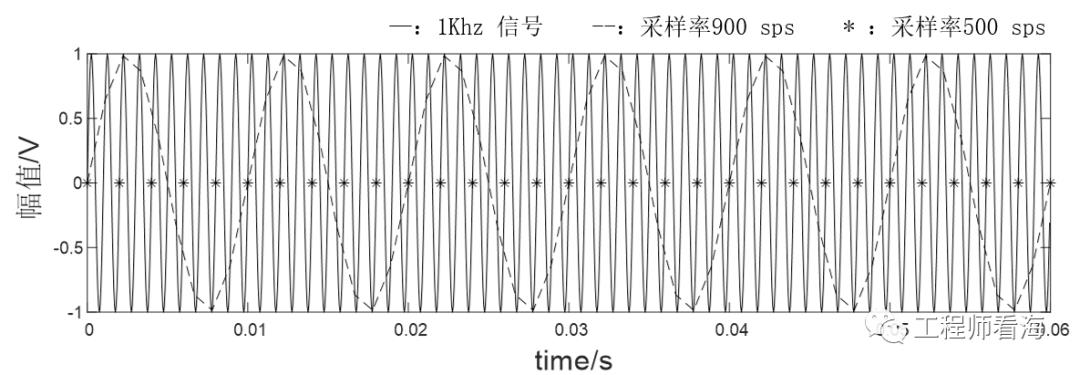

我们画出具体的波形图,会更容易理解,下图黑色实线是原始的1Khz信号,--虚线是以采样率900sps进行采样后的波形,*是以采样率500sps进行采样后的波形。可以看到,以低采样率对高频率信号进行采样,是采集到了信号的,只是会失真。同时,如果采样率小于信号频率,并且成整数倍,那么就采集不到交流信号,比如下图*曲线所示。

对上图信号进行FFT分析,--虚线是以采样率900sps进行采样后的波形,*是以采样率500sps进行采样后的波形。从频率来看,结果也是和上文分析一致的,实际上1000Hz的信号,900 sps采样后,变成了100Hz。

-

采集不到?

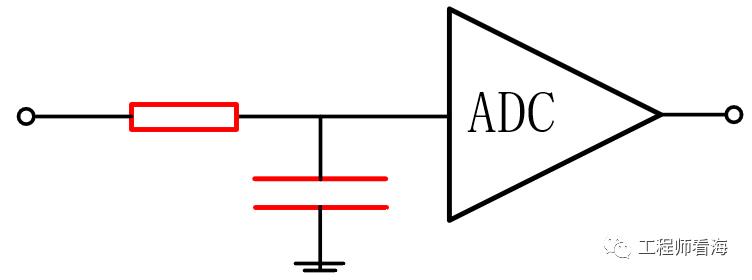

有同学说,为什么实际试验时低速采样率却采集不到高频信号?那是因为,信号在进入ADC之前,被进行了低通滤波,超过fs的高频成分已经被滤除了。

如下图所示,红色虚线之外的信号被抑制掉,因此本应该出现在fa-fs的频率成分就并没有出现,因此我们在设计电路时,有效的低通滤波器将会非常重要,这是指导硬件设计的重要原则之一。

-

怎么才能采到?

恰好我手里有一块某公司的采集卡,带宽是30Mhz,最大采样率是100Msps,那我的理解就是超过30Mhz的信号是采集不到的,应该是通过硬件、软件的手段抑制的,换句话说,硬件对30Mhz以内的信号衰减有限。

我们就基于我的猜测,以10Msps的速率采集11Mhz的信号,看看结果如何。

11Mhz的信号使用10Msps的采样率,那么根据前文的分析,采集的后的信号频率应该是1Mhz,时间波形见下图,FFT变换后明显看到1Mhz的频率成分,11Mhz的信号经过10Msps采样后变成了1Mhz,与前文的分析基本一致。

那么同样的,10Ksps采样率,采集30Khz的信号会有什么结果呢?根据前文的分析,整数倍关系时,应该采集不到,实际测试结果如下图,频谱上没有看到有效频率信息。

这里我可以再额外追加一个问题,我这个带宽30Mhz的设备,100Msps采样时,可以采集到110Mhz的信号吗?

-

应该怎么回答?

对于本文开篇的问题,如果面试官问:采样率低于信号的频率,我们可以采集到信号吗?你该怎么回答呢?

本来是想直接写答案的,后来想想,相比于结果,分析过程更重要,思路我已经写的很清晰了,归纳总结,就交给各位同学啦。

感谢点赞、分享、在看,让知识变得更简单

限时免费扫码进群,交流更多行业技术

推荐阅读▼

以上是关于低频能不能采到高频?采样定理指导硬件设计的主要内容,如果未能解决你的问题,请参考以下文章