RISC-V基本介绍

Posted 辣椒油li

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了RISC-V基本介绍相关的知识,希望对你有一定的参考价值。

文章目录

前言

RISC-V作为目前大火的开源指令集架构有着自己的独特魅力,本文将对其基本情况进行介绍,给大家留一个初步印象。

关于指令集的概念大家可以参看:什么是指令集架构ISA【从处理器谈起】

RISC-V念作 “risk-five”,代表着 Berkeley 所研发的第五代精简指令集。它是一款高质量、免许可证、开放的RISC ISA(指令集架构),是一套由RISC-V基金会维护的标准,适用于所有类型的计算系统。开源的RISC-V打破了ARM、x86架构的技术壁垒,便于开发者进行开发,目前国内外都在流行该架构。

一、命名规范

我们在实现基于RISCV架构的处理器时,根据应用场景的需要我们可以选择只实现架构中的部分指令,或者对于处理器的位宽有不同的选择。我们需要根据一些命名规范来对选择的RISCV子架构进行命名。以方便让用户马上了解这款处理器是基于怎样的子架构开发的。

RISCV ISA 命名格式:RV[###][abc……xyz]

- RV:用于标识 RISC-V 体系架构的前缀,即 RISC-V的缩写。

- [###]:32, 64, 128 用于标识处理器的位宽,也就是处理器的寄存器的宽度(单位为 bit)

- [abc…xyz]:标识该处理器支持的指令集模块集合。(指令模块的含义在下面会介绍)

如RV32IMA,RV64GC。

二、模块化ISA

RISC-V采用模块化的指令集,易于扩展、组装。

RISCV ISA = 1 个基本整数指令集(I) + 多个可选的扩展指令集

其中唯一强制要求实现的基础指令集,其他指令集都是可选的扩展模块。RISC-V 允许在实现中以可选的形式实现其他标准化和非标准化的指令集扩展。

RISC-V指令集模块包括

【注:特定组合“IMAFD”被称为 “通用(General)”组合,用英文字母 G 表示】

其他的扩展指令集还包括“B”标准扩展:位操作、“E”标准扩展:嵌入式、“H”特权态架构扩展:支持管理程序(Hypervisor)、“J”标准扩展:动态翻译语言、“L”标准扩展:十进制浮点、“N”标准扩展:用户态中断、“P”标准扩展:封装的单指令多数据(Packed-SIMD)指令、“Q”标准扩展:四精度浮点。

RV32I指令集有47条指令,能够满足现代操作系统运行的基本要求,47条指令按照功能可以分为如下几类。

- 整数运算指令:实现算术、逻辑、比较等运算。

- 分支转移指令:实现条件转移、无条件转移等运算,并且没有延迟槽。

- 加载存储指令:实现字节、半字、字的加载、存储操作,采用的都是寄存器相对寻址方式。

- 控制与状态寄存器访问指令:实现对系统控制与状态寄存器的原子读-写、原子读-修改、原子读-清零等操作。

- 系统调用指令:实现系统调用、调试等功能。

三、一些概念

1. 指令格式

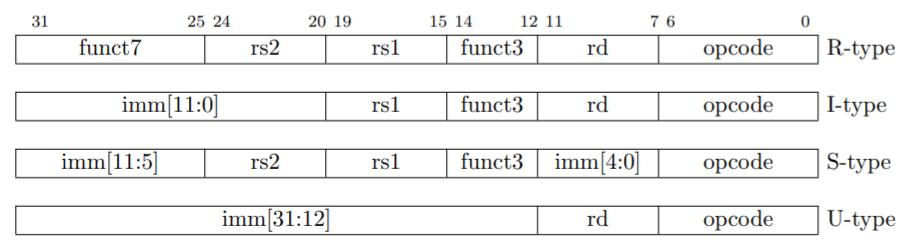

RISC-V具有非常工整的指令格式,所有基础指令的格式可以分为以下四种,指令长度为32位,在“C”标准扩展中,指令长度被压缩到16位:

规整的指令格式有利于处理器中的控制器对于二进制指令的解码。符合“越规整,越简单”的设计理念。

还有两种特殊的指令格式:SB型和UJ型,两种格式都只包含一条指令。

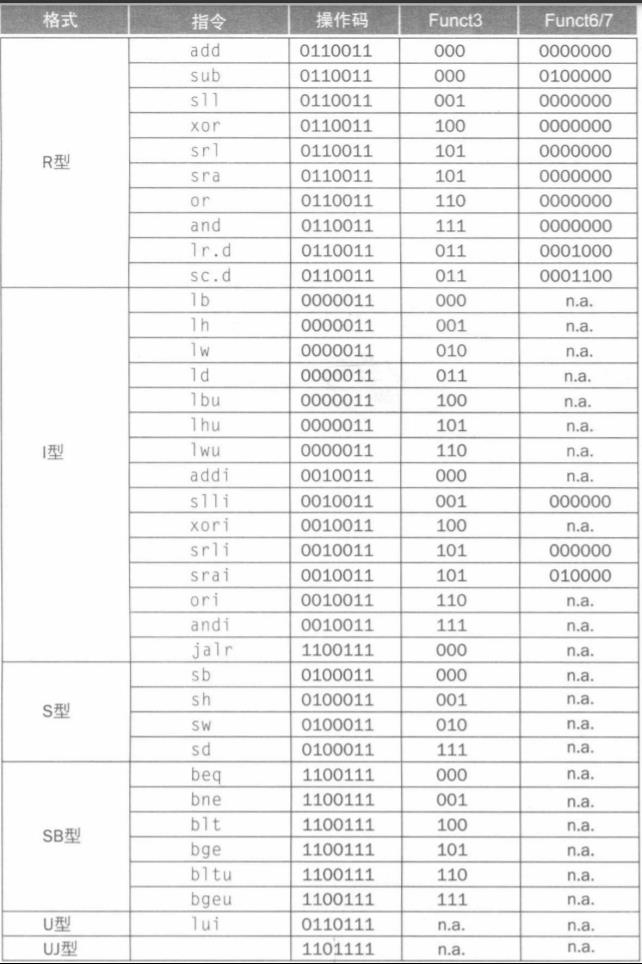

具体基本的RISCV的汇编语言和机器语言的对应表如下所示:

2. 寄存器

RISC-V 的 Unprivileged Specification 定义了 32 个通用寄存器以及一个 PC

-

对RV32I/RV64I/RV128I都一样

-

如果实现支持 F/D 扩展则需要额外支持 32个浮点(Float

Point)寄存器。 -

RV32E(E表示嵌入式系统)将32个通用寄存器缩减为16个。

每个寄存器具体编程时有特定的用途以及各自的别名,如下表:

3. 特权级别

RISC-V 的 Privileged Specification 定义了四个特权级别(privilege level),以下特权等级由高到低排列。

-

机器级别(M):RISC-V中hart(hardware thread,硬件线程,hart相当于核)可以执行的最高权限模式。在M模式下运行的hart对内存,I/O和一些对于启动和配置系统来说必要的底层功能有着完全的使用权。因此它是唯一所有标准RISC-V

处理器都必须实现的权限模式。实际上普通的RISC-V微控制器仅支持M模式。 -

超级监管者级别(H):为了支持虚拟机监视器。

-

监管者级别(S):旨在支持现代类Unix操作系统,如Linux,FreeBSD和Windows。

-

用户级别(U):用于运行应用程序,适用于安全嵌入式系统。

任何时候,一个RISC-V硬件线程(hart)是运行在某个特权级上的,这个特权级由CSR(control and status register,控制和状态寄存器)配置。

4. CSR(控制和状态寄存器)

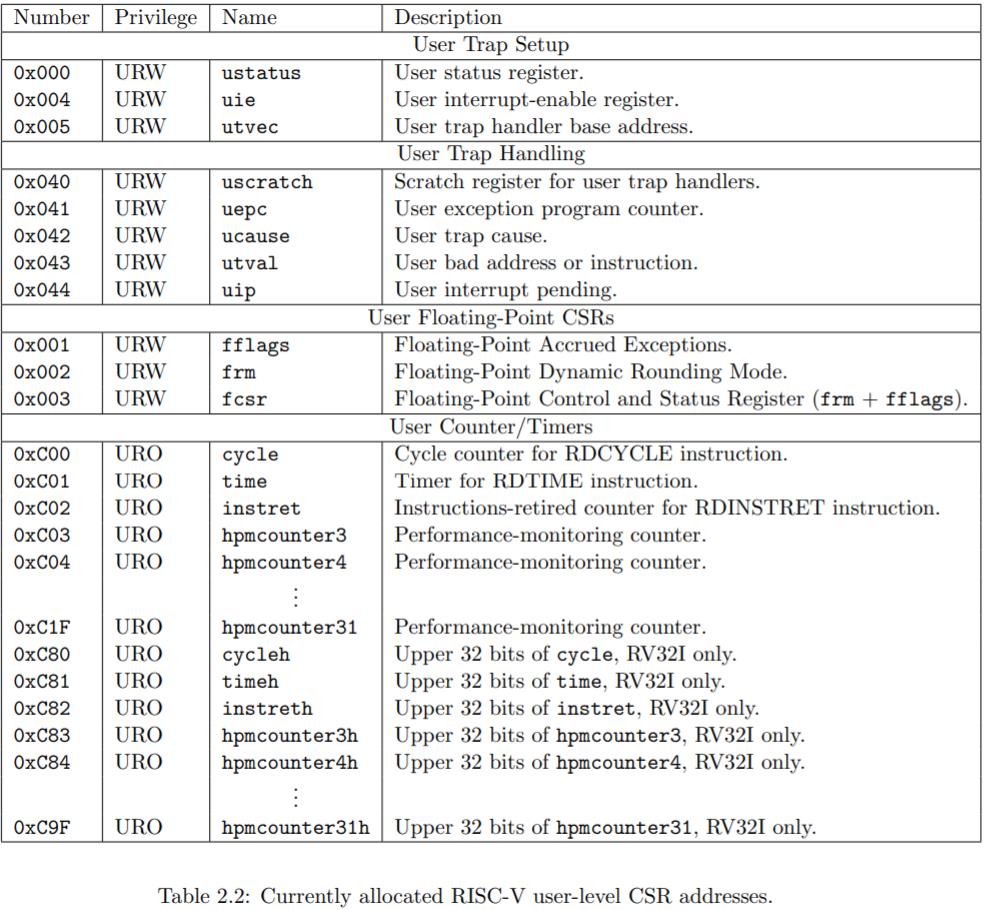

不同的特权级别下时分别对应各自的一套Registers(CSR),用于控制和获取相应特权级别下的处理器工作状态。在高级别的特权级别下,可以访问低级别的CSR,譬如Machine Level下可以访问Supervisor/User Level的CSR;但反之不可以。

标准RISC-V ISA设置了一个12位的编码空间(csr[11:0])作为CSR地址,可用于4096个CSR。根据约定,CSR地址的高4位(csr[11:8])用于编码CSR根据特权级读写的可访问性。其中最高2位(csr[11:10])指示这个寄存器是否是可以读/写(如只读是11)。后面2位(csr[9:8])指示了能够访问这个CSR所需要的最低特权级(如上表中,监管者模式是01)。

RISC-V定义了专门用于操作CSR的指令,且定义了特定的指令可以用于在不同特权级别之间进行切换(称为trap)。

一个hart(硬件线程)通常在U-mode下运行应用程序,直到某些自陷(trap,例如一个管理员调用或者一个定时器中断)强制切换到一个自陷处理函数(trap handler)。提升特权级别的自陷称为垂直自陷(vertical trap),而保持在同样特权级别的自陷称为水平自陷(horizontal trap)。

例如,下表是已被分配的用户级别(U)的CSR地址:

特权级别的切换对应于操作系统中用户态到内核态的切换,在内核态中才可以进行系统调用。

四、学习资料

1. 官方资料

在RISC-V官网上可以下载基础的ISA手册及特权手册:https://riscv.org/technical/specifications/

开发者在开发前需要阅读架构规范。官方的github主页是:https://github.com/riscv。

2. 开发参考

RISC-V只是定义了一套指令集架构规范,没有具体实现的代码,需要开发者根据该架构手册,通过使用硬件描述语言如VHDL编程来具体实现基于RISC-V的处理器,再移植到满足RISC-V需求的硬件平台(处理器芯片或开发板)上去。

使用RISC-V架构的同时,还要配套开发相应的编译器gcc以及调试器如openOCD。

同时RISC-V官方提供了兼容性测试代码,可以测试每一条指令的运行结果,验证开发者的核是否实现了RISC-V规范。

目前基于RISC-V架构的开源处理器有很多,既有标量处理器Rocket,也有超标量处理器BOOM,还有面向嵌入式领域的Z-scale、PicoRV32等。具体有哪些开源处理器项目可以参见:RISC-V架构总结1,开源代码在github上也有很多。

可供学习的一个简单RISC-V核是tinyrisc。该项目实现的是一个单核32位的小型RISC-V处理器核,采用verilog语言编写

总结

RISCV由于其开源性,被大家广泛使用,我们在需要特定的处理器时也可以采用RISCV架构自行开发。同时RISCV具有低功耗的特点,适合嵌入式开发。

以上是关于RISC-V基本介绍的主要内容,如果未能解决你的问题,请参考以下文章