Doherty经典论文

Posted 硬件老钢丝

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了Doherty经典论文相关的知识,希望对你有一定的参考价值。

论文:The Doherty Power Ampifier 2006 (偏置改变包络阻抗,提高线性度)

背景

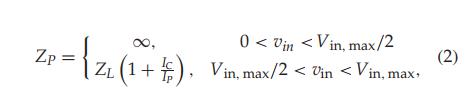

由于基站功率放大器由于后退操作而产生低效率,效率增强技术变得非常重要。在宽瞬时带宽范围内实现高效率、线性化的基站功率放大器的设计技术已成为研究的热点,在这篇文章中,我们证明Doherty放大器能够满足基站功率放大器的严格要求。我们解释了工作原理,包括线性和效率的改善,以及放大器的基本电路配置。本文还介绍了跨宽带宽操作和提高线性度的先进设计方法。结果表明,Doherty放大器是一种宽带宽、效率高、线性度好的基站功率放大器

论文细节

(一)Doherty Amplifier Operation

Doherty是1936年提出的,最初的Doherty放大器由两个管放大器和一个阻抗反相网络组成。

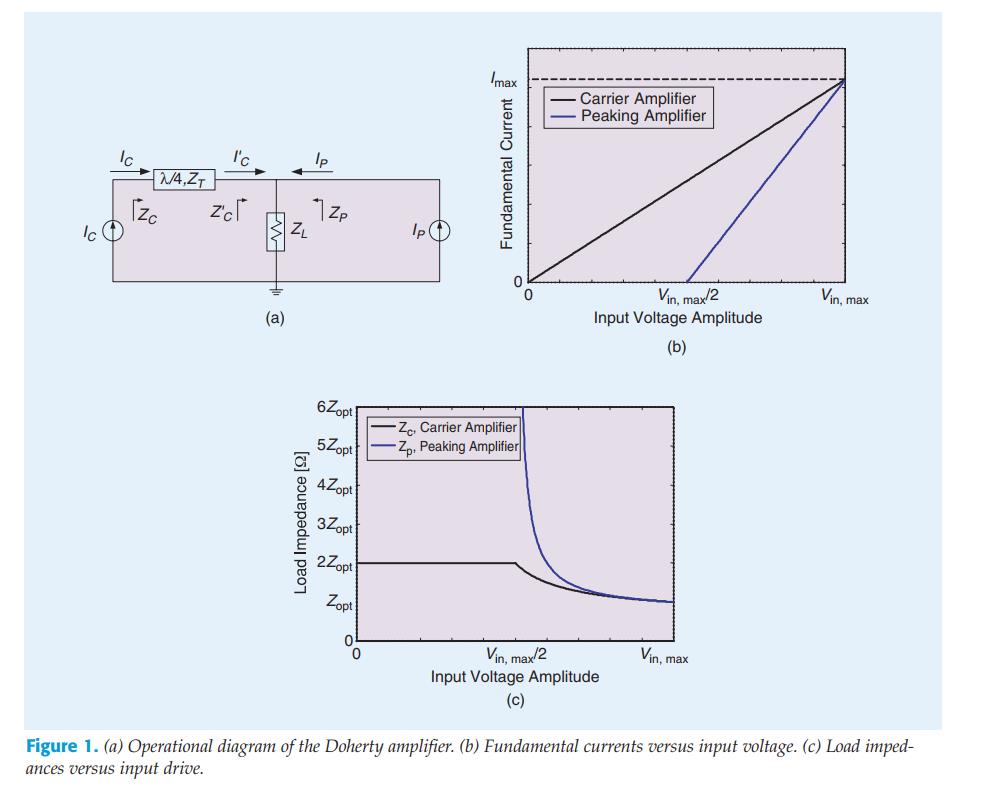

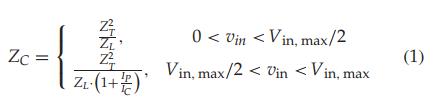

Doherty功放是由载波功放和峰值功放构成的,输出负载通过阻抗逆变器(四分之一波长传输线)连接到载波放大器,并直接连接到峰值放大器,两个功放都等效为电流源,并且假设每个电流源和输入电压信号成线性比例,工作在AB类或者B类,其谐波视为短路。Doherty功放的基本原理大家可以参照我ADS进行验证的一篇帖子,这里就不进行理论分析了,直接公式表述。

公式看出,在低功率输入时,只有载波功放工作,峰值功放处于关闭状态,载波功放的负载为传统负载的2倍,因此,载波放大器在输入电压(Vin,max)/2处达到饱和状态,因为最大基电流摆幅为一半,最大电压摆幅达到Vdc。结果,这时的最大输出功率为载波功放饱和功率的一半,也就是整个DPA的6dB回退处,此时会出现第一个最大效率点。

在大功率输出水平下,峰值功放导通,它的电流水平在负载调制中起到了很重要的作用,假设峰值功放的gm是载波功放的2倍,峰值放大器的电流和电压波动与输入电压水平成比例增加,电压波动仅在最大输入电压时达到Vdc的最大电压波动,其负载变化从上面的图中可以看出。

Doherty放大器在最大输入电压下的效率等于载波放大器的最大效率。当峰值放大器和载波放大器的尺寸相同时,通常情况下,两个放大器的gm是相同的,峰值放大器不能完全打开,因此功率性能下降。

从基本的工作原理出发,我们探索了Doherty放大器,与传统的AB类放大器相比,它在整个功率范围内提供了更高的效率。由此产生的Doherty放大器可以解决在大的PAR信号下保持高效率的问题。

(二)Linearity of the Doherty Amplifier

Doherty放大器的线性度比AB类放大器的线性度更复杂。AB类偏置载波放大器在低功率水平的负载阻抗是常规功放阻抗的两倍大,载波放大器的高阻抗补偿了由于输入功率划分造成的低增益特性。在高功率水平,两个放大器使用正常负载阻抗产生全功率,均衡功率增益。在低功率区域,放大器的线性完全由载波放大器决定。因此,即使负载阻抗很高,载波放大器也应该是高度线性的

在高功率水平下,采用适当的栅极偏差对两个放大器进行谐波抵消,从而改善了放大器的线性度。

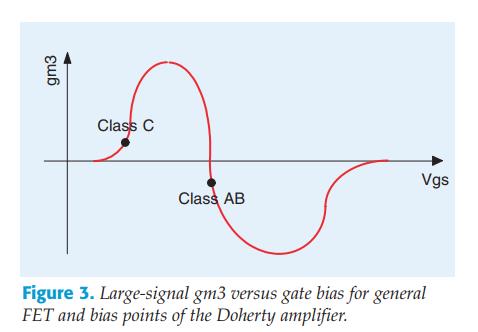

如图三所示,表明了不同类型功放三次谐波产生系数gm3。

根据各放大器的增益特性,C类偏置峰值放大器的后期增益扩展补偿了AB类载波放大器的增益压缩。

因此,基于负载调制技术的Doherty放大器能够比传统的AB类功率放大器提供更多的线性输出功率。

The third-order intermodulation (IM3) level from the carrier amplifier increasesand the phase of the IM3 decreases because the gain ofthe carrier amplifier is compressed. In contrast, when the gain of the peaking amplifier is expanded, both the IM3 level and phase increase. (文章这段我的理解是,对于载波功放他在大信号的时候最后会有一个增益压缩,导致IM3相位为负,而峰值功放一直呈增益扩张状态,所以IM3相位为正。)

为了补偿两个功放的IM3,两个功放必须是180度相位差,但是振幅一致,所以峰值功放的设计适当,用来抵消载波放大器的谐波。

(三)The Circuit Configuration of Doherty Amplifier

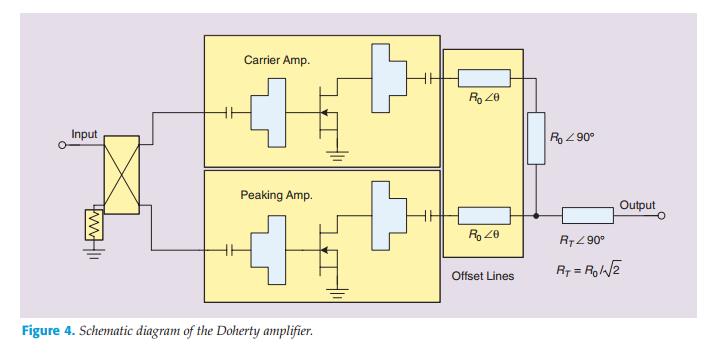

下面是传统DPA的结构图,这里不做过多解释,在更原始的论文以及很多中文论文都有很详细的论述。

(四)Advanced Design Methods for the Doherty Amplifier

Doherty可以提高效率和线性度,在本节中,我们将解释一些典型问题 Doherty放大器,并提出了解决它们的方法。

由于峰值放大器偏置低于载波放大器,峰值放大器在最大输入驱动处的电流水平不能达到最大允许电流水平。因此,两个放大器的负载阻抗不能完全调制到最优阻抗,Zopt,它们大于最优值。结果,传统的Doherty放大器严重饱和,线性和功率都下降。由于记忆效应,在一个宽带范围内,提高DPA的线性度是很困难的。

针对宽带宽、高线性度、高功率的应用,我们提出了以下三种设计方法:

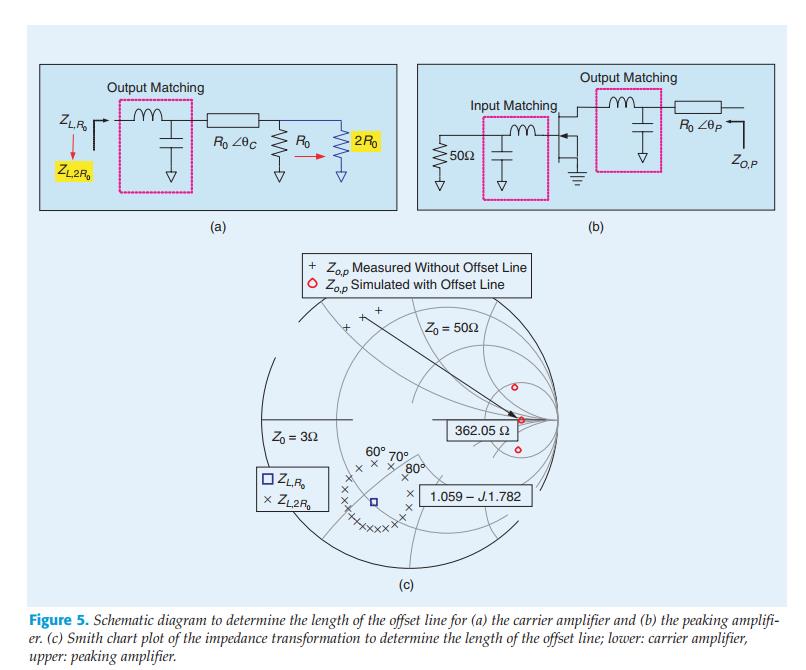

1)非均匀功率驱动,对峰值放大器施加更大的功率,可以充分打开峰值放大器,并对负载阻抗进行最佳调节。因此,不均匀功率驱动的放大器比相同输入功率驱动的放大器运行更线性,产生更多的功率。

2)由于负载调制不当,两个放大器的功率匹配电路应适当设计为低负载阻抗,以提高线性度。由于峰值放大器的偏置点较低,因此峰值放大器的功率匹配电路应设计为比载波放大器具有更低的负载阻抗。此外,两个放大器的匹配电路应单独优化,以增强在宽带宽的功率范围内的IM抵消。

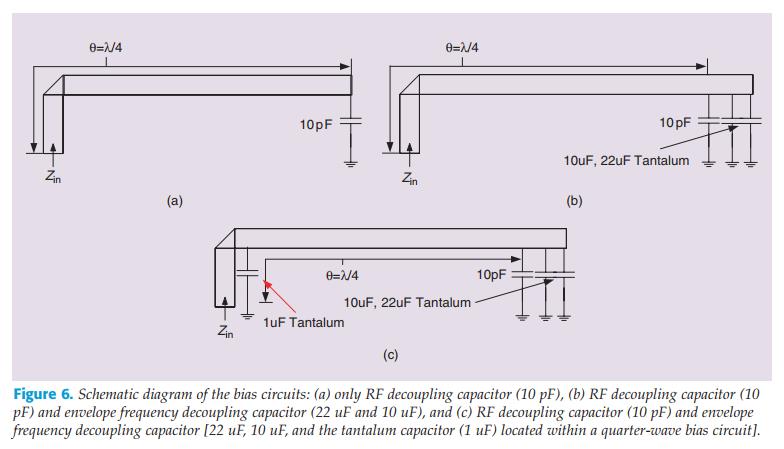

3)偏置电路应该被设计去最小化记忆效应。由于记忆效应带来的上、下杂散辐射的不同,以Doherty放大器和PD等谐波消除为重点的线性化技术被限制在一个较低的消除极限。偏置电路不应该有任何包络阻抗的频散,以减少记忆效应。为了减少记忆效应,使用四分之一波偏置线和每个频率的去耦电容来优化偏置电路。钽电容插入四分之一波偏压线内,以满足包络频率的要求。此外,两个放大器的偏差适当调整,以保持优化的线性和效率。

(五)Bias Circuit Test to Reduce the Memory Effects

不同带宽对记忆效果的影响主要是ACLR或互调失真(IMD)不对称和带宽依赖的相邻信道泄漏比(ACLR)或IMD特征,为了减少这些效应或记忆效应,应降低偏置电路的负载阻抗,使其缩短包络频率电压分量或保持在相同的值。

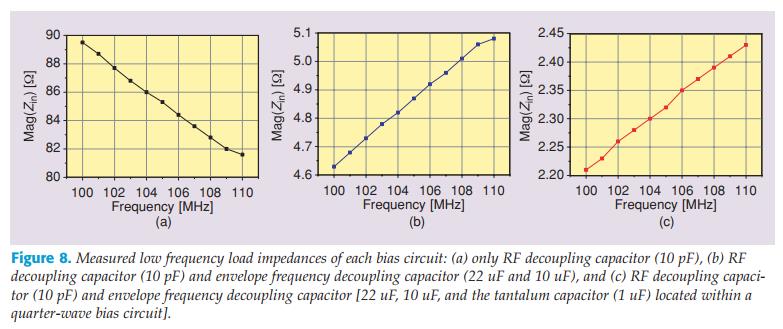

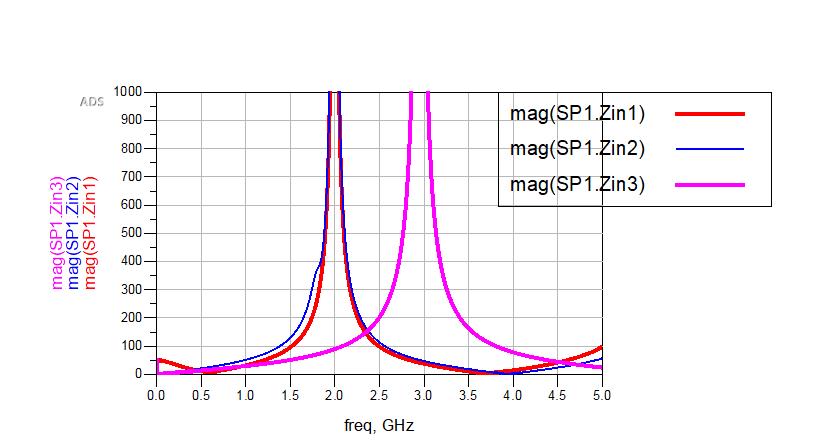

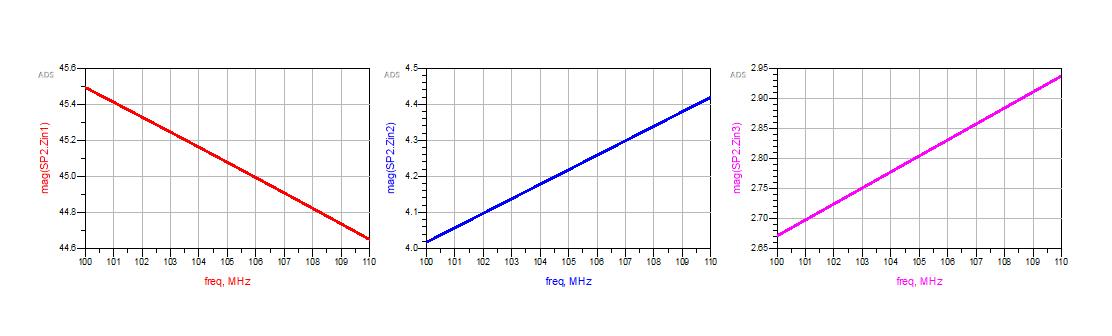

设计了几种偏置电路,来减少记忆效应。由于无法测试DC-20MHz的包络阻抗,所以通过测量100MHz-5GHz的负载阻抗,从这些测试结果来模拟偏置电路的包络频率负载阻抗。

10UF和22UF为包络去耦电容,即使这种情况下的包络负载阻抗非常小,功率放大器有严重的记忆效应。造成这种结果的一个原因是,由于大功率放大器的负载阻抗非常小,很难缩短包络频率电压分量。

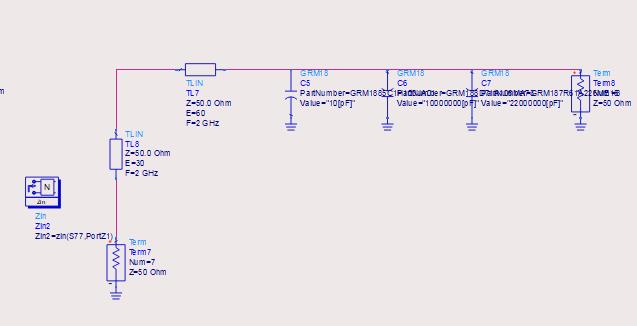

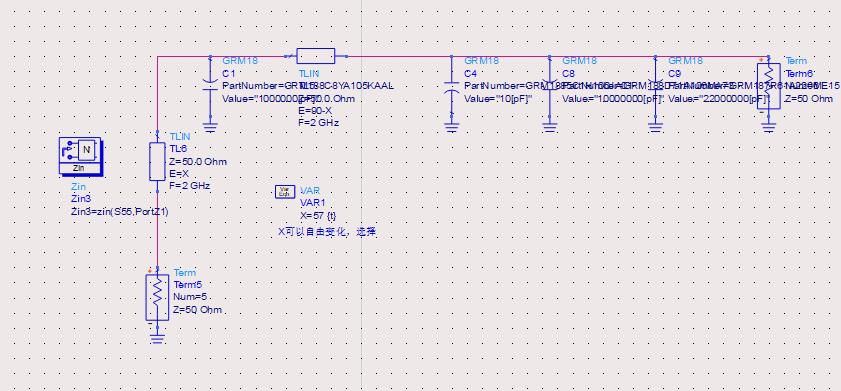

为了减小记忆效应,应进一步减小偏置电路的负载阻抗。因此,文章提出了射频去耦电容的偏置电路优化方法(10 pF)和包络频率去耦电容[22 uF, 10 uF,和位于四分之一波偏置电路中的钽电容(1 uF)]。

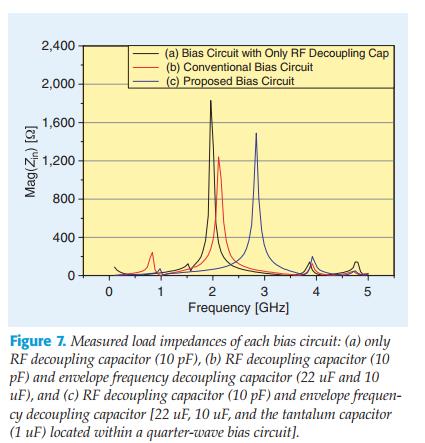

和图7©和图8©显示了比一般偏置方案在低频时更小的包络负载阻抗和更低的负载阻抗变化。然而,如图7©所示,位于四分之一波偏压线内的钽电容降低了射频阻抗,因此,我们需要对偏置电路和匹配电路进行优化。结果表明,所提出的偏置电路优化方法比传统偏置电路方法更有效地降低了记忆效应,降低了ACLR的不对称性

下面是文章论文的验证过程。

位于四分之一波偏压线内对于减小记忆效应特别重要,即使这些电容器降低了射频阻抗,我们对偏置电路和匹配电路进行了优化。

因此,偏置电路成为有源匹配电路,在所有平均输出功率上,ACLR与上下ACLR的偏置电路优化的差值减小到2 dB以下。(这些图自己看论文吧)

验证

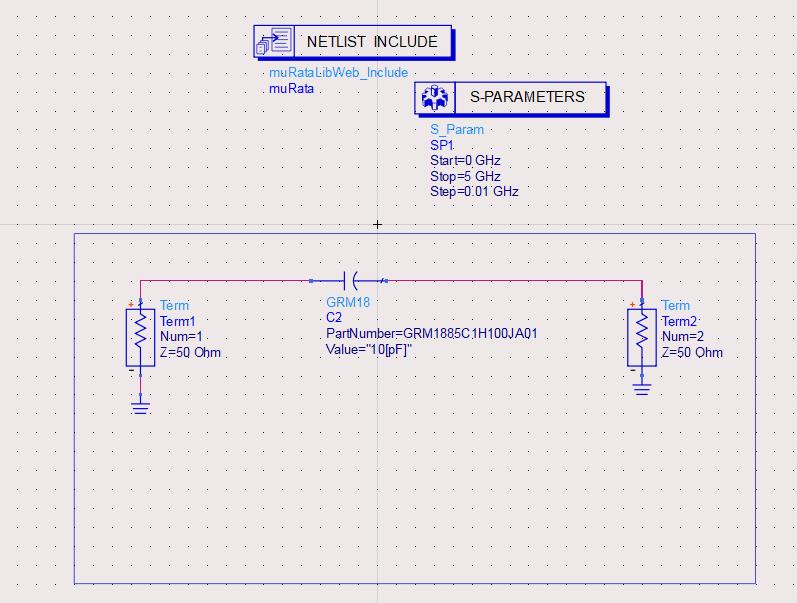

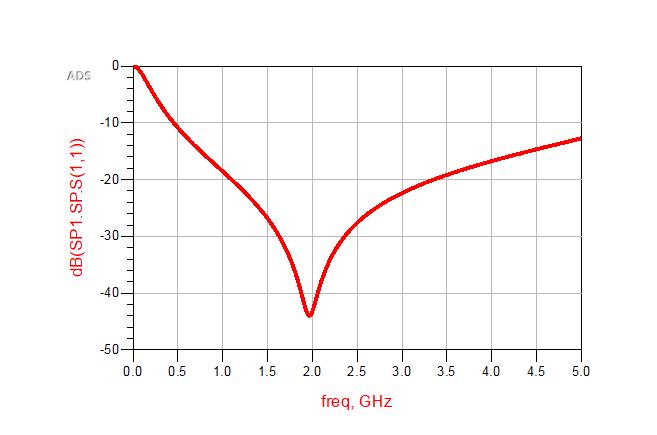

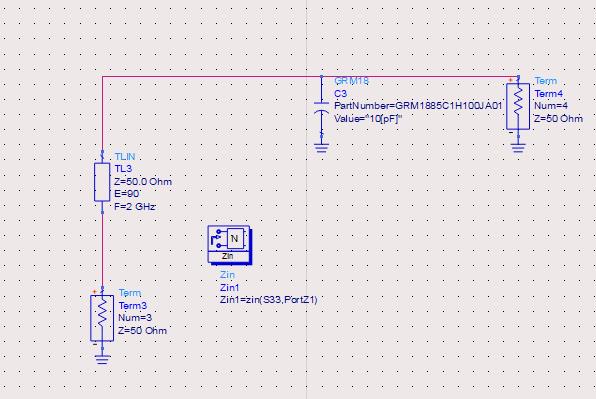

这里我也用ADS进行了验证偏置电路的阻抗,线性度没有去验证。

去耦电容选定:谐振在2GHz

以上是关于Doherty经典论文的主要内容,如果未能解决你的问题,请参考以下文章