zedboard在PL端实现流水灯

Posted xadc

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了zedboard在PL端实现流水灯相关的知识,希望对你有一定的参考价值。

开发环境:win 10

开发平台:vivado 2015.4

目的:在zynq7000的基础上以zedboard为硬件平台实现流水灯,zynq7000系列有一个硬件FPGA和两个ARM-A9硬核,FPGA部分被称为PL(Programmable Logic),不使用SDK来进行实验。

流程:

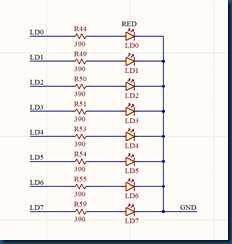

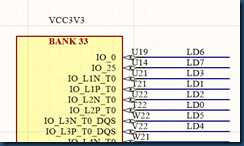

正式开始建立工程和编写代码之前我们需要先看懂原理图,下面我们看一下zedboard的LED所对应的原理图、

这是LED部分的原理图,在找到对应的FPGA引脚

LD0对应的T22

LD1对应的T21

LD2对应的U22

LD3对应的U21

LD4对应的V22

LD5对应的W22

LD6对应的U19

LD7对应的U14

1:使用vivado建立工程,编写Verilog代码。

打开vivado 软件,见下图。

一直下一步建立一个RTL PROject,

然后一直下一步直到选择板子的一步,选择board-zedboard,点击next->finish.

到现在为止工程就建立完成了

现在我们添加vrilog的代码了

右键选择add sources ,然后选择 add design source。

选择create file

插入一下代码

module PL_LED_TEST(

input clk,

input rst,

output reg [7:0]LED

);

reg [31:0] cntr ;

always @ (posedge clk)if ( rst ) cntr<=0;else cntr <=cntr+1 ;

always @ (posedge clk)LED <= cntr[24:17] ;

endmodule

编写约束文件,就是约束管脚顺序与添加Verilog 顺序一样,需要选择的是constrs

set_property PACKAGE_PIN Y9 [get_ports {clk}]

set_property iosTANDARD LVCMOS33 [get_ports {clk}]

set_property PACKAGE_PIN N15 [get_ports {rst}]

set_property IOSTANDARD LVCMOS18 [get_ports {rst}]

set_property PACKAGE_PIN T22 [get_ports {LED[0]}]

set_property IOSTANDARD LVCMOS33 [get_ports {LED[0]}]

set_property PACKAGE_PIN T21 [get_ports {LED[1]}]

set_property IOSTANDARD LVCMOS33 [get_ports {LED[1]}]

set_property PACKAGE_PIN U22 [get_ports {LED[2]}]

set_property IOSTANDARD LVCMOS33 [get_ports {LED[2]}]

set_property PACKAGE_PIN U21 [get_ports {LED[3]}]

set_property IOSTANDARD LVCMOS33 [get_ports {LED[3]}]

set_property PACKAGE_PIN V22 [get_ports {LED[4]}]

set_property IOSTANDARD LVCMOS33 [get_ports {LED[4]}]

set_property IOSTANDARD LVCMOS33 [get_ports {LED[5]}]

set_property PACKAGE_PIN W22 [get_ports {LED[5]}]

set_property PACKAGE_PIN U19 [get_ports {LED[6]}]

set_property IOSTANDARD LVCMOS33 [get_ports {LED[6]}]

set_property IOSTANDARD LVCMOS33 [get_ports {LED[7]}]

set_property PACKAGE_PIN U14 [get_ports {LED[7]}]

然后点击右侧的

生成BIT流文件

2:连接目标板。

点击

选择autoconnect

3:下载观察实验现象。

观察实验现象,这是一个按照数位一直增加的,如果看不清,可以改变对应的位数

以上是关于zedboard在PL端实现流水灯的主要内容,如果未能解决你的问题,请参考以下文章

实现基于RS-485通信和Modbus协议的远程智能消防监测系统