为啥我的quartus的管脚分配了但还是看不见啊?我想把分配好的管脚显示出来

Posted

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了为啥我的quartus的管脚分配了但还是看不见啊?我想把分配好的管脚显示出来相关的知识,希望对你有一定的参考价值。

参考技术A 软件有的时候有bug,你关闭一下,然后再打开就会有了。你进入pin plan里面看,如果都分配好了,就没问题了。追问点进去看是有的,就是无法自动显示,让我感觉很不爽啊

追答不爽也没办法,其实进入pin plan观察是最准确的

本回答被提问者采纳 参考技术B 保存编译,在pin里看看,一般它是自动保存的!追问点进去看是有的,就是无法自动显示,让我感觉很不爽啊

参考技术C 编译一下看看追问点进去看是有的,就是无法自动显示,让我感觉很不爽啊

追答编译之后不显示吗

追问恩恩 也不显示

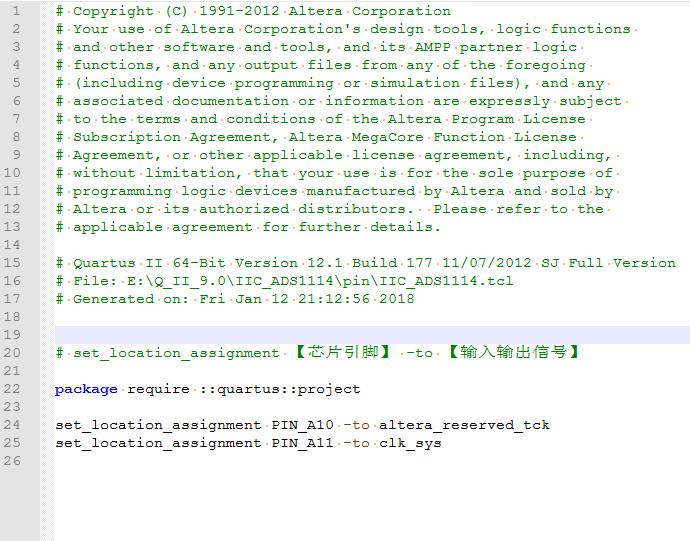

Quartus II管脚批量分配文件(.tcl)格式

1 package require ::quartus::project 2 3 set_location_assignment PIN_E1 -to clk 4 set_location_assignment PIN_A11 -to data[0] 5 set_location_assignment PIN_A12 -to data[1]

范例:

1 # 2 # Clock / Reset 3 # 4 set_location_assignment PIN_J15 -to rst_n_pad_i 5 set_instance_assignment -name IO_STANDARD "3.3-V LVTTL" -to rst_n_pad_i 6 set_location_assignment PIN_E1 -to btn_n_pad_i 7 set_instance_assignment -name IO_STANDARD "3.3-V LVTTL" -to btn_n_pad_i 8 set_location_assignment PIN_R8 -to sys_clk_pad_i 9 set_instance_assignment -name IO_STANDARD "3.3-V LVTTL" -to sys_clk_pad_i 10 11 # 12 # UART0: RX <-> GPIO_2[0] (Pin 5, bottom header) 13 # TX <-> GPIO_2[1] (Pin 6, bottom header) 14 # 15 set_location_assignment PIN_A14 -to uart0_srx_pad_i 16 set_instance_assignment -name IO_STANDARD "3.3-V LVTTL" -to uart0_srx_pad_i 17 set_location_assignment PIN_B16 -to uart0_stx_pad_o 18 set_instance_assignment -name IO_STANDARD "3.3-V LVTTL" -to uart0_stx_pad_o 19 20 # 21 # I2C0: Connected to the EEPROM and Accelerometer 22 # 23 set_location_assignment PIN_F2 -to i2c0_scl_io 24 set_instance_assignment -name IO_STANDARD "3.3-V LVTTL" -to i2c0_scl_io 25 set_location_assignment PIN_F1 -to i2c0_sda_io 26 set_instance_assignment -name IO_STANDARD "3.3-V LVTTL" -to i2c0_sda_io 27 28 # 29 # Accelerometer specific lines 30 # 31 set_location_assignment PIN_M2 -to accelerometer_irq_i 32 set_instance_assignment -name IO_STANDARD "3.3-V LVTTL" -to accelerometer_irq_i 33 set_location_assignment PIN_G5 -to accelerometer_cs_o 34 set_instance_assignment -name IO_STANDARD "3.3-V LVTTL" -to accelerometer_cs_o 35 36 # 37 # I2C1: sda <-> GPIO_2[6] (Pin 11, bottom header) 38 # scl <-> GPIO_2[7] (Pin 12, bottom header) 39 # 40 set_location_assignment PIN_D15 -to i2c1_sda_io 41 set_instance_assignment -name IO_STANDARD "3.3-V LVTTL" -to i2c1_sda_io 42 set_location_assignment PIN_D14 -to i2c1_scl_io 43 set_instance_assignment -name IO_STANDARD "3.3-V LVTTL" -to i2c1_scl_io 44 45 # 46 # SPI0: Connected to the EPCS 47 # 48 set_global_assignment -name RESERVE_FLASH_NCE_AFTER_CONFIGURATION "USE AS REGULAR IO" 49 set_global_assignment -name RESERVE_DATA0_AFTER_CONFIGURATION "USE AS REGULAR IO" 50 set_global_assignment -name RESERVE_DATA1_AFTER_CONFIGURATION "USE AS REGULAR IO" 51 set_global_assignment -name RESERVE_DCLK_AFTER_CONFIGURATION "USE AS REGULAR IO" 52 set_location_assignment PIN_C1 -to spi0_mosi_o 53 set_instance_assignment -name IO_STANDARD "3.3-V LVTTL" -to spi0_mosi_o 54 set_location_assignment PIN_H2 -to spi0_miso_i 55 set_instance_assignment -name IO_STANDARD "3.3-V LVTTL" -to spi0_miso_i 56 set_location_assignment PIN_H1 -to spi0_sck_o 57 set_instance_assignment -name IO_STANDARD "3.3-V LVTTL" -to spi0_sck_o 58 set_location_assignment PIN_D2 -to spi0_ss_o 59 set_instance_assignment -name IO_STANDARD "3.3-V LVTTL" -to spi0_ss_o 60 61 # 62 # SPI1: Connected to the AD converter 63 # 64 set_location_assignment PIN_B10 -to spi1_mosi_o 65 set_instance_assignment -name IO_STANDARD "3.3-V LVTTL" -to spi1_mosi_o 66 set_location_assignment PIN_A9 -to spi1_miso_i 67 set_instance_assignment -name IO_STANDARD "3.3-V LVTTL" -to spi1_miso_i 68 set_location_assignment PIN_B14 -to spi1_sck_o 69 set_instance_assignment -name IO_STANDARD "3.3-V LVTTL" -to spi1_sck_o 70 set_location_assignment PIN_A10 -to spi1_ss_o 71 set_instance_assignment -name IO_STANDARD "3.3-V LVTTL" -to spi1_ss_o 72 73 # 74 # SPI2: MOSI <-> GPIO_2[2] (Pin 7, bottom header) 75 # MISO <-> GPIO_2[3] (Pin 8, bottom header) 76 # SCK <-> GPIO_2[4] (Pin 9, bottom header) 77 # SS <-> GPIO_2[5] (Pin 10, bottom header) 78 # 79 set_location_assignment PIN_C14 -to spi2_mosi_o 80 set_instance_assignment -name IO_STANDARD "3.3-V LVTTL" -to spi2_mosi_o 81 set_location_assignment PIN_C16 -to spi2_miso_i 82 set_instance_assignment -name IO_STANDARD "3.3-V LVTTL" -to spi2_miso_i 83 set_location_assignment PIN_C15 -to spi2_sck_o 84 set_instance_assignment -name IO_STANDARD "3.3-V LVTTL" -to spi2_sck_o 85 set_location_assignment PIN_D16 -to spi2_ss_o 86 set_instance_assignment -name IO_STANDARD "3.3-V LVTTL" -to spi2_ss_o 87 88 # 89 # SDRAM 90 # 91 set_location_assignment PIN_P2 -to sdram_a_pad_o[0] 92 set_instance_assignment -name IO_STANDARD "3.3-V LVTTL" -to sdram_a_pad_o[0] 93 set_location_assignment PIN_N5 -to sdram_a_pad_o[1] 94 set_instance_assignment -name IO_STANDARD "3.3-V LVTTL" -to sdram_a_pad_o[1] 95 set_location_assignment PIN_N6 -to sdram_a_pad_o[2] 96 set_instance_assignment -name IO_STANDARD "3.3-V LVTTL" -to sdram_a_pad_o[2] 97 set_location_assignment PIN_M8 -to sdram_a_pad_o[3] 98 set_instance_assignment -name IO_STANDARD "3.3-V LVTTL" -to sdram_a_pad_o[3] 99 set_location_assignment PIN_P8 -to sdram_a_pad_o[4] 100 set_instance_assignment -name IO_STANDARD "3.3-V LVTTL" -to sdram_a_pad_o[4] 101 set_location_assignment PIN_T7 -to sdram_a_pad_o[5] 102 set_instance_assignment -name IO_STANDARD "3.3-V LVTTL" -to sdram_a_pad_o[5] 103 set_location_assignment PIN_N8 -to sdram_a_pad_o[6] 104 set_instance_assignment -name IO_STANDARD "3.3-V LVTTL" -to sdram_a_pad_o[6] 105 set_location_assignment PIN_T6 -to sdram_a_pad_o[7] 106 set_instance_assignment -name IO_STANDARD "3.3-V LVTTL" -to sdram_a_pad_o[7] 107 set_location_assignment PIN_R1 -to sdram_a_pad_o[8] 108 set_instance_assignment -name IO_STANDARD "3.3-V LVTTL" -to sdram_a_pad_o[8] 109 set_location_assignment PIN_P1 -to sdram_a_pad_o[9] 110 set_instance_assignment -name IO_STANDARD "3.3-V LVTTL" -to sdram_a_pad_o[9] 111 set_location_assignment PIN_N2 -to sdram_a_pad_o[10] 112 set_instance_assignment -name IO_STANDARD "3.3-V LVTTL" -to sdram_a_pad_o[10] 113 set_location_assignment PIN_N1 -to sdram_a_pad_o[11] 114 set_instance_assignment -name IO_STANDARD "3.3-V LVTTL" -to sdram_a_pad_o[11] 115 set_location_assignment PIN_L4 -to sdram_a_pad_o[12] 116 set_instance_assignment -name IO_STANDARD "3.3-V LVTTL" -to sdram_a_pad_o[12] 117 118 set_location_assignment PIN_G2 -to sdram_dq_pad_io[0] 119 set_instance_assignment -name IO_STANDARD "3.3-V LVTTL" -to sdram_dq_pad_io[0] 120 set_location_assignment PIN_G1 -to sdram_dq_pad_io[1] 121 set_instance_assignment -name IO_STANDARD "3.3-V LVTTL" -to sdram_dq_pad_io[1] 122 set_location_assignment PIN_L8 -to sdram_dq_pad_io[2] 123 set_instance_assignment -name IO_STANDARD "3.3-V LVTTL" -to sdram_dq_pad_io[2] 124 set_location_assignment PIN_K5 -to sdram_dq_pad_io[3] 125 set_instance_assignment -name IO_STANDARD "3.3-V LVTTL" -to sdram_dq_pad_io[3] 126 set_location_assignment PIN_K2 -to sdram_dq_pad_io[4] 127 set_instance_assignment -name IO_STANDARD "3.3-V LVTTL" -to sdram_dq_pad_io[4] 128 set_location_assignment PIN_J2 -to sdram_dq_pad_io[5] 129 set_instance_assignment -name IO_STANDARD "3.3-V LVTTL" -to sdram_dq_pad_io[5] 130 set_location_assignment PIN_J1 -to sdram_dq_pad_io[6] 131 set_instance_assignment -name IO_STANDARD "3.3-V LVTTL" -to sdram_dq_pad_io[6] 132 set_location_assignment PIN_R7 -to sdram_dq_pad_io[7] 133 set_instance_assignment -name IO_STANDARD "3.3-V LVTTL" -to sdram_dq_pad_io[7] 134 set_location_assignment PIN_T4 -to sdram_dq_pad_io[8] 135 set_instance_assignment -name IO_STANDARD "3.3-V LVTTL" -to sdram_dq_pad_io[8] 136 set_location_assignment PIN_T2 -to sdram_dq_pad_io[9] 137 set_instance_assignment -name IO_STANDARD "3.3-V LVTTL" -to sdram_dq_pad_io[9] 138 set_location_assignment PIN_T3 -to sdram_dq_pad_io[10] 139 set_instance_assignment -name IO_STANDARD "3.3-V LVTTL" -to sdram_dq_pad_io[10] 140 set_location_assignment PIN_R3 -to sdram_dq_pad_io[11] 141 set_instance_assignment -name IO_STANDARD "3.3-V LVTTL" -to sdram_dq_pad_io[11] 142 set_location_assignment PIN_R5 -to sdram_dq_pad_io[12] 143 set_instance_assignment -name IO_STANDARD "3.3-V LVTTL" -to sdram_dq_pad_io[12] 144 set_location_assignment PIN_P3 -to sdram_dq_pad_io[13] 145 set_instance_assignment -name IO_STANDARD "3.3-V LVTTL" -to sdram_dq_pad_io[13] 146 set_location_assignment PIN_N3 -to sdram_dq_pad_io[14] 147 set_instance_assignment -name IO_STANDARD "3.3-V LVTTL" -to sdram_dq_pad_io[14] 148 set_location_assignment PIN_K1 -to sdram_dq_pad_io[15] 149 set_instance_assignment -name IO_STANDARD "3.3-V LVTTL" -to sdram_dq_pad_io[15] 150 151 set_location_assignment PIN_R6 -to sdram_dqm_pad_o[0] 152 set_instance_assignment -name IO_STANDARD "3.3-V LVTTL" -to sdram_dqm_pad_o[0] 153 set_location_assignment PIN_T5 -to sdram_dqm_pad_o[1] 154 set_instance_assignment -name IO_STANDARD "3.3-V LVTTL" -to sdram_dqm_pad_o[1] 155 156 set_location_assignment PIN_M7 -to sdram_ba_pad_o[0] 157 set_instance_assignment -name IO_STANDARD "3.3-V LVTTL" -to sdram_ba_pad_o[0] 158 set_location_assignment PIN_M6 -to sdram_ba_pad_o[1] 159 set_instance_assignment -name IO_STANDARD "3.3-V LVTTL" -to sdram_ba_pad_o[1] 160 161 set_location_assignment PIN_L1 -to sdram_cas_pad_o 162 set_instance_assignment -name IO_STANDARD "3.3-V LVTTL" -to sdram_cas_pad_o 163 164 set_location_assignment PIN_L7 -to sdram_cke_pad_o 165 set_instance_assignment -name IO_STANDARD "3.3-V LVTTL" -to sdram_cke_pad_o 166 167 set_location_assignment PIN_P6 -to sdram_cs_n_pad_o 168 set_instance_assignment -name IO_STANDARD "3.3-V LVTTL" -to sdram_cs_n_pad_o 169 170 set_location_assignment PIN_L2 -to sdram_ras_pad_o 171 set_instance_assignment -name IO_STANDARD "3.3-V LVTTL" -to sdram_ras_pad_o 172 173 set_location_assignment PIN_C2 -to sdram_we_pad_o 174 set_instance_assignment -name IO_STANDARD "3.3-V LVTTL" -to sdram_we_pad_o 175 176 set_location_assignment PIN_R4 -to sdram_clk_pad_o 177 set_instance_assignment -name IO_STANDARD "3.3-V LVTTL" -to sdram_clk_pad_o 178 179 # 180 # GPIO0 (LEDs) 181 # 182 set_location_assignment PIN_A15 -to gpio0_io[0] 183 set_instance_assignment -name IO_STANDARD "3.3-V LVTTL" -to gpio0_io[0] 184 set_location_assignment PIN_A13 -to gpio0_io[1] 185 set_instance_assignment -name IO_STANDARD "3.3-V LVTTL" -to gpio0_io[1] 186 set_location_assignment PIN_B13 -to gpio0_io[2] 187 set_instance_assignment -name IO_STANDARD "3.3-V LVTTL" -to gpio0_io[2] 188 set_location_assignment PIN_A11 -to gpio0_io[3] 189 set_instance_assignment -name IO_STANDARD "3.3-V LVTTL" -to gpio0_io[3] 190 set_location_assignment PIN_D1 -to gpio0_io[4] 191 set_instance_assignment -name IO_STANDARD "3.3-V LVTTL" -to gpio0_io[4] 192 set_location_assignment PIN_F3 -to gpio0_io[5] 193 set_instance_assignment -name IO_STANDARD "3.3-V LVTTL" -to gpio0_io[5] 194 set_location_assignment PIN_B1 -to gpio0_io[6] 195 set_instance_assignment -name IO_STANDARD "3.3-V LVTTL" -to gpio0_io[6] 196 set_location_assignment PIN_L3 -to gpio0_io[7] 197 set_instance_assignment -name IO_STANDARD "3.3-V LVTTL" -to gpio0_io[7] 198 199 #============================================================ 200 # GPIO1 (Switches) 201 #============================================================ 202 set_location_assignment PIN_M1 -to gpio1_i[0] 203 set_location_assignment PIN_T8 -to gpio1_i[1] 204 set_location_assignment PIN_B9 -to gpio1_i[2] 205 set_location_assignment PIN_M15 -to gpio1_i[3] 206 set_instance_assignment -name IO_STANDARD "3.3-V LVTTL" -to gpio1_i[*]

以上是关于为啥我的quartus的管脚分配了但还是看不见啊?我想把分配好的管脚显示出来的主要内容,如果未能解决你的问题,请参考以下文章