Verilog如何检测一个时钟周期肿的翻转?

Posted

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了Verilog如何检测一个时钟周期肿的翻转?相关的知识,希望对你有一定的参考价值。

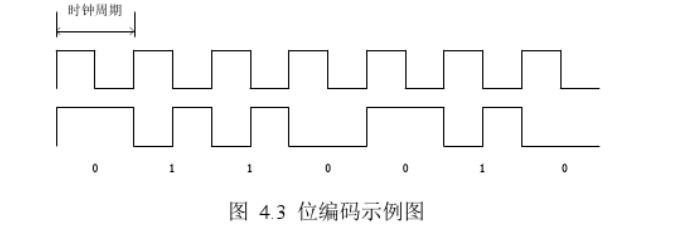

在做差分双相编码调制,发送端发送数据信号,确保发送的每一个数据位起始时刻都与内部时钟的上升沿对应,在一个周期内有翻转编码为1,无翻转编码为0,这个解调代码不太会写

当然你这个done 本身就可以定义为一个input 然后对应的 IO 外接控制高低电平的按键来控制done 的高低 简要思路如下:

module XX (done,XX,……);

input done;

output XX;

…… ;

reg XX;

always @ (done)

begin

if (done) //done 由输入IO口控制

XX = 0;

else

XX = ……;

end

........

..........

..........

endmodule

当然如果是些测试代码的话就是上面那位仁兄所写的。希望能帮到你,共同进步,加油!!

数字IC设计verilog编写——6脉冲同步器

数字IC设计verilog编写——6脉冲同步器

- 脉冲同步器

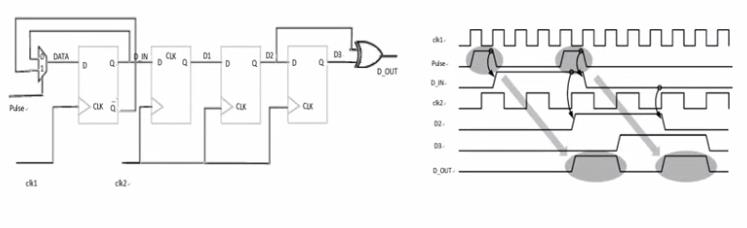

首先在源时钟域进行信号翻转,在跨时钟域到des_clk,并进行边沿检测,即为dec_clk时钟域的脉冲,实现脉冲同步;

脉冲同步器的使用中,快时钟的有效信号需要是单脉冲信号,并且两个有效信号的时间间隔需要大于等于两个同步器的时钟周期,否则,无法恢复出有效信号。

在实际的电路设计中,异步电路的设计在实际应用中的重要意义不言而喻。由于信号在不同时钟域之间传输,容易发生亚稳态的问题导致,不同时钟域之间得到的信号不同。

处理亚稳态常用打两拍的处理方法。

多时钟域的处理方法很多,最有效的方法异步fifo,异步fifo适合处理不同时钟域之间传输的数据组,但有时不同时钟域之间仅仅传递脉冲,异步fifo就显的有点大材小用的,因此单信号的跨时钟域处理通常有:

- 两级寄存器串联。

- 脉冲同步器。

- 结绳法。

- 采用握手。

脉冲同步器一般用在快时钟域信号进入慢时钟域的电路设计中

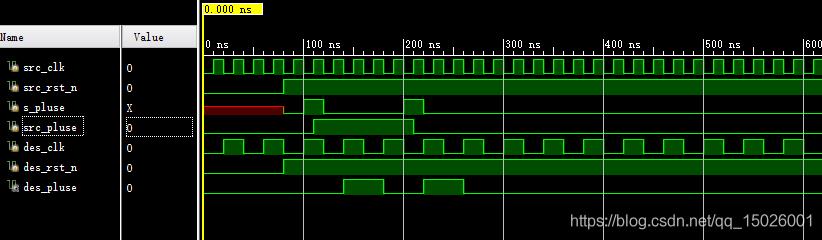

- RTL 代码

`timescale 1ns / 1ps

module pluse_sync(

input src_clk,

input src_rst_n,

input s_pluse,

input des_clk,

input des_rst_n,

output des_pluse

);

reg src_pluse;

always @ (posedge src_clk or negedge src_rst_n)

if(!src_rst_n)

src_pluse <= 1'b0;

else if(s_pluse)

src_pluse <= ~src_pluse;

reg d_reg1,d_reg2;

always @ (posedge des_clk or negedge des_rst_n)

if(!des_rst_n)

{d_reg1,d_reg2} <= 2'b00;

else

{d_reg1,d_reg2} <= {src_pluse,d_reg1};

assign des_pluse = (d_reg1 != d_reg2) ? 1'b1:1'b0;

endmodule

以上是关于Verilog如何检测一个时钟周期肿的翻转?的主要内容,如果未能解决你的问题,请参考以下文章