Allegro 电源和地铺铜后钻孔出现DRC错误。

Posted

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了Allegro 电源和地铺铜后钻孔出现DRC错误。相关的知识,希望对你有一定的参考价值。

pcb editor给电源和地铺铜后,所有钻孔,就是需要插元件的孔都出现DRC的错误标识,蝴蝶结上显示的是PS,是pin to shape.该怎么解决?新手初学感觉有很多问题。悬赏100金币,知道的讲解详细点,拜托拜托!

drc report是这样

report我放图了,麻烦帮我看看

参考技术A 你找到原因了嘛,我也出现了这样的错误candence的SMD pin to SMD pin spacing问题(元件本身的引脚间距过小造成的DRC错误)

前言

在用allegro绘制PCB的时候,明明已经规定好间距,结果莫名奇妙的报DRC错误,而且还是同一个元器件。真服了。

就像下面这个。

然后参考了网上的解决方法,不知道是不是版本问题,没有所说的选项。

有兴趣的可以看一下

Allegro消除元件本身的引脚间距过小造成的DRC错误

我用的版本candence 17.2

一、解决方法

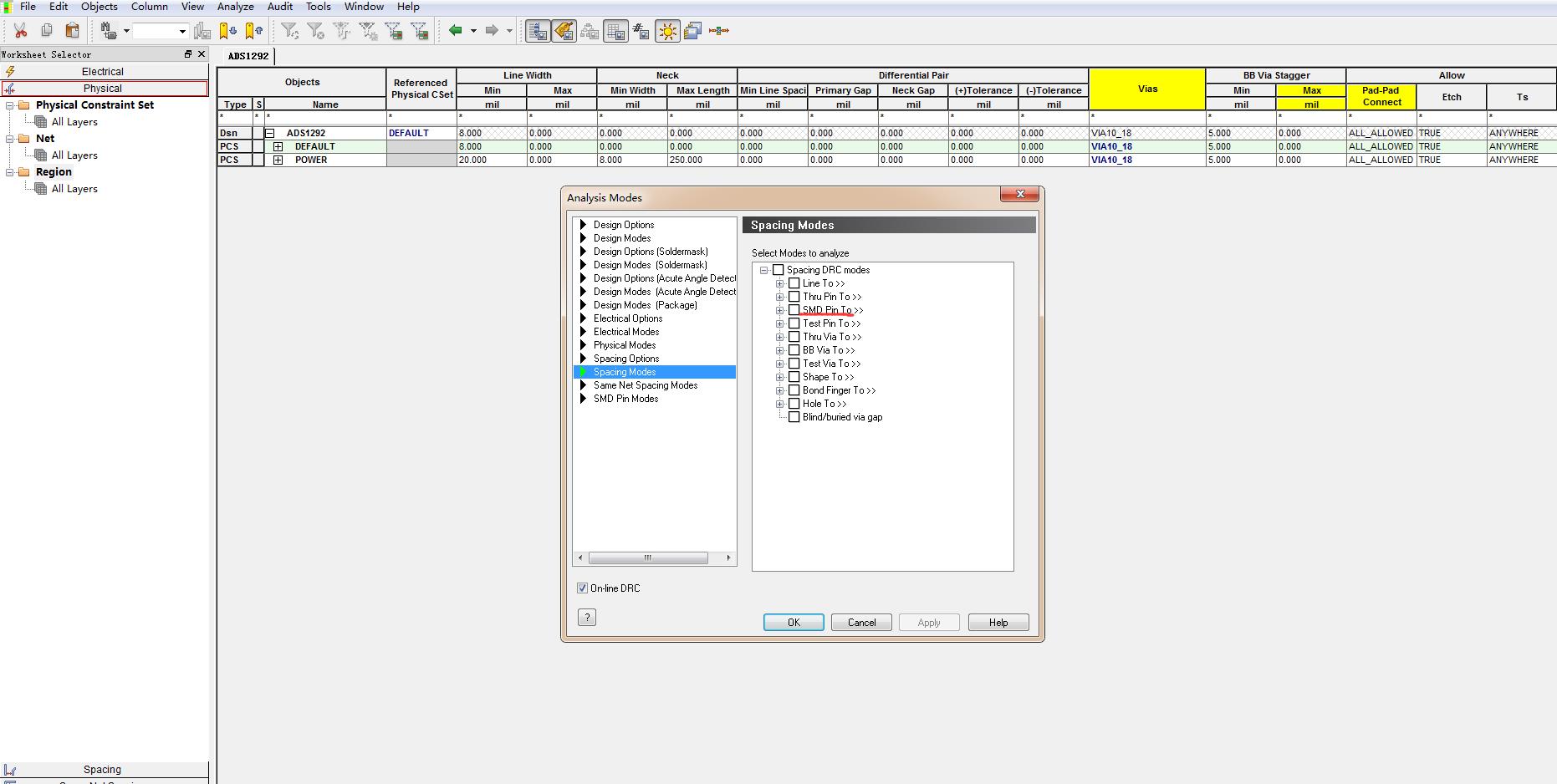

我也是找了好久才解决,就是在我们规则设计检查这里,不勾选这一项,其他的一样的道理。我的错误是SMD pin to SMD pin spacing问题

你用鼠标的光标去点击或者靠近DRC的错误,他会有提示。

然后把这些DRC检查去掉就可以了。

总结

好了今天的分享就到这里。希望能解决你的问题。

其他的问题大家可以看看这篇:allegro 遇到的问题汇总 避免忘记

以上是关于Allegro 电源和地铺铜后钻孔出现DRC错误。的主要内容,如果未能解决你的问题,请参考以下文章

allegro16.2中怎样设置可以使VIA打在PAD上不提示DRC

candence的SMD pin to SMD pin spacing问题(元件本身的引脚间距过小造成的DRC错误)