如何配置MIPI DSI Clock和PCLK

Posted

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了如何配置MIPI DSI Clock和PCLK相关的知识,希望对你有一定的参考价值。

RK针对MIPI DSI的lcd配置时有两个clock, rockchip,dsi_hs_clk 和 clock-frequency.文件中如下:

disp_mipi_init: mipi_dsi_init

compatible = "rockchip,mipi_dsi_init";

rockchip,screen_init = <1>;

rockchip,dsi_lane = <4>;

rockchip,dsi_hs_clk = <348>;

rockchip,mipi_dsi_num = <1>;

;

disp_timings: display-timings

native-mode = <&timing0>;

compatible = "rockchip,display-timings";

timing0: timing0

screen-type = <SCREEN_MIPI>;

lvds-format = <LVDS_8BIT_2>;

out-face = <OUT_P888>;

clock-frequency = <58200000>;

hactive = <480>;

vactive = <1280>;

hback-porch = <160>;

hfront-porch = <160>;

vback-porch = <10>;

vfront-porch = <12>;

hsync-len = <24>;

vsync-len = <2>;

hsync-active = <0>;

vsync-active = <0>;

de-active = <0>;

pixelclk-active = <0>;

swap-rb = <0>;

swap-rg = <0>;

swap-gb = <0>;

;

;

有人可能对这两个值不太清楚如何设置,而设置出错会引起显示异常,这里简要说明下:

clock-frequency:

即DCLK(dotc clock), PCLK(pixel clock).

clock-frequency = (h_active + hfp + hbp + h_sync) * (v_active + vfp + vbp + v_sync) * fps

厂商给的参考值是58.2MHz, 那么fps就是:

fps = 58200000 / (480 + 160 + 160 +24) * (1280 + 12 + 10 + 2) = 54Hz

PCLK不能太大,android支持不超过60fps.

PCLK不能太小,小了画面刷新率会比较慢.

rockchip,dsi_hs_clk:

即每条MIPI data lane 传输速率.

dsi_hs_clk = ((h_active + hfp + hbp + h_sync) * (v_active + vfp + vbp + v_sync) * fps * bpp) / lane_number

这里就是:

dsi_hs_clk = ((480 + 160 + 160 +24) * (1280 + 12 + 10 + 2) * 54 * 24) / 4 = 348136704 bps = 348 Mbps

hs_clk不能太小,太小会显示灰屏,偏小会偏移.

hs_clk不能太大,过大画面会显示条纹.

RK文档有提到 dsi_hs_clk还需要加上100, 追踪了下源码,没看出来.

另外我有实际测试其中一款屏,发现最终的值还是会有差异,不知道这是为什么.

顺便说下, 由于MIPI DSI上升沿和下降沿都可以发送数据,所以

MIPI CLK Lane * 2 = MIPI DATA Lane

在测量的时候, 要注意MIPI DSI CLK Lane的时钟速率会慢一倍. 参考技术A MIPI(Mobile Industry Processor Interface)是2003年由ARM, Nokia, ST ,TI等公司成立的一个联盟,目的是把手机内部的接口如摄像头、显示屏接口、射频/基带接口等标准化,从而减少手机设计的复杂程度和增加设计灵活性。MIPI联盟下面有不同的WorkGroup,分别定义了一系列的手机内部接口标准,比如摄像头接口CSI、显示接口DSI、射频接口DigRF、麦克风/喇叭接口SLIMbus等。统一接口标准的好处是手机厂商根据需要可以从市面上灵活选择不同的芯片和模组,更改设计和功能时更加快捷方便。

其优点是;更低功耗、更高数据传输率和更小的PCB占位空间,并且专门为移动设备进行的优化,因而更适合手机和智能平板的连接。

MIPI DSI

MIPI DSI是什么?

MIPI(移动行业处理器接口)是Mobile Industry Processor Interface的缩写。MIPI(移动行业处理器接口)是MIPI联盟发起的为移动应用处理器制定的开放标准,常用到的是DSI(显示接口)和CSI(摄像接口)。

嗯~MIPI DSI是一种用于显示的接口。小分辨率的都是并口,随着分辨率越做越高,速度越来越快,并口就不能满足需求了。因此出现了LVDS接口和MIPI DSI。

DSI初了解

MIPI官网链接:https://mipi.org/specifications/dsi-2 里面有所有的DSI,CSI,D-PHY等协议

打开DSI的SPEC,170多页

先看看introduction

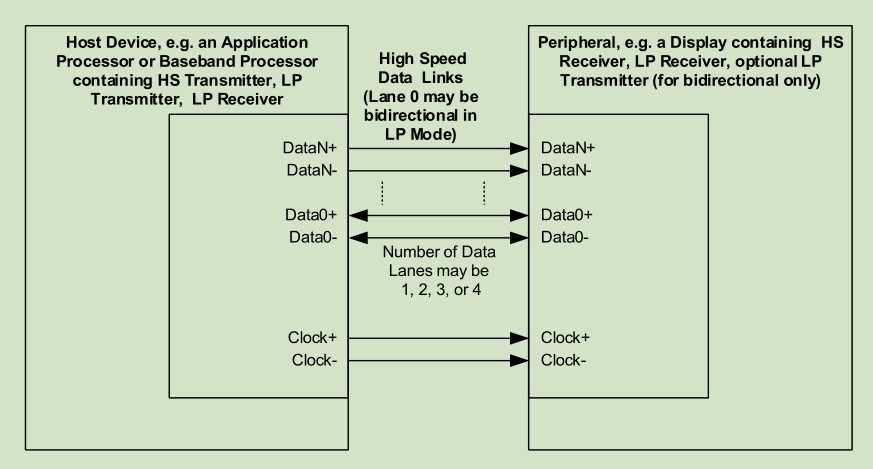

接口是4对数据差分信号和1对时钟差分信号,4条数据lane和1条datalane,第0条lane是双向的,其他lane是从发送到接收。

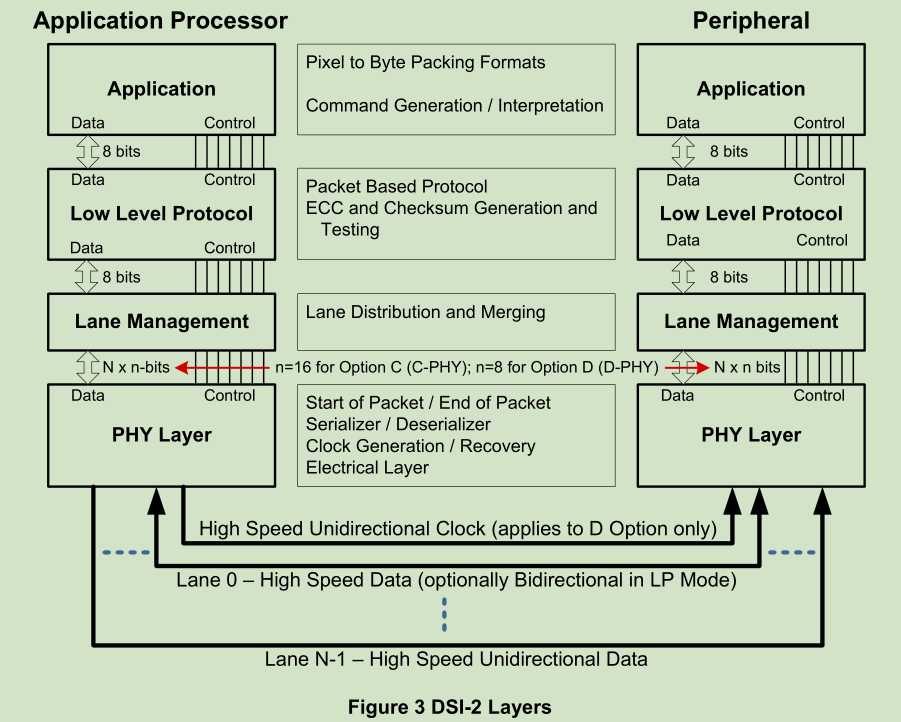

和很多高速串行接口一样(USB,SATA,PCIE),它们都是分层设计,大同小异。DSI如上图分为4层架构,Application属于上层架构,软件搞的;硬件需要搞的是下面3层:

PHY layer:物理层,定义传输媒介,包含高速串行接口,并串转换,时钟产生,组包;这部分的工作主要是模拟设计。

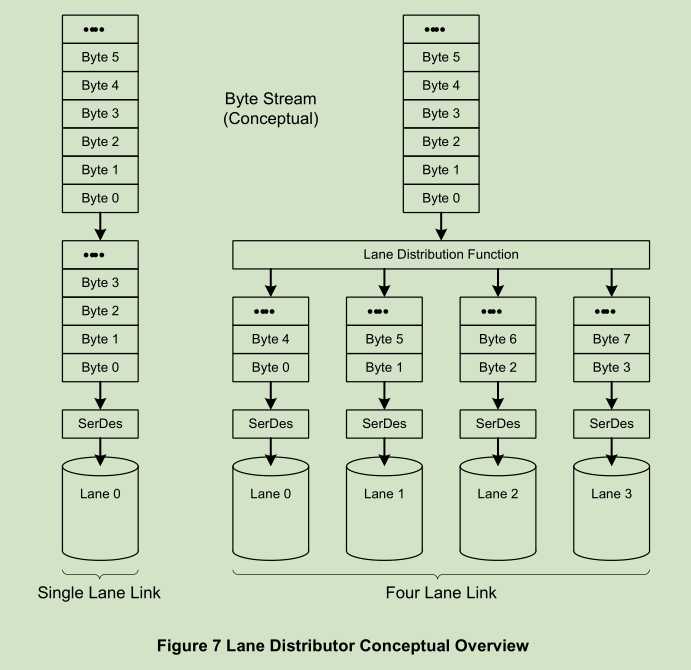

Lane management:lane管理,将数据流按照顺序依次分发到每条lane上。

Low level protocol;按照DSI协议指定数据组包方式,定义包头等相关内容,生成ECC,校验码等。

DSI的模式有command mode和video mode,

command mode下dsi以命令的方式发送命令和数据到具有现实缓存的控制器。寄存器配置,参数,帧数据等,这种模式下也可以读屏的信息等

video mode:这种模式是最常用的模式,从主机传输视频数据,这种模式以高速传输,为了减少复杂性和节约成本只采用video模式的系统只有一个单向数据路径。

接下来就逐层学习下

DSI Physical layer(D-PHY)

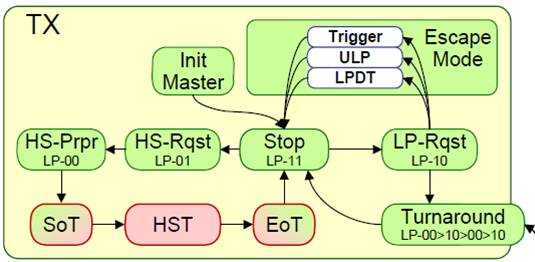

HS : 高速模式下传输视频数据,80Mbps~1Gbps/lane

LPS:Low-Power State,低功耗模式,用于控制:10Mhz(max)

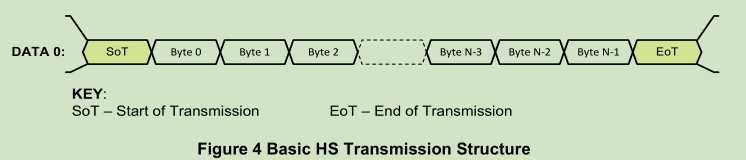

D-PHY低层协议规定最小的数据单元是一个字节,发送数据必须低位在前,高位在后。

D-PHY可能包含:

低功耗发送器(LP-TX)

低功耗接收器(LP-RX)

高速发送器(HS-TX)

高速接收器(HS-RX)

低功耗竞争检测器(LP-CD)

如果做host和屏对接,可以只有TX

lane状态和电压

LP-00,LP-01,LP-10,LP-11(单端)

HS-0,HS-1(差分)

lane电压(典型)

LP:0-1.2v HS:100-300mv(200mv)

进入高速模式过程:LP11->LP01->LP00->SOT(00011101)->HSD(80Mbps->1Gbps)

退出高速模式过程:EOT->LP11

多条lane分发

如果byte数和lane非对齐

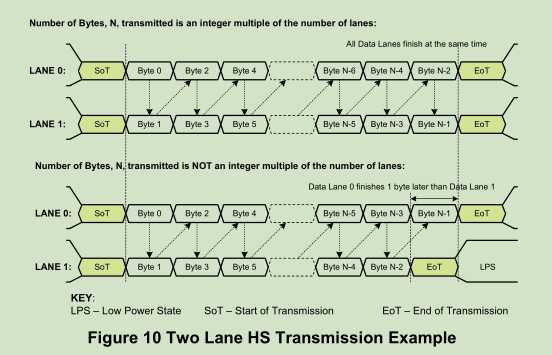

2lane对齐传输和非对齐传输下EOT的发送如下图:

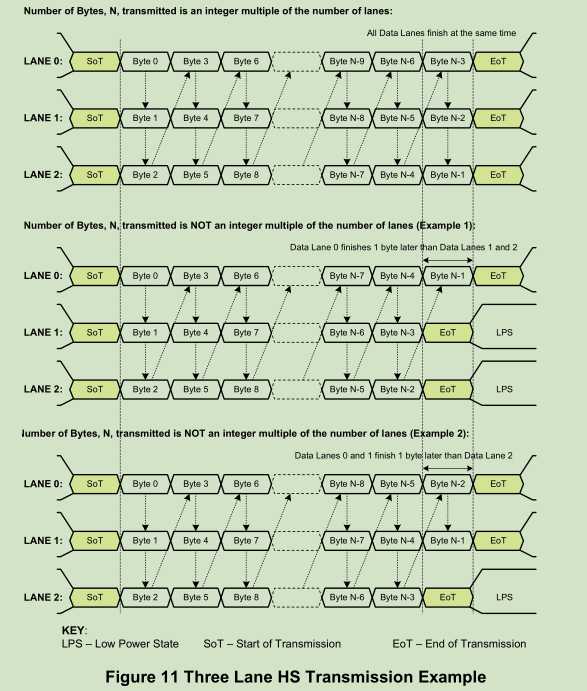

3lane对齐传输和非对齐传输下EOT的发送如下图所示:

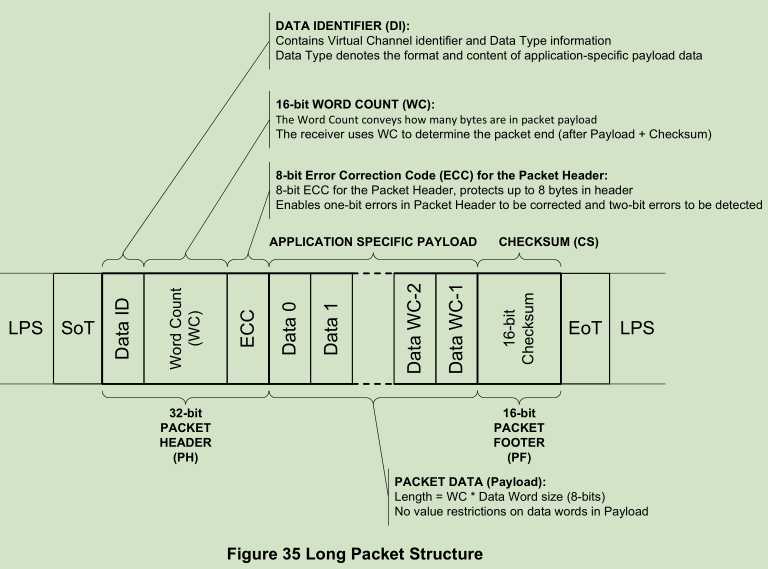

MIPI是怎样组包,包的格式是什么样的呢?

DSI以包(packet)的方式封装进行传输的,帧类型有:

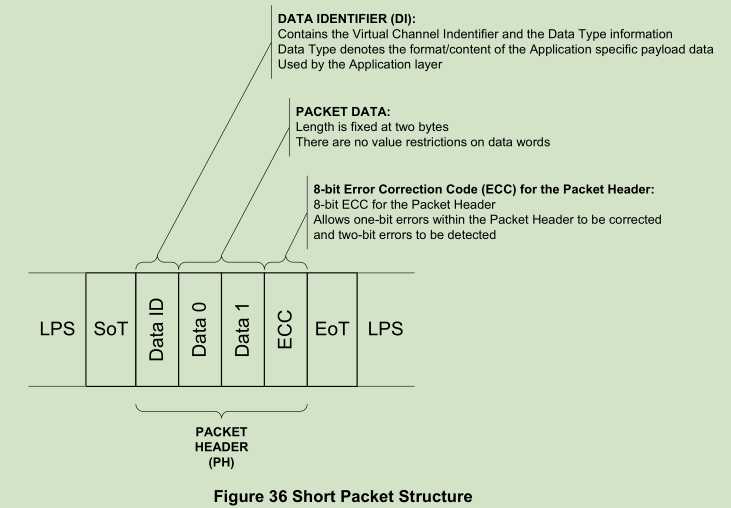

短帧:4bytes(固定)

长帧:6-65541bytes(可变)

短帧结构(4个字节)

数据标识(DI)1个字节

帧数据:data0,Data1,两个字节,表示要传输的数据

ECC:1个字节,误差校验码

长帧结构

DI:数据标识符

WC:word count,两个字节,包中有效负载长度

ECC:一个字节,误差校正码

Data:有效负载

Checksum:2个字节校验码

以上是关于如何配置MIPI DSI Clock和PCLK的主要内容,如果未能解决你的问题,请参考以下文章