Xilinx ISE 13.1综合提示错误啥原因?

Posted

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了Xilinx ISE 13.1综合提示错误啥原因?相关的知识,希望对你有一定的参考价值。

Verilog程序如下:

`timescale 1ns / 1ps

module counter(

input clk,

input reset,

output [7:0] dout

);

reg [7:0] dout;

always @(posedge clk)begin

if(reset==0)

dout<=0;

else

dout<=dout+1;

end

endmodule

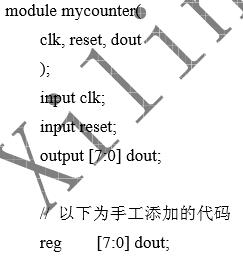

综合时提示如下信息: Illegal redeclaration of 'dout',该怎么解决?

Error (10759): Verilog HDL error at count_8.v(6): object dout declared in a list of port declarations cannot be redeclared within the module body

这是quartus给出的解释,就是说port是不能被重新定义或声明的。可以向这样改:

也可以在定义port的时候在写成:output reg [7:0] dout,然后把出问题的那句删掉。

参考技术A xilinx的错误提示是有超链接的,点进去可以看到xilinx的官方解决方案代码。追问问题已经解决

追答yes

我是觉得渔网也很重要

module counter(

input clk,

input reset,

output reg [7:0] dout

); 参考技术C output [7:0] dout - output reg [7:0] dout,

reg [7:0] dout; - 删除追问

为什么需要如此改动?

追答verilog 2001语法标准 不为什么

参考技术D 请删除 reg [7:0] dout; 这一句然后试试Xilinx ISE的时序约束

使用Synplify Pro加时序约束。综合完毕后,可以在ISE中进行布局、布线。需要用.ucf文件指定布局布线的时钟约束。前者可以比后者小。

早期的ISE,两个约束可以继承。现在用的高版本,反而需要分别指定,否则会忽略掉。

将综合(Synthesis)的频率提高,将布局布线(Place & route)的频率降低,可以提高性能指标。以后者为性能依归。

以上是关于Xilinx ISE 13.1综合提示错误啥原因?的主要内容,如果未能解决你的问题,请参考以下文章