ADS仿真入门1 -- 结合史密斯圆图对特性阻抗的tuning

Posted

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了ADS仿真入门1 -- 结合史密斯圆图对特性阻抗的tuning相关的知识,希望对你有一定的参考价值。

参考技术A 作为一名硬件工程师,如果板子打出来高速差分特性阻抗不满足要求怎么办?在不该PCB的情况下如何做临时tuning?首先,我们需要将几个公式了然于心:

平行板电容量

C=εoA/h

A表示平行板面积,h表示平板间距。

圆形导体局部自感

L=5dln(2d/r)-3/4

d为长度,r为半径

A表示平行板面积,h表示平板间距。

频域二阶阻抗公式

Z(w)=R+i(wL-1/wC),w=2πf 频域二阶

w指角频率,i为相位复数,f为频率。

微带线(microstrip)特性阻抗

Z=87/[sqrt(Er+1.41)]*ln[5.98H/(0.8W+T)]

W为线宽,T为走线的铜皮厚度,H为走线到参考平面的距离,Er是PCB板材质的介电常数(dielectric constant)

带状线(stripline)特性阻抗

Z=[60/sqrt(Er)]*ln4H/[0.67π(0.8W+T)]

即与介电常数、铜箔厚度成反比;与介质厚度(与参考层的距离)成正比

综合上面3个公式,可领悟出,铜箔越厚,L越小,Z(w)=R+i(wL-1/wC),故特性阻抗变大;与参考层距离越大,C越大,Z(w)=R+i(wL-1/wC),故特性阻抗越小。

再实际一点,就是信号遇到容性阻抗时,特性阻抗会降低;遇到感性阻抗时,特性阻抗会升高。

S11=Vr/Vi=(Z2-Z1 )/(Z2+Z1)

S12=Vt/Vi=2*Z2/(Z2+Z1) (2)

Vi为反射前端信号电压,Vr为反射电压,Vt为反射后端信号电压,Z1为反射前端阻抗,Z2为反射后端阻抗,Vo为驱动端电压。Vi为传输线电压。

实际一点,就是如果后端阻抗大于输入阻抗,就是形成正反射,信号电压升高,即过冲;就是如果后端阻抗小于输入阻抗,就是形成负反射,信号电压降低,即下冲。我们经常在发送端加22~33Ω匹配串阻,就是因为CMOS输出阻抗很低,只有20~40Ω,需要进行阻抗匹配。

ADS建一个简单的前仿真线路

主要是因为兴趣玩玩,所以在线路上胡乱串联并联了LC,看看能不能调,正常情况下高速信号上肯定只有AC coup,所以结果会不怎么好看,损耗太严重。

扫描频率设置为1GHz~5GHz,设置差分S参数公式,提取差分回损SDD11,差分插损SDD12,TDR阻抗,史密斯圆图结果。

从Smith圆图上增加2个mark点,可以看出在1GHz时,阻抗约为超出100较多;在5GHz,阻抗低于100较多,且实部阻抗一直不在Zo圆圈附近,在实部和虚部高低之间一直来回震荡。

打开ADS tuning,调节串联LC和并联C的值,发现串联C的值影响几乎忽略不计,故此处不写,串阻R也是,发现对信号的损耗太大。

增大串联L从0.05nH到2.04nH,从史密斯圆图上发现1G~5GHz阻抗几乎在同一个实部圆圈上,由于阻抗匹配较好,所以SDD11回损几乎保持不变,TDR曲线几乎没变,但插损损失变得更加严重。

继续增大L到5.025nH,从史密斯圆图上看,较低频的1GHz阻抗从0.05nH时的实部1.457降到0.503,阻抗变小了很多;5GHz反而相反。插损更加严重,接收端能接受到的功率在2GHz下几乎无法满足了。

总结得出,串联L对特性阻抗的调试没有线性规律,还是取决于板子上信号频率,且L越大,插损越大,不宜采取此方法。

将并联电容从0.1nF减小为0.001nF,发现1GHz阻抗实部从1.45降为1.234,5GHz实部从0.68减为0.676,史密斯圆圈变小,越来越靠近Zo,所以回损插损整体都变小。

将并联电容从0.001nF增到为10nF,发现1GHz阻抗实部从1.234升为1.442,5GHz实部从0.676降为0.606,史密斯圆圈变大,所以回损插损整体都变大,由于5GHz阻抗变化非线性,故并联电容无法线性调节阻抗。

将并联电容从10nF增到为100nF,发现1GHz阻抗实部虚部均几乎没有变化,不仅如此其他参数也没有变化,故可见并联C并不能一直影响特性阻抗,它有一个范围。

综上,搞了半天,高速差分阻抗调试必须搭配频率,没有一定的规律可寻,而结合最开始说的公式,线宽线距过孔参考层都会影响到阻抗,所以还是安心在gerber前把阻抗控制好,注意review stackup和layout,否则万劫不复准备走人啊~

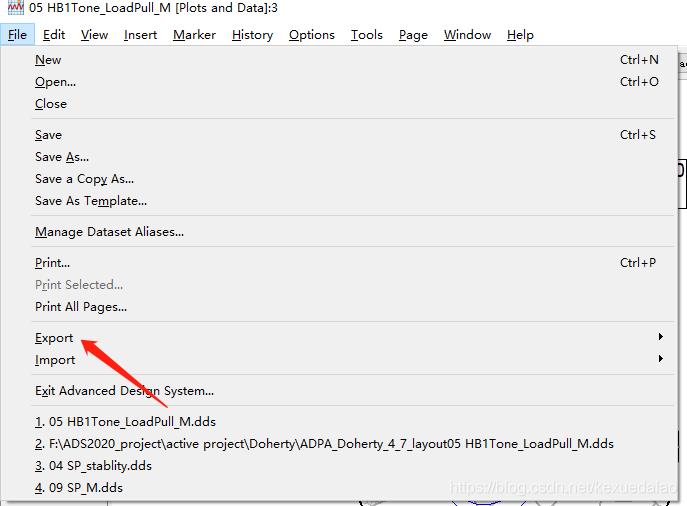

如何把ADS的圆图导入到origin中

以上是关于ADS仿真入门1 -- 结合史密斯圆图对特性阻抗的tuning的主要内容,如果未能解决你的问题,请参考以下文章