思科时钟频率配置命令

Posted

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了思科时钟频率配置命令相关的知识,希望对你有一定的参考价值。

参考技术A 设置时间及时区命令如下:1.设置时区:Router(config)#CLOCK Timezone beijing +08 //设置为北京的时区为东8区

2.设置时间:Router# clock set 10:00:00 Aug 4 2015 //设置时间为2015年8月4日10时整

3.设置网络时间:Router(config)#ntp server s1b.time.edu.cn //清华大学NTP服务器

由于路由器在交互时对时间的匹配要求严格,所以在配置路由器时不推荐使用手动设置时间, 我们一般借助专门的时间同步服务器来配置网络设备的时间。

Network Time Protocol(NTP)是用来使计算机时间同步化的一种协议,它可以使计算机对其服务器或时钟源(如石英钟,GPS等等)做同步化,

它可以提供高精准度的时间校正(LAN上与标准间差小于1毫秒,WAN上几十毫秒),且可介由加密确认的方式来防止恶毒的协议攻击。

NTP可以利用多个途径和来源的时间服务器来更加精确的校正时间。

现在绝大部分的操作系统都支持NTP,比如在Unix和Windows中都有他们自己的NTP服务。比如在Windows中的SNTP。

由于各个系统厂商会根据自己的系统情况对NTP来进行优化和设置,

更加适合他自己的系统,对于其他系统的兼容性就会差很多。还有不同时期的系统会使用不同版本的NTP服务。最新版本位V4,由于每个版本都要他自己的一些特征。

所以在设置NTP服务器时会有一些兼容性问题。

因此,在多类型操作系统的环境中,尽量使用NTP官方组织提供的软件进行设置而不使用其他厂商在系统中默认提供的NTP服务器。NTP官方组织为

www.ntp.org。

Server一般用于服务器端,该服务器不会去同步其他服务器时间,一般server后可以跟 127.127.1.0 该地址代表本级的时钟,

如果Server后跟其他服务器IP,表示会去同步其他时间服务器的地址。 参考技术B 思科网络设备配置命令大全

基础配置

1思科设备管理基础命令

enable 从用户模式进入特权模式

configure terminal 进入配置模式

interface g0/0 进入千兆以太网接口g0/0

ip address 172.16.0.1 255.255.0.0 配置接口的 ip 地址

no shutdown 开启接口

line vty 0 4 进入虚拟终端 vty 0 – vty 4

password CISCO 配置认证密码

login 用户要进入路由器,需要先进行登录

exit 退回到上一级模式

enable password CISCO 配置进入特权模式的密码,密码不加密

end 直接回到特权模式

show int g0/0 显示 g0/0 接口的信息

hostname Terminal-Server 配置路由器的主机名

enable secret ccielab 配置进入特权模式的密码,密码加密

no ip domain-lookup 路由器不使用 DNS 服务器解析主机的 IP地址

logging synchronous 路由器上的提示信息进行同步,防止信息干扰我们输入命令

no ip routing 关闭路由器的路由功能

ip default-gateway 10.1.14.254 配置路由器访问其他网段时所需的网关

show line 显示各线路的状态

line 33 48 进入 33-48 线路模式

transport input all 允许所有协议进入线路

int loopback0 进入 loopback0 接口

ip host R1 2033 1.1.1.1 为 1.1.1.1 主机起一个主机名

alias exec cr1 clear line 33 为命令起一个别名

privilege exec level 0 clear line 把命令 clear line 的等级改为 0,在用户模式下也可以执行它

banner motd 设置用户登录路由器时的提示信

show ip int brief 查看接口状态

2VLAN相关命令

vlan X 创建VLAN X

name SPOTO 将VLAN X命名为SPOTO

exit 退出当前模式

interface e0/0 进入以太网接口e0/0

switchport mode access 将二层接口设置为接入模式

switchport access vlan X 将接口划入vlan X

interface e0/1

switchport trunk encapsulation dot1q trunk链路封装协议为 802.1q

switchport mode trunk 将二层接口配置模式为 trunk

switchport trunk allow vlan X trunk接口单独放行某个 vlan。

Show vlan 查看设备vlan信息

3 VTP相关配置命令

vtp domain SPTO 配置VTP域名

vtp mode server 修改模式(默认为 server)

vtp pass SPOTO 配置密码VTP密码

vtp version 2 修改版本

vtp pruning 开启VTP修剪功能

show vtp status 查看VTP信息

4Ethernetchannel相关配置命令

interface ran ge e0/0 -1 批量进入接口

channel-pro lacp 启用 lacp 协议

channel-group 1 mode active 捆绑组 1 模式:主动

interface port-channel 1 进入逻辑链路

show etherchannel summary 查看捆绑组

5HSRP(Cisco 私有)/VRRP配置命令

spandby/vrrp 10 ip 192.168.1.254 设置虚拟网关

spandby/vrrp 10 priority110 修改优先级为 110(默认100)

spandby/vrrp 10 preempt 开启抢占

track 10 interface e0/0 line_protocol 启用链路检测

standby/vrrp 10 track 10 decrement 20 如果断开则自降优先级级 20

show hsrp/vrrp brief 查看 hsrp/vrrp 状态

6STP配置命令

spanning-tree cost 10 修改接口开销值

spanning-tree vlan x cost 10 针对一个 vlan 修改开销值

spanning-tree vlan x priority 0 或 spanning-tree vlan x root priority 将设备设置为vlan x的主根桥

spanning-tree vlan x priority 4096 或 spanning-tree vlan x root secondary 将设备设置为vlan x的备份根桥

show spanning-tree brief 查看生成树状态

7MSTP配置命令

spanning-tree mode mst 修改生成树模式为MSTP

spanning-tree mst conf 进入MSTP配置模式

instance 1 vlan 10,20 创建实例1并将vlan10、20纳入实例1

instance 2 vlan 30,40 创建实例2并将vlan30、40纳入实例2

spanning-tree mst 1 priority 0 配置实例 1 为根桥

spanning-tree mst 2 priority 4096 配置实例 2 为备根桥

show spanning-tree mst 1 查看实例

路由配置

一、静态路由

Ip route x.x.x.x(网段) x.x.x.x( 子网掩码) x.x.x.x/出接口(下一跳) (尽量用下一跳地址,出接口会产生 ARP 消息)

默认路由:

Ip route 0.0.0.0 0.0.0.0 x.x.x.x(下一跳)

黑洞路由:

IP route x.x.x.x x.x.x.x null 0 将不需要的流量丢弃到 null 0(黑洞接口)

Loopback 接口:

Interface loopback 0

Interface loopback 1

Interface loopback 2

BFD双向转发检测:

Interface ethernet0/0

Bfd interval 50 min_rx 50 multiplier 3 接口开启BFD检测,50ms发送一次探测帧,3次超时

Ip route static bfd e0/0 x.x.x.x

Ip route 1.1.1.1 255.255.255.255 e0/0 x.x.x.x 静态路由联动BFD

Show bfd neighboor 查看BFD邻居

二、动态路由

Rip:

Router rip 启动 rip 进程

Version 2 指定版本 2

Network x.x.x.x 宣告网段

No auto-summary 关闭自动汇总 重点!!!

Default-information originate 默认路由下发

Redistribute static 静态路由重分布

EIgrp (cisco 私有):

Router eigrp 1 同区域同 AS 号

Network x.x.x.x x.x.x.x (反掩码)宣告网段

No auto-summary 关闭自动汇总

Ospf :

Router-id x.x.x.x 设置 routeID

Router ospf 1 启动 ospf 进程为 1

Network x.x.x.x x.x.x.x area 0 宣告网段,这里区域为 0

Ip ospf network x.x.x.x 接口下更改 ospf 网络类型

Show ip ospf nei 查看 ospf 邻居

Show ip ospf interface brief 查看接口关于 ospf 的信息

Show ip route ospf 查看 ospf 路由

Show ip ospf database 查看 ospf 链路状态数据库

Debug ip ospf adj 查看 ospf 邻居关系建立过程

Debug ip ospf hello 查看 ospf hello 包

Debug ip ospf events 查看 ospf 相关事件

DHCP:

Service dhcp 开启 dhcp (默认开启)

IP dhcp pool name 设置地址池名称

Network 192.168.1.0 255.255.255.0 指定可分配网段

Default-router 192.168.1.254 下发网关

Dns-server 8.8.8.8 下发 dns

ip dhcp excluded-address 192.168.1.254 排除这个地址不做分配

Pc端:interface e0/0

Ip add dhcp 地址通过DHCP方式获取

DHCP 中继:

Int vlan x

Ip add x.x.x.x x.x.x.x

Ip helper-address 192.168.1.254 (dhcp 服务器上的接口) 指向 dhcp 服务器

Show ip dhcp pool name 查看 dhcp 地址池

三、ACL 访问控制列表

标准 ACL:1-99 “No access-list 一条”将会删除整个 ACL 列表。

Access-list 1 deny x.x.x.x x.x.x.x 拒绝某网段通过

Access-list 1 permit any 允许所有通过

Inter e0/0

Ip access-group 1 in 进接口下调用

配置了 ACL 一定要在接口下调用,否则不生效,或者接口下调用了,全局下没有这个 ACL 也不生效。

扩展 ACL:100-199 “No access-list 一条”将会删除整个 ACL 列表。

Access-list(100-199) per/deny 协议(IP 代表所有 TCP/IP 协议)x.x.x.x(源地址) 反掩码 端口号(选加) x.x.x.x(目的) 反掩码(不加默认为 0.0.0.0)端口号(选加)

Access-list 100 deny(拒绝或允许) tcp(协议) any(源地址) host(精确主机,) x.x.x.x (不加反掩码默认为 0.0.0.0)eq 23 或者 access-list 100 deny tcp any x.x.x.x 0.0.0.0 eq 23 拒绝所有的 TCP 协议访问 x.x.x.x 的 23端口

Access-list 100 permit ip(所有 TCP/IP 协议) any(源) any(目的) 允许所有

Int e0/1 进入接口

Ip access-group 1 out 调用在出接口

Show ip access-list 编号 查看 ACL

Show ip access-list int vlan x

Show run | sec access-list 查看 ACL 配置

字符命名 ACL

Ip access-list standard(标准)/extended(扩展) name 创建命名 ACL,如果name 用数字命名,则会进入到数字 ACL 下,并不是字符命名 ACL。

时钟配置

要让LPC824正常工作,首先要对它的时钟源进行配置。LPC824的最高工作频率为30MHz,因此给它的主时钟频率最大不能超过30MHz。实际上,通常都是使用频率较低的晶振,以降低外部电磁干扰,然后再通过内部倍频的方式把主时钟频率提高。根据管方手册给出的数据,外部晶振的频率范围是1MHz~25MHz,一般情况下使用12MHz晶振,然后内部进行2倍频,主时钟工作频率为24MHz。

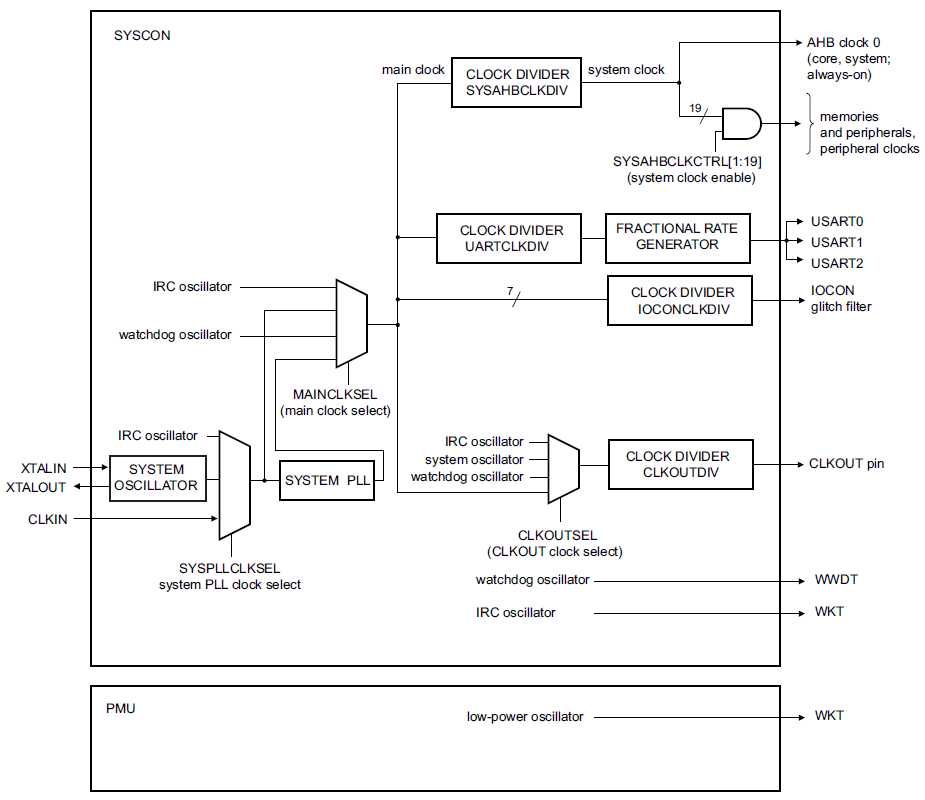

要对LPC824的时钟进行配置,必须要了解它的时钟结构,先来看一下它的时钟结构图,如下图所示。

首先来看主时钟,给主时钟(main clock)提供选择有4个源,分别是:内部RC振荡器、未倍频之前的PLL时钟、内部看门狗时钟、经过PLL倍频之后的时钟。由对主时钟源选择寄存器(MAINCLKSEL)的操作来进行选择,同一时刻只能选择一种时钟做为主时钟。

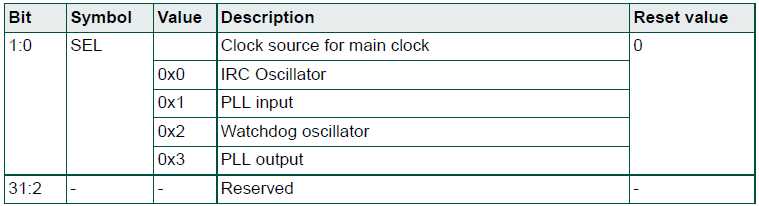

下表给出了主时钟源选择寄存器MAINCLKSEL的全部位结构,其字节地址为0x40048070。注意,由于LPC824是32位微控制器,所以它内部的寄存器全都是32位的。

(1)第0、1两位(SEL)为主时钟源选择位,这两位的值从0x0到0x3,分别对应选择内部RC时钟、未倍频之前的PLL时钟、内部看门狗时钟、经过PLL倍频之后的时钟。

(2)第2到31位为保留位。

一般情况下都会选择系统PLL倍频后的时钟作为主时钟,因此大多数时候MAINCLKSEL寄存器的值都会选择0x3(执行语句“LPC_SYSCON->MAINCLKSEL=0x00000003”)。

接下来看系统PLL时钟,PLL(Phase Locked Loop)即锁相环,它的功能很多,这里主要利用它来实现倍频的功能。从时钟结构图中可以看出,供给PLL选择的有3个源,一个是片内RC振荡器,另一个是系统振荡器,再一个是外部输入。通过对系统PLL时钟选择寄存器的操作可进行选择,但同一时刻只能选择一种时钟作为输入时钟。

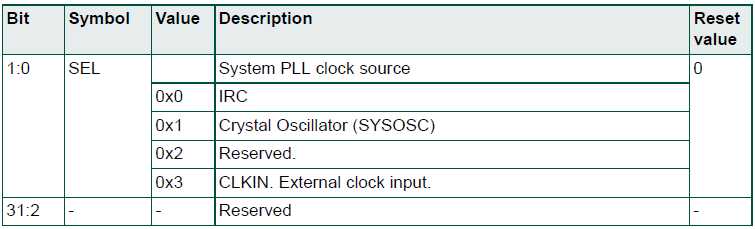

下表给出了系统PLL时钟选择寄存器SYSPLLCLKSEL的全部位结构,其字节地址为0x40048040。

(1)第0、1两位(SEL)为系统PLL时钟源选择位,值为0x0时选择内部RC时钟,值为0x1时选择系统振荡时钟(即外部晶振),值为0x3时选择外部时钟输入,其他值为保留。

(2)第2到31位为保留位。

为了提高LPC824的时钟精度,一般情况下SYSPLLCLKSEL寄存器的值会选择0x1(执行语句“LCP_SYSCON->SYSPLLCLKSEL=0x00000001”),以选择外部晶体振荡器作为时钟输入。

从时钟结构图中可以看到,主时钟分成4路供给不同的模块。其中一路主时钟经过系统AHB时钟分频选择(SYSAHBCLKDIV)后作为系统时钟提供给AHB。在LPC824中,只有高速设备(如GPIO、SRAM等)才需要AHB。为了给不同速度的模块(如内核、存储、APB等)提供时钟,需要对系统AHB时钟分频选择寄存器进行操作,以对主时钟进行分频。

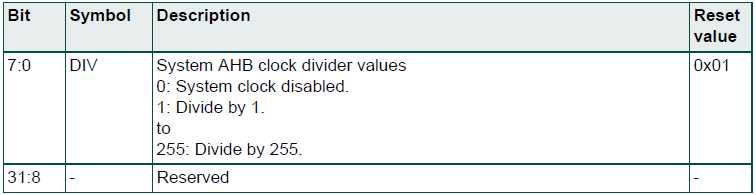

下表给出了系统AHB时钟分频选择寄存器SYSAHBCLKDIV的全部位结构,其字节地址为0x40048078。

(1)第0到7位(DIV)为系统AHB时钟选择位,值为0时禁止系统时钟,其他值为AHB时钟的分频值。

(2)第8到31位为保留位。

从表中可以看到,AHB时钟分频的最大值为255。系统的默认值为1(也可执行语句“LPC_SYSCON->SYSAHBCLKDIV=0x00000001”来实现),即为AHB提供不分频的主时钟。剩余3个模块(USART、IOCON、CLKOUT)的时钟也一样由主时钟来分频,只不过它们默认的分频值为0,即默认不提供时钟,也就是说剩余的3个模块在默认状态下不工作,需要的时候再通过程序打开,以降低功耗。

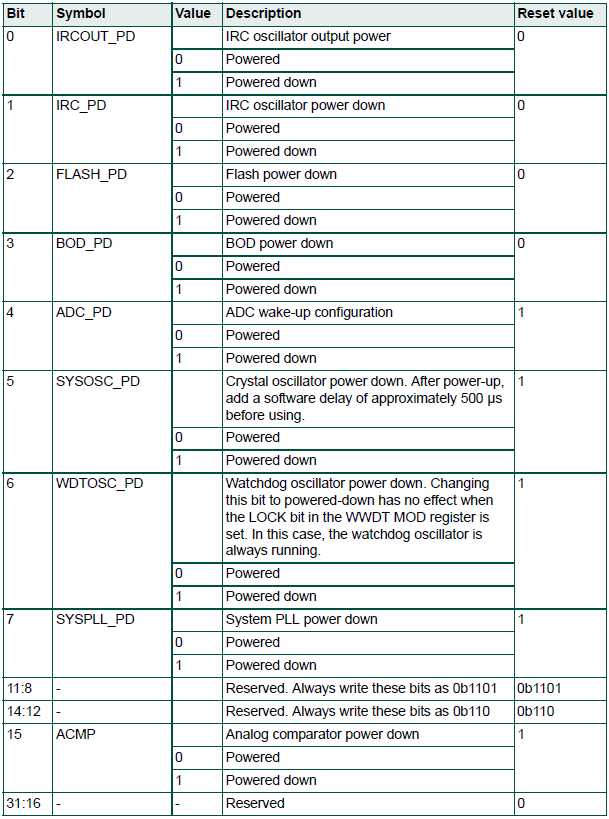

下表给出的是掉电配置寄存器PDRUNCFG的全部位结构,其字节地址为0x40048238。

(1)第0位(IRCOUT_PD)为内部RC振荡器输出掉电控制位,置0时上电,置1时掉电,默认为上电。

(2)第1位(IRC_PD)为内部RC振荡器掉电控制位,置0时上电,置1时掉电,默认为上电。

(3)第2位(FLASH_PD)为FLASH掉电控制位,置0时上电,置1时掉电,默认为上电。

(4)第3位(BOD_PD)为BOD掉电控制位,置0时上电,置1时掉电,默认为上电。

(5)第4位(ADC_PD)为ADC掉电控制位,置0时上电,置1时掉电,默认为掉电。

(6)第5位(SYSOSC_PD)为系统振荡器掉电控制位,置0时上电,置1时掉电,默认为掉电。

(7)第6位(WDTOSC_PD)为看门狗振荡器掉电控制位,置0时上电,置1时掉电,默认为掉电。

(8)第7位(SYSPLL_PD)为系统PLL掉电控制位,置0时上电,置1时掉电,默认为掉电。

(9)第8到14位为保留位,但它们有默认值,在对这些位进行写入操作时,必须按照默认值来写。

(10)第15位(ACMP)为模拟比较器掉电控制位,置0时上电,置1时掉电,默认为掉电。

(11)第16到31位为保留位。

从上表中可以看出,系统振荡器和系统PLL在默认情况下是掉电的,也就是说默认状态下它们处于不工作状态,要让它们工作就必须给它们的控制位置0(执行语句“LPC_SYSCON->PDRUNCFG &= ~(1 << 5)”和“LCP_SYSCON->PDRUNCFG &= ~(1 << 7)”),以更改为上电状态。

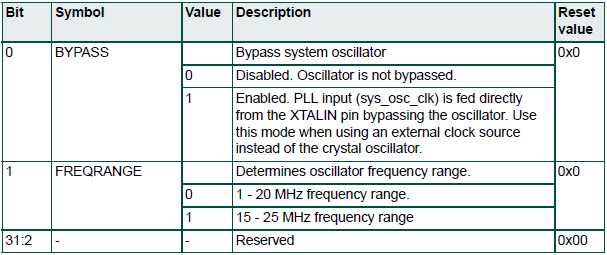

下表给出了系统振荡器控制寄存器SYSOSCCTRL的全部位结构,其字节地址为0x40048020。

(1)第0位(BYPASS)为系统振荡器旁路控制位,置0时未旁路,置1时被旁路,默认为未旁路。

(2)第1位(FREQRANGE)为低功耗振荡器确定频率范围选择位,置0时外部晶振的频率范围为1~20MHz,置1时为15~20MHz,默认为1~20MHz。

(3)第2到31位为保留位。

从上表中可以看出,如果要让系统振荡器工作,则SYSOSCCTRL寄存器的第0位就应该选择0,即不被旁路,只有从外部直接输入振荡信号的情况下才会选择旁路(比如使用有源晶振)。若系统使用12MHz外部晶振,则第1位应该选择0。实际上LPC824复位后的值就是该配置值,当然也可执行语句“LCP_SYSCON->SYSOSCCTRL = 0x00000000”来实现。

在配置了LPC824的时钟之后(无论是PLL时钟还是主时钟),都需要“更新”一下才能正常工作。根据官方数据手册,更新操作要给相应的更新允许寄存器进行“toggle”操作(即先向其写0再紧接着写1),这样之后时钟才能正常运行。

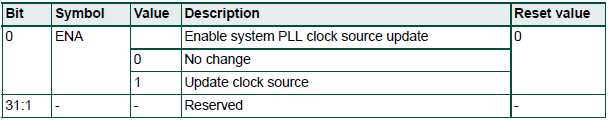

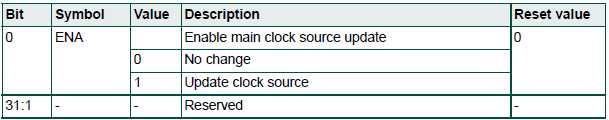

以下两表分别给出了系统PLL时钟源更新允许寄存器SYSPLLCLKUEN和主时钟源更新允许寄存器MAINCLKUEN的全部位结构,它们的字节地址分别为0x40048044、0x40048074。

(1)第0位(ENA)为允许系统PLL时钟源更新控制位,置0时无变化,置1时更新,默认为无变化。

(2)第1到31位为保留位。

(1)第0位(ENA)为允许主时钟源更新控制位,置0时无变化,置1时更新,默认为无变化。

(2)第1到31位为保留位。

在PLL时钟源和主时钟源更改后,紧接着要及时更新相应的允许寄存器才能让它们正常工作。此外还要注意,“toggle”后需要再次查询相应的允许寄存器是否已更新,若没有就需要等待直到其更新为止(例如在更新PLL时钟源更新允许寄存器SYSPLLCLKUEN后要执行语句“while (!(LPC_SYSCON->SYSPLLCLKUEN & 0x01));”,以等待其更新完成)。

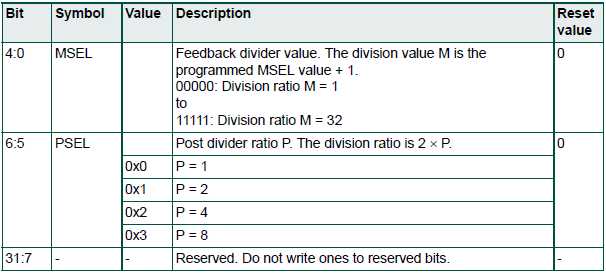

接下看PLL的配置,要让PLL对输入时钟进行倍频或分频,就得配置系统倍频控制寄存器,下表给出了系统倍频控制寄存器SYSPLLCTRL的全部位结构,其字节地址为0x40048008。

(1)第0到4位(MSEL)为反馈分频器的值,分频器的值M为MSEL+1。

(2)第5、6两位(PSEL)为后分频器的值,分频器的值为2×P。

(3)第7到31位为保留位,不能对它们写1。

PLL的输出频率要符合下面的公式:

上式中,Fclkout为PLL的输出频率,Fclkin为外部晶振的频率,FCCO的值必须在156MHz ~320MHz之间,M为倍频的倍数,P值要符合要求。若以12MHz的晶振做为输入,系统主时钟要为24MHz,则M=2(MSEL=0010),P的值只能取4(PSEL=10)才能满足公式要求。因此寄存器SYSPLLCTRL的值应该为100010(0x22),所以要配置此项可执行语句“LPC_SYSCON->SYSPLLCTRL = 0x00000022”。

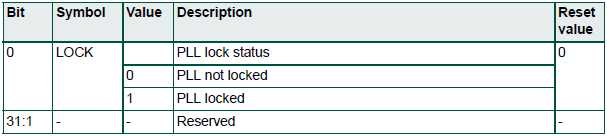

下表给出了倍频状态寄存器SYSPLLSTAT的全部位结构,其字节地址为0x4004800C。

(1)第0位(LOCK)为PLL锁定状态标志位,为0时未锁定,为1时锁定。

(2)第1到31位为保留位。

在改变了PLL的倍频之后,要查询SYSPLLSTAT寄存器来确定PLL锁定了没有,若没有就进入等待直到其锁定为止(执行语句“while (!(LPC_SYSCON->SYSPLLSTAT & 0x01));”)。

CPU要对GPIO进行操作,就必须给GPIO时钟信号,即需要使能GPIO的时钟。在默认情况下GPIO时钟是允许的,也可以对系统AHB时钟控制寄存器中相应的位进行操作来选择允许时钟。

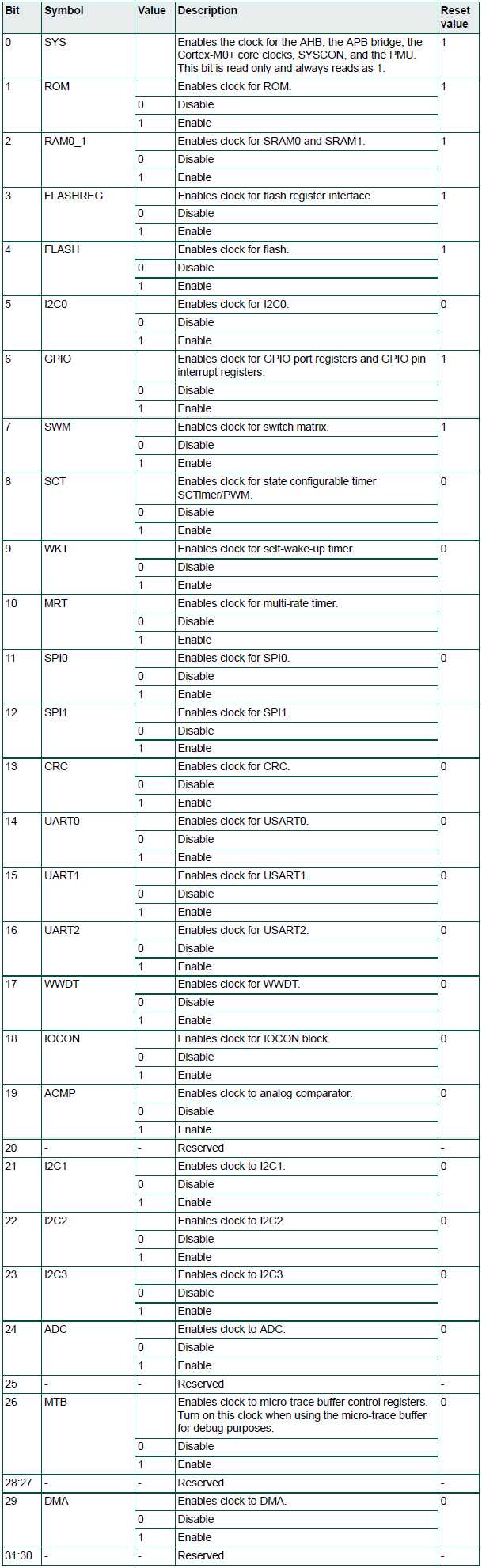

下表给出了系统AHB时钟控制寄存器SYSAHBCLKCTRL的全部位结构,其字节地址为0x40048080。

(1)第0位(SYS)为允许AHB时钟标志位,该位为只读,值为0时保留,为1时允许,默认为允许。

(2)第1位(ROM)为允许ROM时钟控制位,置0时禁止,置1时允许,默认为允许。

(3)第2位(RAM0_1)为允许SRAM0和SRAM1时钟控制位,置0时禁止,置1时允许,默认为允许。

(4)第3位(FLASHREG)为允许flash寄存器接口时钟控制位,置0时禁止,置1时允许,默认为允许。

(5)第4位(FLASH)为允许flash时钟控制位,置0时上电禁止,置1时允许,默认为允许。

(6)第5位(I2C0)为允许I2C0时钟控制位,置0时禁止,置1时允许,默认为禁止。

(7)第6位(GPIO)为允许GPIO时钟控制位,置0时禁止,置1时允许,默认为允许。

(8)第7位(SWM)为允许开关矩阵时钟控制位,置0时禁止,置1时允许,默认为允许。

(9)第8位(SCT)为允许配置SCTimer/PWM时钟控制位,置0时禁止,置1时允许,默认为禁止。

(10)第9位(WKT)为允许自唤醒定时器时钟控制位,置0时禁止,置1时允许,默认为禁止。

(11)第10位(MRT)为允许多速率定时器时钟控制位,置0时禁止,置1时允许,默认为禁止。

(12)第11位(SPI0)为允许SPI0时钟控制位,置0时禁止,置1时允许,默认为禁止。

(13)第12位(SPI1)为允许SPI1时钟控制位,置0时禁止,置1时允许,默认为禁止。

(14)第13位(CRC)为允许CRC时钟控制位,置0时禁止,置1时允许,默认为禁止。

(15)第14位(UART0)为允许USART0时钟控制位,置0时禁止,置1时允许,默认为禁止。

(16)第15位(UART1)为允许USART1时钟控制位,置0时禁止,置1时允许,默认为禁止。

(17)第16位(UART2)为允许USART2时钟控制位,置0时禁止,置1时允许,默认为禁止。

(18)第17位(WWDT)为允许WWDT时钟控制位,置0时禁止,置1时允许,默认为禁止。

(19)第18位(IOCON)为允许IOCON时钟控制位,置0时禁止,置1时允许,默认为禁止。

(20)第19位(ACMP)为允许模拟比较器时钟控制位,置0时禁止,置1时允许,默认为禁止。

(21)第20位为保留位。

(22)第21位(I2C1)为允许I2C1时钟控制位,置0时禁止,置1时允许,默认为禁止。

(23)第22位(I2C2)为允许I2C2时钟控制位,置0时禁止,置1时允许,默认为禁止。

(24)第23位(I2C3)为允许I2C3时钟控制位,置0时禁止,置1时允许,默认为禁止。

(25)第24位(ADC)为允许ADC时钟控制位,置0时禁止,置1时允许,默认为禁止。

(26)第25位为保留位。

(27)第26位(MTB)为允许微跟踪缓冲区控制寄存器时钟控制位,置0时禁止,置1时允许,默认为禁止。

(28)第27、28两位为保留位。

(29)第29位(DMA)为允许DMA时钟控制位,置0时禁止,置1时允许,默认为禁止。

(30)第30、31两位为保留位。

从上表中可以看出,第6位即为“通用输入输出端口GPIO”的时钟配置项,执行语句“LPC_SYSCON->SYSAHBCLKCTRL |= (1<<6)”就可以开启GPIO的时钟。在打开了GPIO的时钟后,PIO0_0~PIO0_28端口才能正常使用,不过默认状态就是开启的。

由上述可见,基于Cortex-M0+内核的微控制器由于强化了时钟配置,所以在一般情况下使用该类型的芯片,首要的任务就是配置正确的时钟。

下面给出一个时钟初始化的配置函数,可通过它来了解LPC824时钟配置的整个过程。

void SysCLK_config(void)

{

uint8_t i;

LPC_SYSCON->PDRUNCFG &= ~(1 << 5); //给系统振荡器上电

LPC_SYSCON->SYSOSCCTRL = 0x00000000; //系统振荡器未旁路,1~12MHz输入

for (i = 0; i < 200; i++) __nop(); //延时等待振荡器稳定

LPC_SYSCON->SYSAHBCLKCTRL |= (1 << 18); //使能IOCON时钟

LPC_IOCON->PIO0_8 &= ~(3 << 3); //把P0_8引脚配置为无上下拉电阻方式

LPC_IOCON->PIO0_9 &= ~(3 << 3); //把P0_9引脚配置为无上下拉电阻方式

LPC_SWM->PINENABLE0 &= ~(3 << 6); //把P0_8、P_9引脚配置为XTALIN、XTALOUT引脚

LPC_SYSCON->SYSAHBCLKCTRL &= ~(1 << 18); //禁止IOCON时钟

LPC_SYSCON->SYSPLLCLKSEL = 0x00000001; //PLL输入选择外部晶体振荡

LPC_SYSCON->SYSPLLCLKUEN = 0x00;

LPC_SYSCON->SYSPLLCLKUEN = 0x01; //先写0后写1更新时钟源

while (!(LPC_SYSCON->SYSPLLCLKUEN & 0x01)); //等待更新完成

LPC_SYSCON->SYSPLLCTRL = 0x00000022; //M=2、P=4,倍频后的时钟为24MHz

LPC_SYSCON->PDRUNCFG &= ~(1 << 7); //给PLL上电

while (!(LPC_SYSCON->SYSPLLSTAT & 0x01)); //等待PLL锁定

LPC_SYSCON->MAINCLKSEL = 0x00000003; //主时钟选择PLL倍频后的时钟

LPC_SYSCON->MAINCLKUEN = 0x00;

LPC_SYSCON->MAINCLKUEN = 0x01; //先写0后写1更新时钟源

while (!(LPC_SYSCON->MAINCLKUEN & 0x01)); //等待更新完成

LPC_SYSCON->SYSAHBCLKDIV = 0x00000001; //AHB为1分频,AHB时钟为24MHz

在上述配置中,系统外部时钟晶振为12MHz,则在该函数执行完后,LPC824时钟就会被设置为主时钟24MHz,AHB时钟24MHz。另外,由于在默认状态下,LPC824的PIO0_8和PIO0_9两个引脚是GPIO功能,所以要连接外部晶振先要把它们配置为XTALIN、XTALOUT引脚,否则芯片不能正常工作。

以上是关于思科时钟频率配置命令的主要内容,如果未能解决你的问题,请参考以下文章