verilog简单例化问题

Posted

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了verilog简单例化问题相关的知识,希望对你有一定的参考价值。

module DDS (clk , b , dds_out); input clk ; input [31:0] b; output [9:0] dds_out; adder10 u1 (.clock(clk) , .dataa(b) , .datab(dff_out)) ;dff32 u2 (.clock(clk) , .data(result) , .q(dff_out)) ;sin_rom u3 (.clock(clk) , .address(dff_out[31:22]) , .q(dds_out));

endmodule

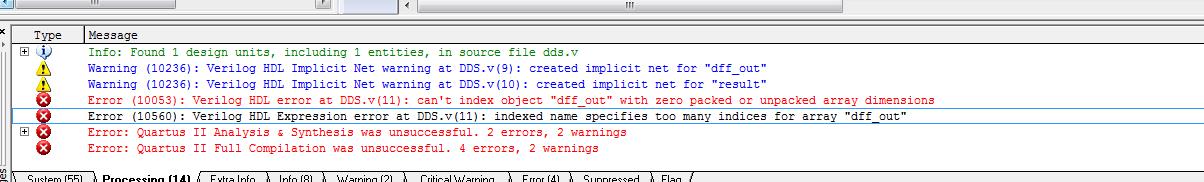

老是提示下面这种错误:

有见过的没,求解决?

应提前声明dff_out为:wire [31:0] dff_out ; 参考技术A 你的result和dff_out信号没有定义,.data(result)的意义不就是连接的意思么,但是result没有定义,那么你连接谁呢?dff_out是一个意思,所以加上定义再连接 参考技术B datab和q都给ddf_out赋值的,这里有问题

9.Verilog端口定义以及模块例化和调用

---------------------------------------------------------------------------------------

端口定义

模块定义以关键字 module 开始,以关键字 endmodule 结束。在module中,对模块的输入和输出进行定义,包括模块名,端口信号,端口声明和可选的参数声明等。

在Verilog中,端口的定义有三种类型, 输入input,输出output和双向端口inout。input、inout 类型不能声明为 reg 数据类型。output 可以声明为 wire 或 reg 数据类型。

具体定义举例如下:

方法1:

module count(

input i_clk,

input i_rst,

output reg[9:0]o_dout

);方法2:

module count(

i_clk,

i_rst,

o_dout

);

input i_clk;

input i_rst;

output [9:0]o_dout;

reg[9:0]o_dout;在方法1中,在module中,空格,然

以上是关于verilog简单例化问题的主要内容,如果未能解决你的问题,请参考以下文章