用八个与非门设计一个2线-4线变量译码器,要求输出低电平有效。画出逻辑图

Posted

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了用八个与非门设计一个2线-4线变量译码器,要求输出低电平有效。画出逻辑图相关的知识,希望对你有一定的参考价值。

这个与非门是几个输入的?

好吧,我来简单回答一下。

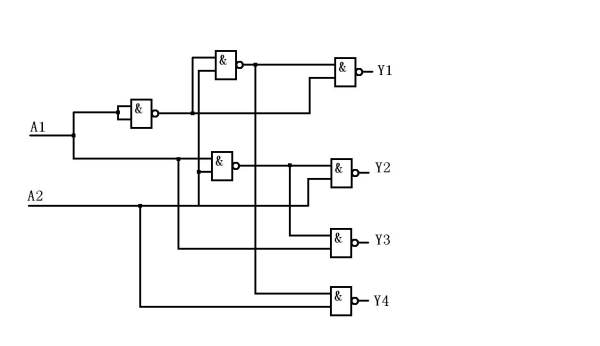

首先将两个输入端以A1和A2表示,四个输出分别以Y1,Y2,Y3,Y4表示。

那么,我们希望得到如下逻辑

A2 0 1

A1

0 0111 1011

1 1101 1110

0111表示Y1输出低电平,其余高电平,

1011表示Y2输出低电平,其余高电平,以此类推。

对Y1Y2Y3Y4画维诺图可以分别获得其逻辑表达式

Y1=((A1非&A2)非&A1非)非

Y2=(A2&(A1&A2)非)非

Y3=(A1&(A1&A2)非)非

Y4=((A1非&A2)非&A2)非

以上,可获得逻辑图如下

由于化简方式不同,逻辑电路也不同。

我化简结果中不存在A2非这一项,因此,少用了一个与非门。

本题目可通过7个与非门即可搭建。

来自:求助得到的回答 参考技术A用八个与非门设计一个2线-4线变量译码器,要求输出低电平有效。

画出逻辑图。

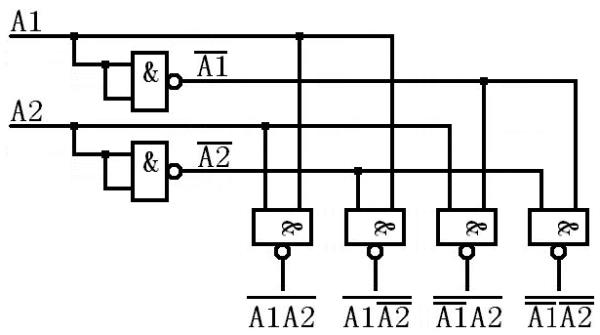

要求低电平有效,六个与非门,就足够了。

逻辑图如下:

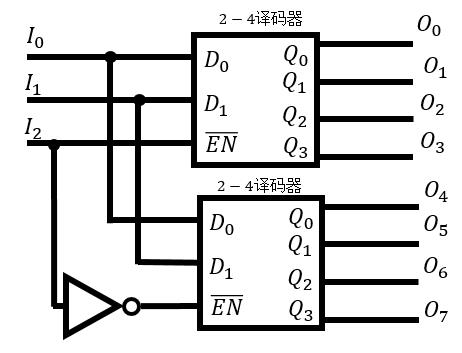

如何用双2-4线译码器转换为3-8线译码器?电路图怎么设计?

将双2-4译码器进行级联,即使用最高位作为两片2-4译码器的片选信号,将剩余位作为译码器片内地址线,就可以转换成3-8译码器。

设计方向

将双2-4译码器级联为3-8译码器

设计思路

由于译码器译码输出与输入对应,输入端位000~111对应选择输出端的Q0~Q7,故可以根据输入端最高位将3-8线译码器分割为低4位和高4位,结合逻辑地址分段的思路使用两个2-4线译码器的表示对应的Q0~Q3和Q4~Q7。

由于Q0~Q3和Q4~Q7除了输入端的最高位不同一一对应,因此可以输入端最高位控制2-4译码器的使能端,将剩余的输入作为片内地址去控制有效译码器的输出。

电路原理

设计分析

该设计通过输入端最高位作为片选信号,将输入端最低位和第二位作为片内地址线选择片内输出,实现两个2-4译码器的级联形成3-8译码器。

注意事项

译码器根据其内部结构不同输出端和使能端均有高电平有效和低电平有效两种,实际使用应根据相关技术手册调整,即调整反相器的位置和输出的默认电平,常使用上拉电阻和下拉电阻。

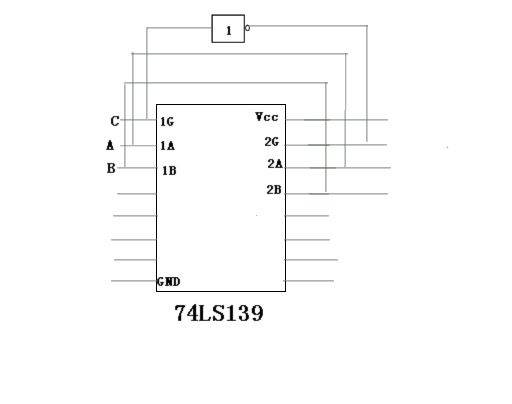

参考技术A 我就不用给插图了啊,直接讲解,我想你应该能听懂,2-4线译码器我们以 74xx139 为例,将两个74139的输入高位与高位,低位与低位连接起来,就是两个输入的A0与A0,A1与A1连接起来,输入Z接A0,Y接A1,将第三个输入X直接送至其中一个139的使能端,我们假设送至139(2),这第三个输入X通过一个非门送至139(1)(就是另一个139),那么当输入为000-011的时候只有139(2)使能,对应输出各个有效信号,当输入为100-111的时候,有139(1)使能,对应有输出。本回答被提问者采纳 参考技术B基本就是这个图了

控制好2个使能信号(G)

以上是关于用八个与非门设计一个2线-4线变量译码器,要求输出低电平有效。画出逻辑图的主要内容,如果未能解决你的问题,请参考以下文章