AHB2APB桥接器设计——同步桥设计的介绍

Posted 摆渡沧桑

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了AHB2APB桥接器设计——同步桥设计的介绍相关的知识,希望对你有一定的参考价值。

🔥点击进入【硬件安全】社区,查看更多精彩内容🔥

📢 声明:

🥭 作者主页:【摆渡沧桑的CSDN主页】。

⚠️ 未经作者允许,禁止转载。

⚠️ 本文为非盈利性质,目的为个人学习记录及知识分享。因能力受限,存在知识点分析不正确的可能。若您参考本文造成了不良后果,本人不承担相关责任。

⚠️ 若本文所采用图片或相关引用侵犯了您的合法权益,请联系我进行删除。

😄 欢迎大家指出文章错误,欢迎同行与我交流 ~

文章目录

一、AHB2APB同步桥的整体介绍

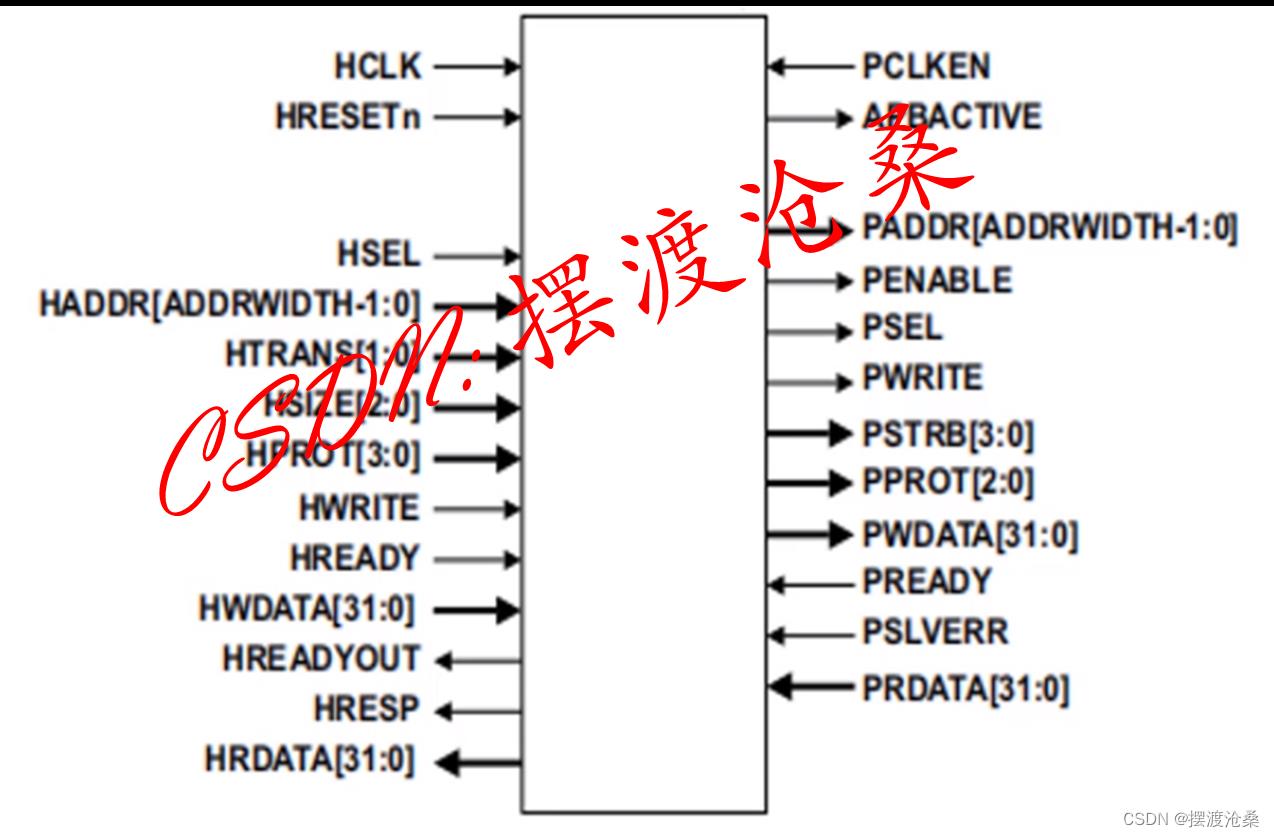

1.1 模块框图

模块框图:

可以分为三个部分来分析整个同步桥的设计:

主要功能将左边AHB的信号转换为APB的信号,同步桥只有一个时钟和复位,信号转换主要由一些组合逻辑来实现

1. 第一部分: 主要有HCLK,HRESETn, PCLKEN, APBACTIVE这些时钟、复位控制信号

2. 第二部分: 主要以H开头的信号,主要是AHB BUS上的信号

3. 第三部分: 主要以P开头的信号,主要是APB BSU上的信号

二、AHB2APB同步桥的信号接口

2.1 系统信号接口

| 信号 | 方向 | 位宽 | 描述 |

|---|---|---|---|

| HCLK | I | 1 | 同步桥AHB和APB的同步时钟 |

| HRESETn | I | 1 | 同步桥AHB和AOB的同步复位 |

| PCLKEN | I | 1 | PCLK的使能信号 |

| APBACTIVE | O | 1 | 指示APB桥工作信号,可以应用于后级APB BUS上的CLK GATE |

2.2 AHB BUS一侧的接口信号(AHB Slave接口信号)

有关AHB的详细协议介绍参考AMBA总线部分,此部分仅介绍模块已有的接口信号

| 信号 | 方向 | 位宽 | 描述 |

|---|---|---|---|

| HSEL | I | 1 | 每个AHB从机的选通信号。每个从机有自己独立的从机选择信号,并用该信号,表示当前传输是都选中该从机,一般是地址信号的译码 |

| HADDR | I | 16 | AHB 16 bit地址总线 |

| HTRANS | I | 2 | AHB的传输类型,IDLE, BUSY, NONSEQ, SEQ四种传输类型 |

| HSIZE | I | 3 | AHB每一个transfer传输数据的大小,以字节为单位 |

| HPROT | I | 4 | AHB保护控制信号,需要slave带有保护功能,一般不作使用。主要给希望执行保护级别的模块使用 |

| HWRITE | I | 1 | AHB写信号,高为写,低为读 |

| HWDATA | I | 32 | AHB写数据 |

| HREADY | I | 1 | AHB总线从机的输入ready信号 |

| HRDATA | O | 32 | AHB读数据 |

| HREADYOUT | O | 1 | AHB桥输出的ready信号,一般与HREADY对应 |

| HRESP | O | 1 | AHB状态相应信号 |

2.3 APB BSU一侧的接口信号 (APB Master接口)

| 信号 | 方向 | 位宽 | 描述 |

|---|---|---|---|

| PADDR | O | 16 | APB地址信号 |

| PENABLE | O | 1 | APB使能信号 |

| PWRITE | O | 1 | APB写信号,高为写,低为读 |

| PSTRB | O | 4 | APB写选通信号,表示哪个字节有效 |

| PPROT | O | 3 | APB Slave的保护类型。提供保护机制 |

| PWDATA | O | 32 | APB写数据 |

| PSEL | O | 1 | APB的设备的选通有效信号 |

| PRDATA | I | 32 | APB读数据 |

| PREADY | I | 1 | APB ready信号 |

| PSLVERR | I | 1 | APB 传输错误信号 |

2.4 特殊型号说明

2.4.1 APBACTIVE信号:同步桥的工作状态信号

APBACTIVE = 1, 说明此时同步桥处于工作状态,有信号在AHB和APB之间传输

APBACTIVE可以用作APB子系统时钟门控信号,供外设做低功耗处理。

2.4.2 PCLKEN信号:(处理PCLK与HCLK之间的关系,需要控制PCLKEN信号)

如果PCLK = HCLK,则PCLKEN 输入1;如果PCLK = 1/2 HCLK,则PCLKEN = PCLK

如果需要HCLK = N * PCLK,那么PCLKEN 需要在PCLK的上升沿的前一拍置位

在不增加逻辑复杂度的情况下,在一定程度上,增加了总线的灵活性,降低了功耗

2.4.3 AHB中的HREADY信号:

- 作为AHB的从机,从机必须由一个输入ready和一个输出ready信号

- HREADY信号: 同步桥的输入信号,外部AHB仲裁器收集各个AHB Slave设备的HREADYout信号,然后做出判断,在送给Slace 端口。表示AHB总线是否READY

- HREADYout信号:同步桥的输出信号。代表同步桥是否准备好接收或者发送数据。在同步桥的数据转换中,APB读写操作至少需要两个时钟周期,设计时需要让AHB在合适的时候拉低HREADYout信号,添加合适的等待周期,从而实现AHB到APB的数据转换。

2.4.4 AMBA APB 3.0信号

- PREADY

APB Slave通过PREADY信号直接来告诉master,Slave的Ready状态。如果PREADY为高,表示可以接收读写操作,如果PREADY为低,表示Master需要等待- PSLVERR

加入Slave反馈给Master Error 反馈功能

2.4.5 AMBA APB 4.0信号

- PSTRB[3:0]

在写操作中,用来指示,byte lane (即多bit字节中哪一个字节是有效的)

在读操作应该改全1,读操作不考虑- PPROT[2:0]

在新版的 APB 4.0协议中,可以采用作为外设访问权限的设置

1. PPROT[0]:0:正常可以访问;1:私有访问,特权级别

2. PPROT[1]:0:安全访问;1:非安全访问

3. PPROT[2]:0:数据;1:指令

三、AHB2APB同步桥的设计参数

定义一些参数,来让代码更加灵活,便于修改

- ADDRWIDTH:16, 地址空间,对应64 KB的寻址空间

- REGISTER_WDATA: 1, (主要定义AHB到APB在数据传输是否对寄存器需要处理)

优点:AHB2APB的同步桥PWDATA会变成寄存器输出,有利于时序优化

缺点:会增加HWDATA到PWDATA的输出延迟- REGISTER_RDATA: 1 (主要定义APB到AHB输出的读数据做寄存器处理)

优点:AHB2APB的同步桥PRDATA会变成寄存器输出,有利于时序优化

缺点:会增加PRDATA到HRDATA输出延迟

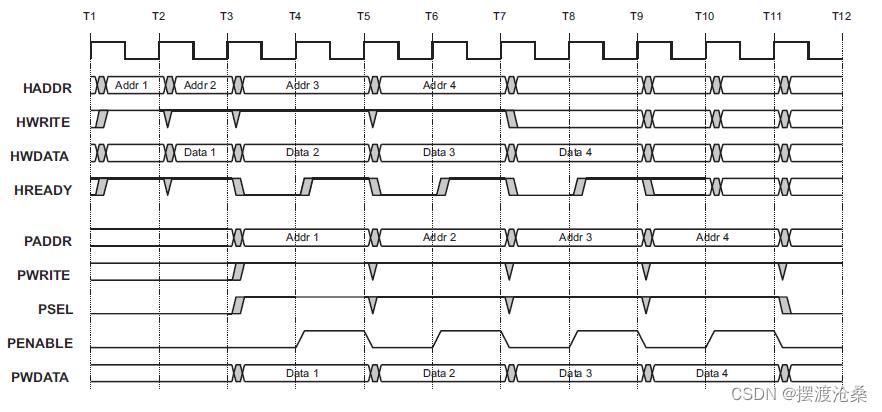

四、AHB2APB同步桥的时序图

4.1 burst写传输:

AHB这一侧,每个一个时钟周期会受到一个HREADY = 0的信号,等待APB将数据写入

4.2 back-back 传输(写读循环)

不经常出现一个写,接着一个读传输

🔥 精选往期 《AMBA总线》系列文章🔥

【协议篇】

AMBA总线协议(一)——一文看懂APB总线协议

AMBA总线协议(二)——一文看懂AMBA2 AHB2与AMBA3 AHB-Lite总线协议的区别

AMBA总线协议(三)——一文看懂AHB总线所有协议总结(AHB2 & AHB-Lite & AHB5 )

AMBA总线协议(四)—— Multi-Layer AHB System (多层AHB总线架构)

AMBA总线协议(五)—— AXI3 协议接口信号介绍1

AMBA总线协议(六)—— 一文看懂 AXI3 协议原子访问2

【实践篇】

AHB2APB桥接器设计(1)——基本原理

AHB2APB桥接器设计(2)——同步桥设计的介绍

以上是关于AHB2APB桥接器设计——同步桥设计的介绍的主要内容,如果未能解决你的问题,请参考以下文章