Cortex M3内核架构

Posted a1314521531

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了Cortex M3内核架构相关的知识,希望对你有一定的参考价值。

CortexM3内核架构

宗旨:技术的学习是有限的,分享的精神是无限的。

1、ARMCortex-M3处理器

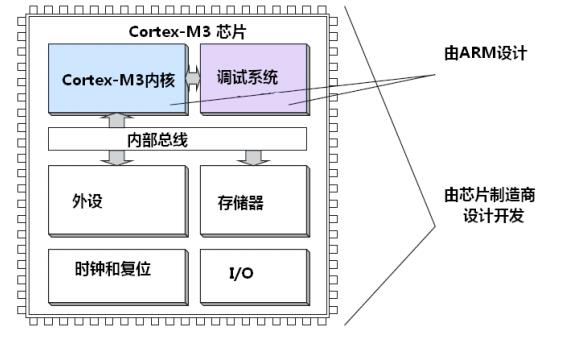

Cortex-M3处理器内核是单片机的中央处理单元( CPU)。 完整的基于CM3的MCU还需要很多其它组件。在芯片制造商得到CM3处理器内核的使用授权后,它们就可以把CM3内核用在自己的硅片设计中,添加存储器,外设, I/O以及其它功能块。不同厂家设计出的单片机会有不同的配置,包括存储器容量、 类型、 外设等都各具特色。

款式A:设计用于高性能的“开放应用平台”——越来越接近电脑了

款式R:用于高端的嵌入式系统,尤其是那些带有实时要求的——又要快又要实时。

款式M:用于深度嵌入的,单片机风格的系统中——ARM v7架构Thumb-2指令集

Cortex-M3 是一个 32 位处理器内核。CM3 采用了哈佛结构,拥有独立的指令总线和数据总线,指令总线和数据总线共享同一个存储器空间4G。

2、Cortex M3内核架构

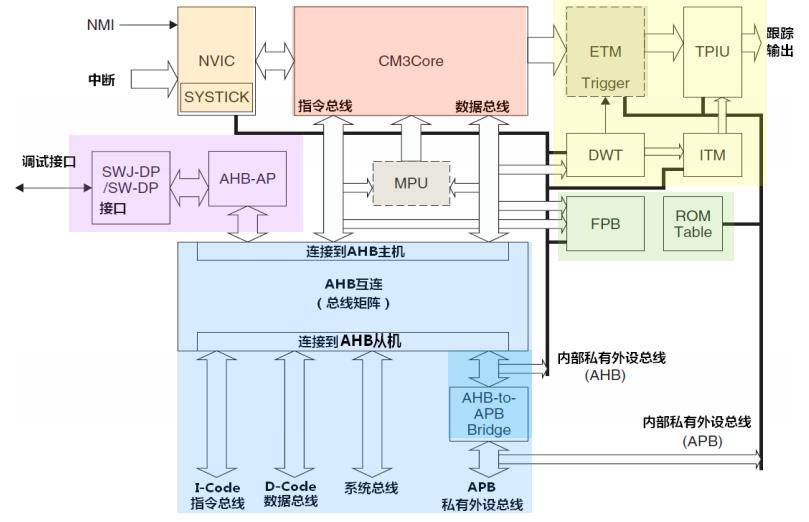

1、Cortex M3处理器核心

2、可嵌套中断向量控制器NVIC

3、总线阵列

4、存储保护单元MPU

5、Flash分区与断点FPB

6、数据监测点与跟踪DWT

7、仪表跟踪宏单元ITM

8、嵌入跟踪宏单元ETM

9、跟踪端口接口单元TPIU

10、AHB访问端口

11、串口线或JTAG调试口

12、CoresightROM表

13、唤醒中断控制器WIC

三、Cortex M3的总线接口

1、I-Code总线

I-Code 总线是一条基于AHB-Lite 总线协议的 32 位总线,负责在 0x0000_0000 – 0x1FFF_FFFF 之间的取指操作。取指以字的长度执行,即使是对于 16 位指令也如此。因此 CPU 内核可以一次取出两条 16 位 Thumb 指令。

2、D-Code总线

D-Code 总线也是一条基于 AHB-Lite 总线协议的 32 位总线,负责在0x0000_0000 – 0x1FFF_FFFF之间的数据访问操作。尽管 CM3支持非对齐访问,但你绝不会在该总线上看到任何非对齐的地址,这是因为处理器的总线接口会把非对齐的数据传送都转换成对齐的数据传送。因此,连接到 D-Code总线上的任何设备都只需支持 AHB-Lite 的对齐访问,不需要支持非对齐访问。

3、系统总线

系统总线也是一条基于 AHB-Lite 总线协议的 32 位总线,负责在0x2000_0000 – 0xDFFF_FFFF 和0xE010_0000– 0xFFFF_FFFF 之间的所有数据传送,取指和数据访问都算上。和 D-Code 总线一样,所有的数据传送都是对齐的。

4、外部私有外设总线

这是一条基于 APB 总线协议的 32 位总线。此总线来负责 0xE004_0000 – 0xE00F_FFFF 之间的私有外设访问。但是,由于此 APB存储空间的一部分已经被 TPIU、 ETM 以及 ROM 表用掉了,就只留下了 0xE004_2000-E00F_F000 这个区间用于配接附加的(私有)外设。

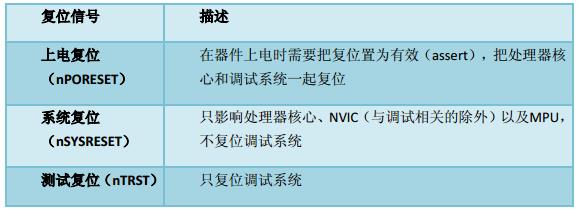

四、复位信号

以上是关于Cortex M3内核架构的主要内容,如果未能解决你的问题,请参考以下文章