ZYNQ之HLS学习----开篇实验

Posted 鲁棒最小二乘支持向量机

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了ZYNQ之HLS学习----开篇实验相关的知识,希望对你有一定的参考价值。

1 Vivado HLS简介

Xilinx 推出的 Vivado HLS 工具可以直接使用C、C++或 System C 来对 Xilinx 系列的 FPGA 进行编程

FPGA 设计中从底层向上一共存在着四种抽象层级,依次为:结构性的、RTL、行为性的和高层

Vivado HLS 的功能简单地来说就是把 C、C++ 或 SystemC 的设计转换成 RTL 实现,然后就可以在 Xilinx FPGA 或 Zynq 芯片的可编程逻辑中综合并实现了

2 开篇实验

实验任务是使领航者底板上的 PL LED0 和 PL LED1 以固定的频率交替闪烁,要求使用 C 或C++语言完成设计,然后综合得到 RTL 级实现并进行验证

2.1 HLS设计

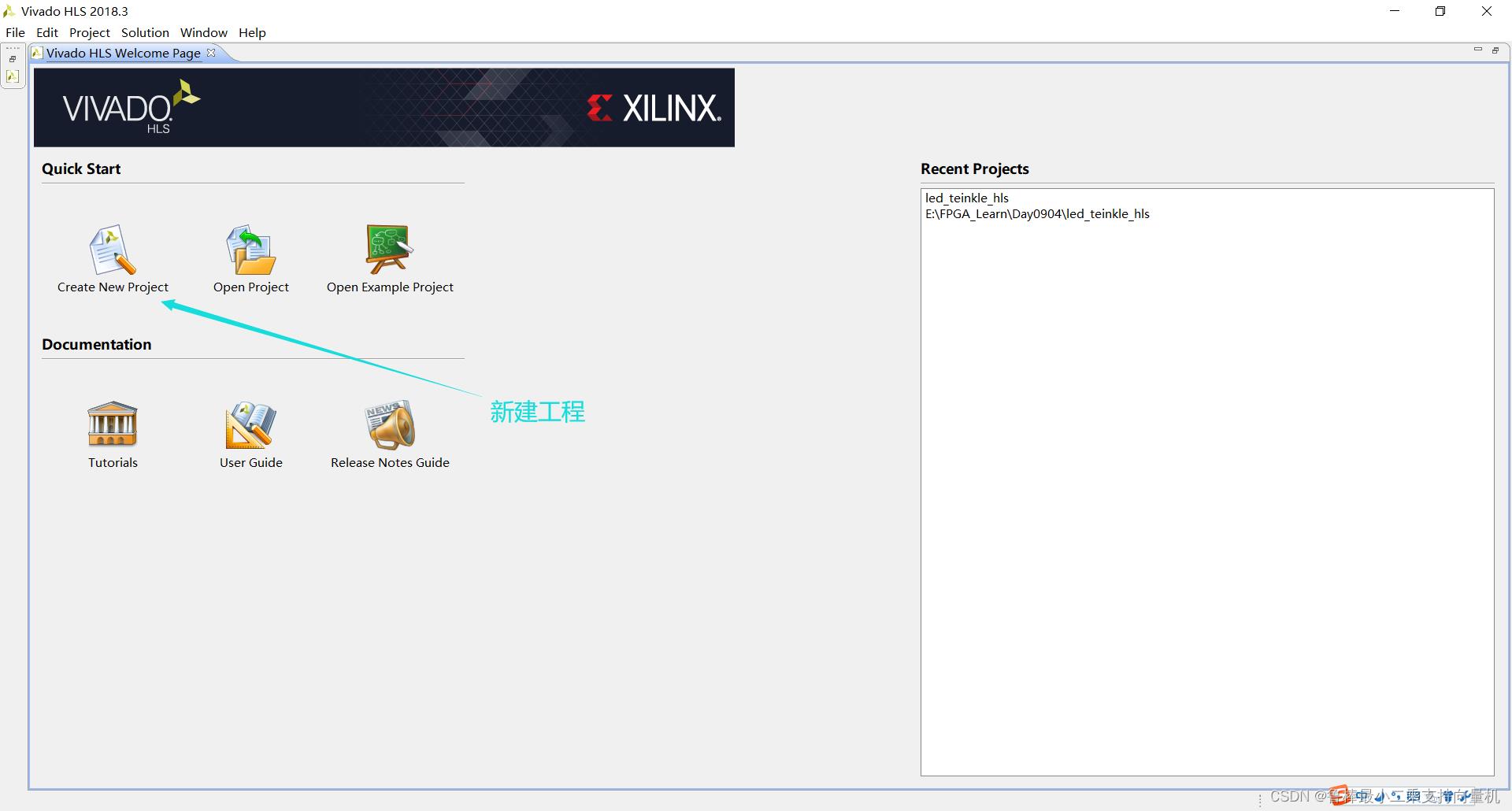

打开 Vivado HLS 工具,界面如图所示:

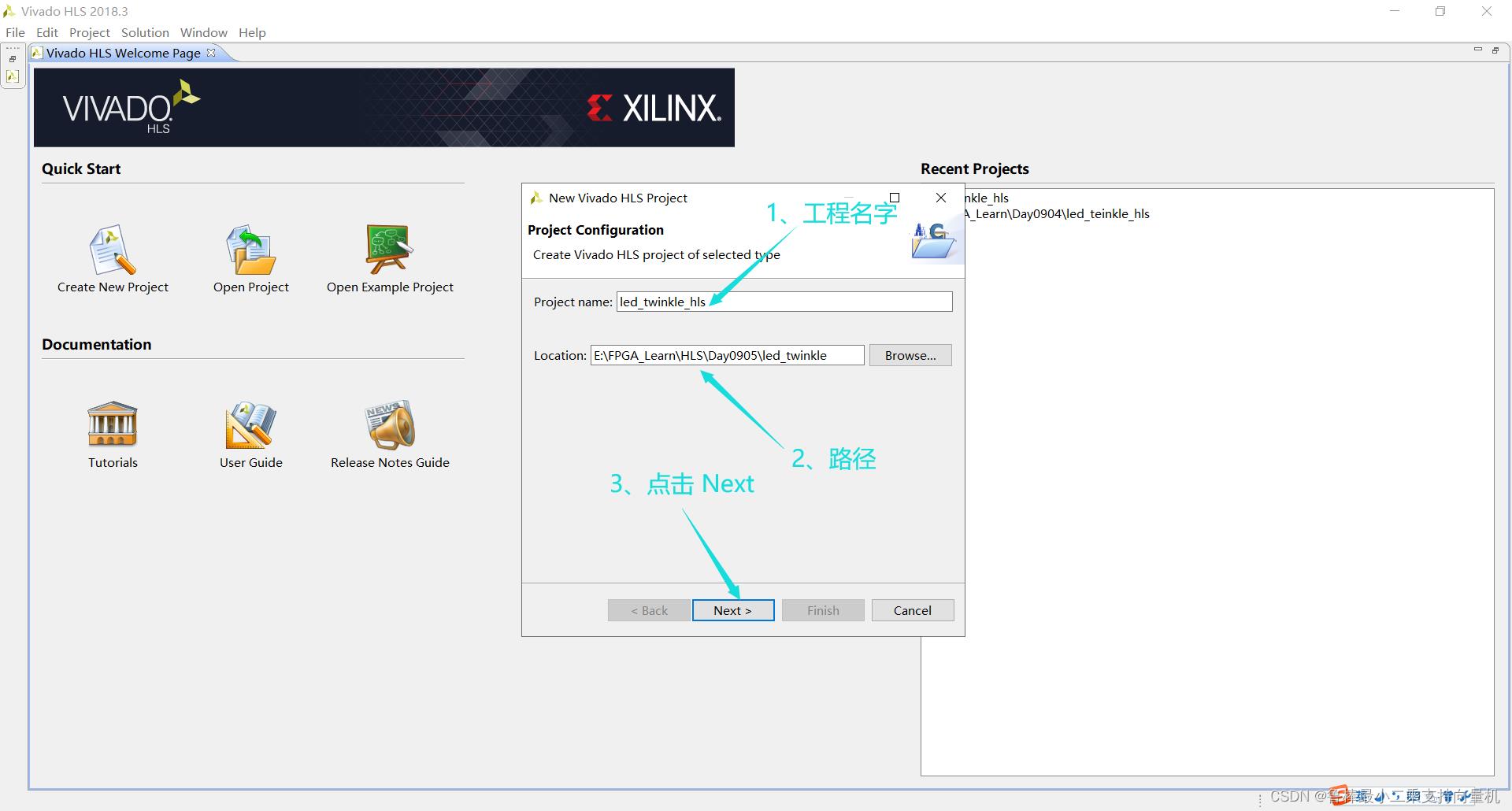

如下图,创建一个新的工程,输入工程名和路径,点击Next:

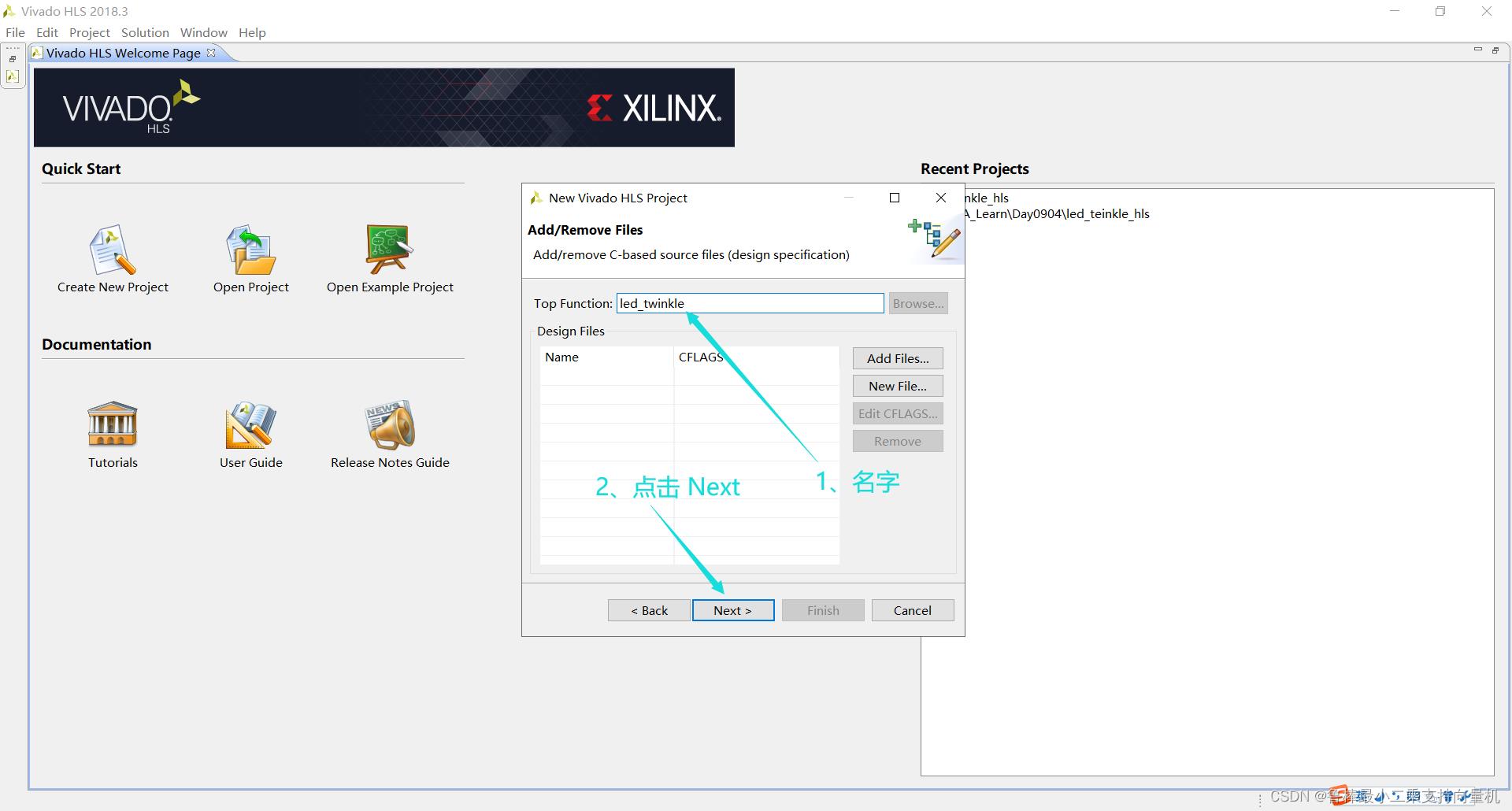

如下图,继续点击Next:

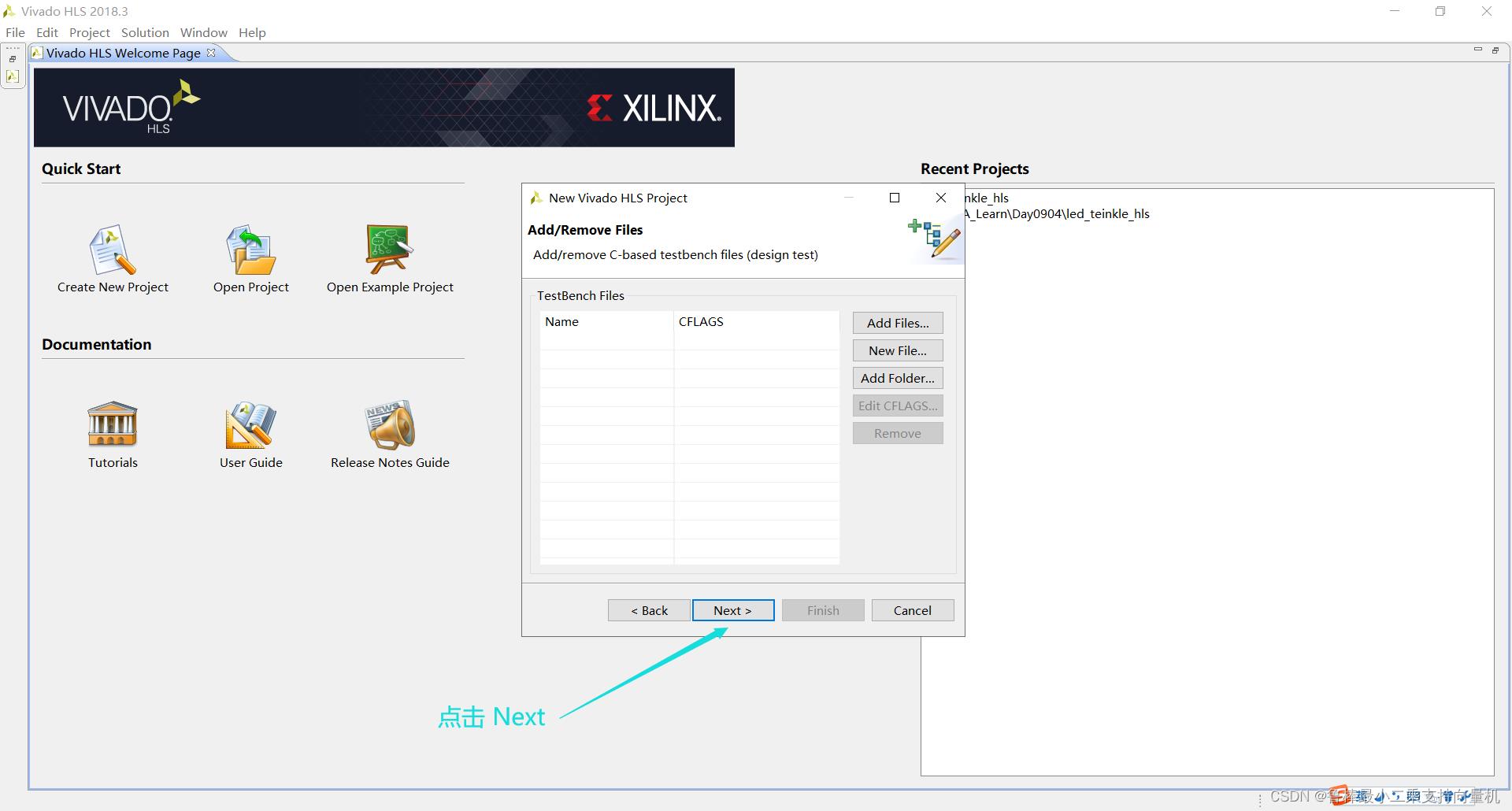

进入如下界面,继续点击Next:

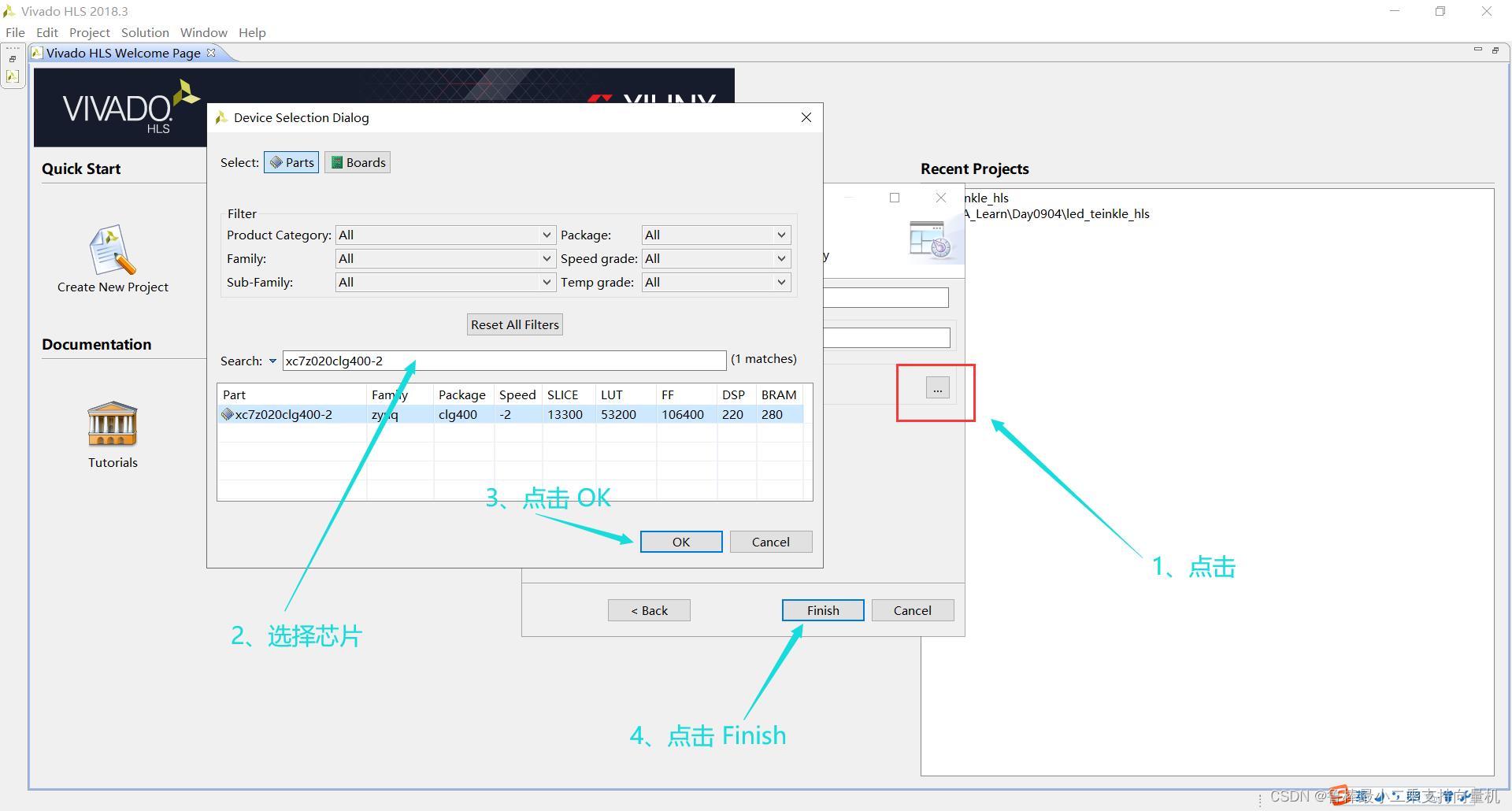

选择芯片型号,如图所示:

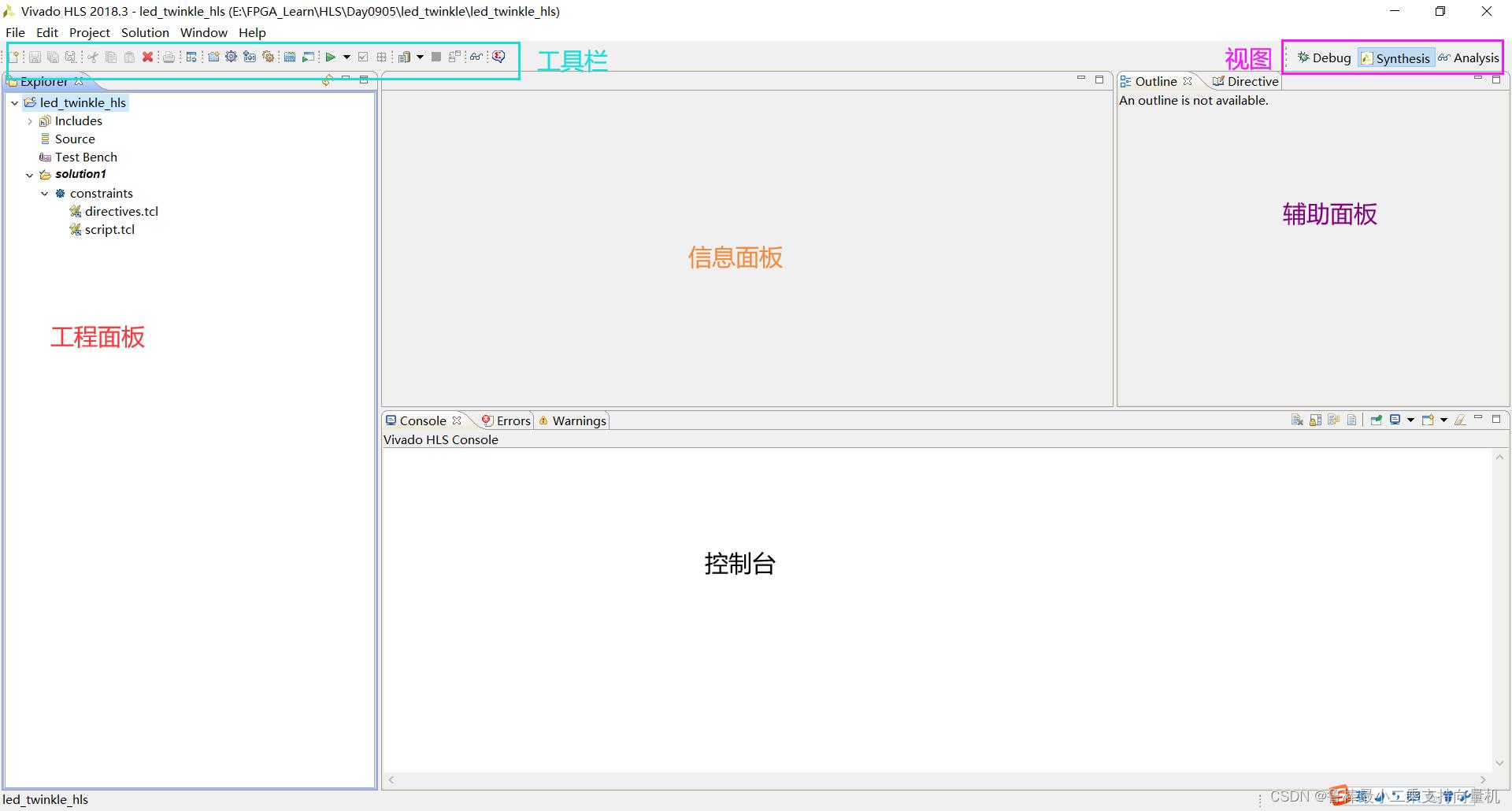

创建工程完成,界面如下:

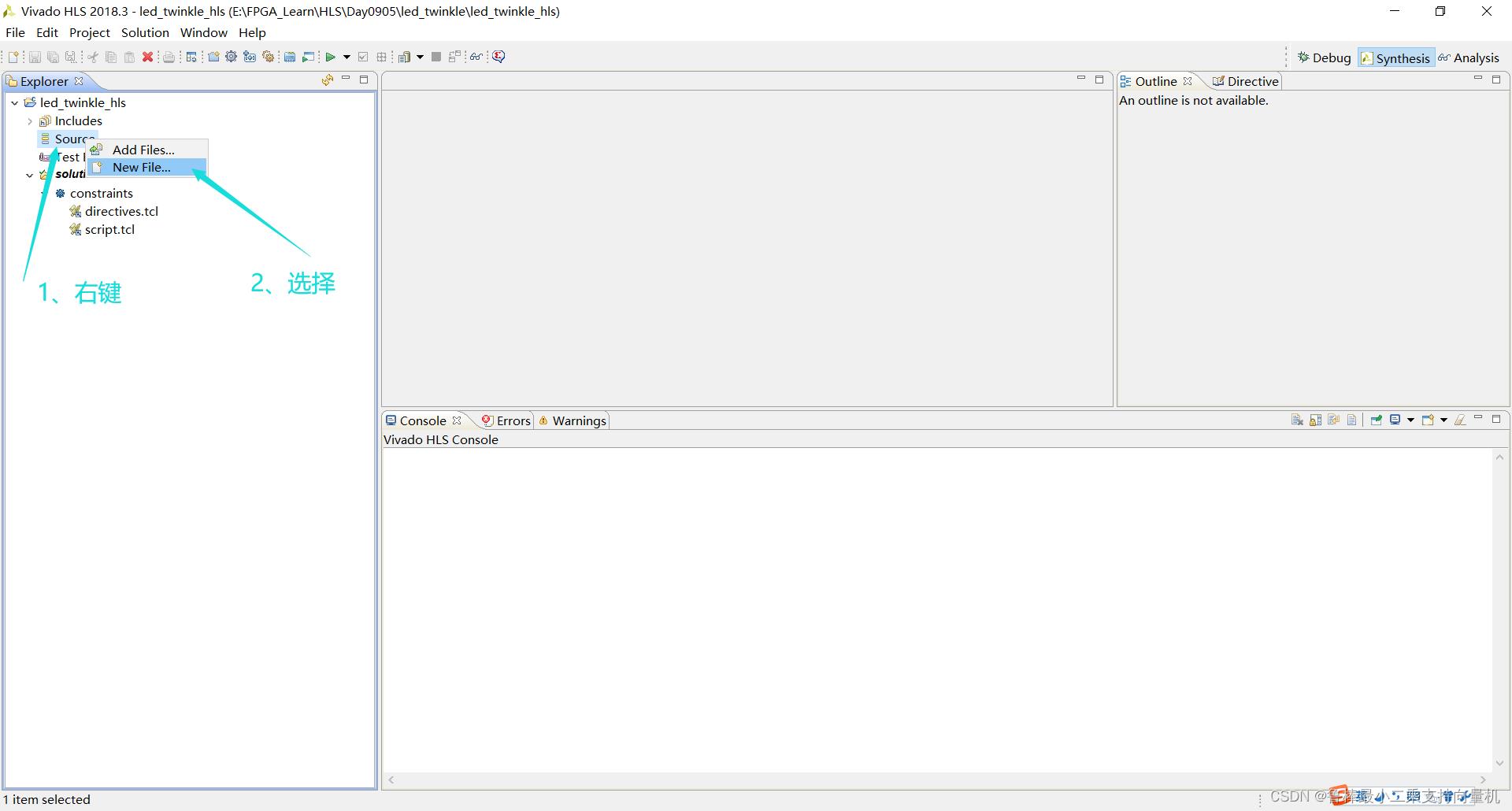

按下步骤新建源文件:

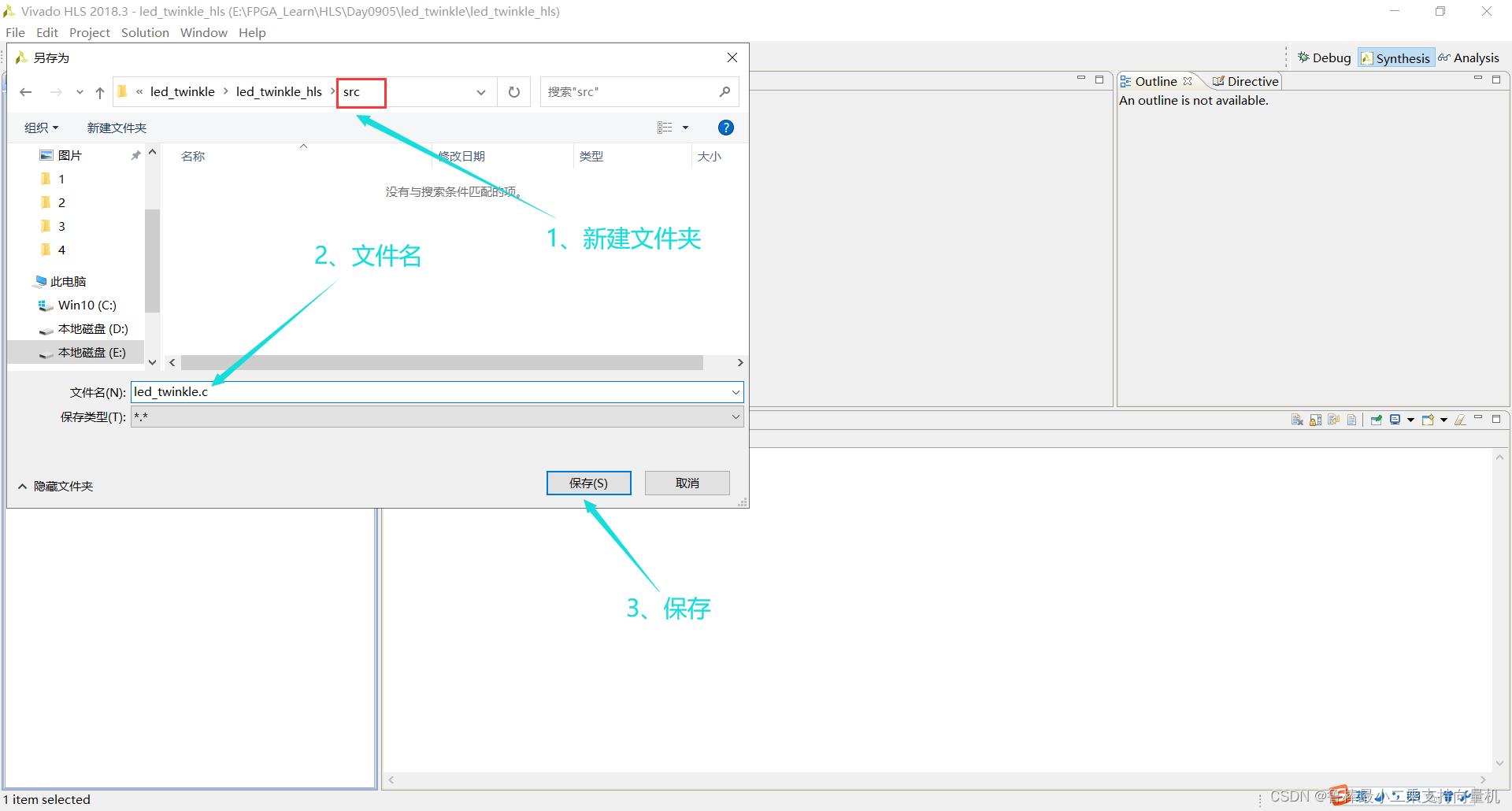

将源文件保存在工程目录下新建的名为src的文件下:

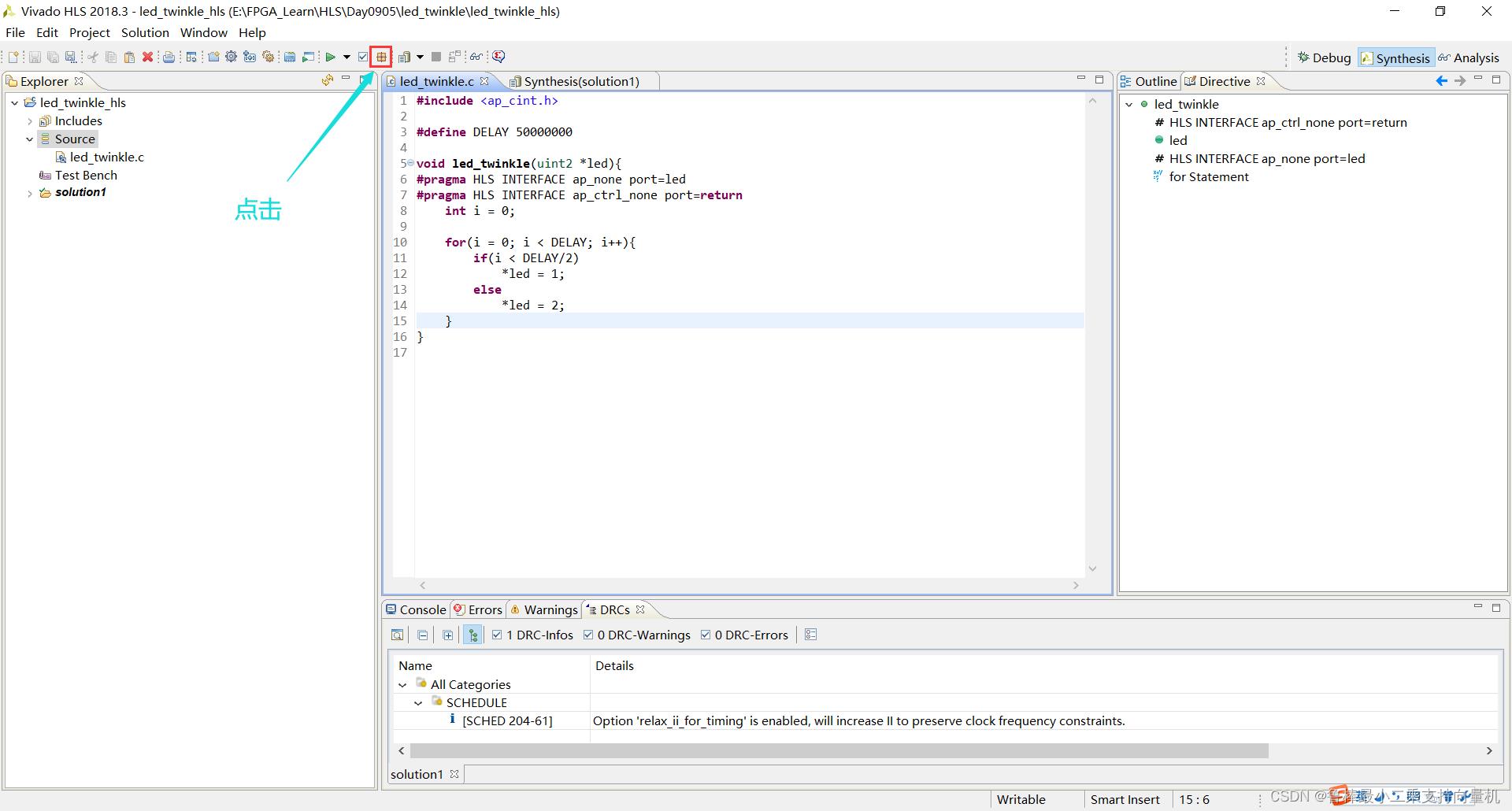

本次试验代码如下:

#include <ap_cint.h>

#define DELAY 50000000

void led_twinkle(uint2 *led )

int i = 0;

for(i = 0; i < DELAY; i++)

if(i < DELAY/2)

*led = 1;

else

*led = 2;

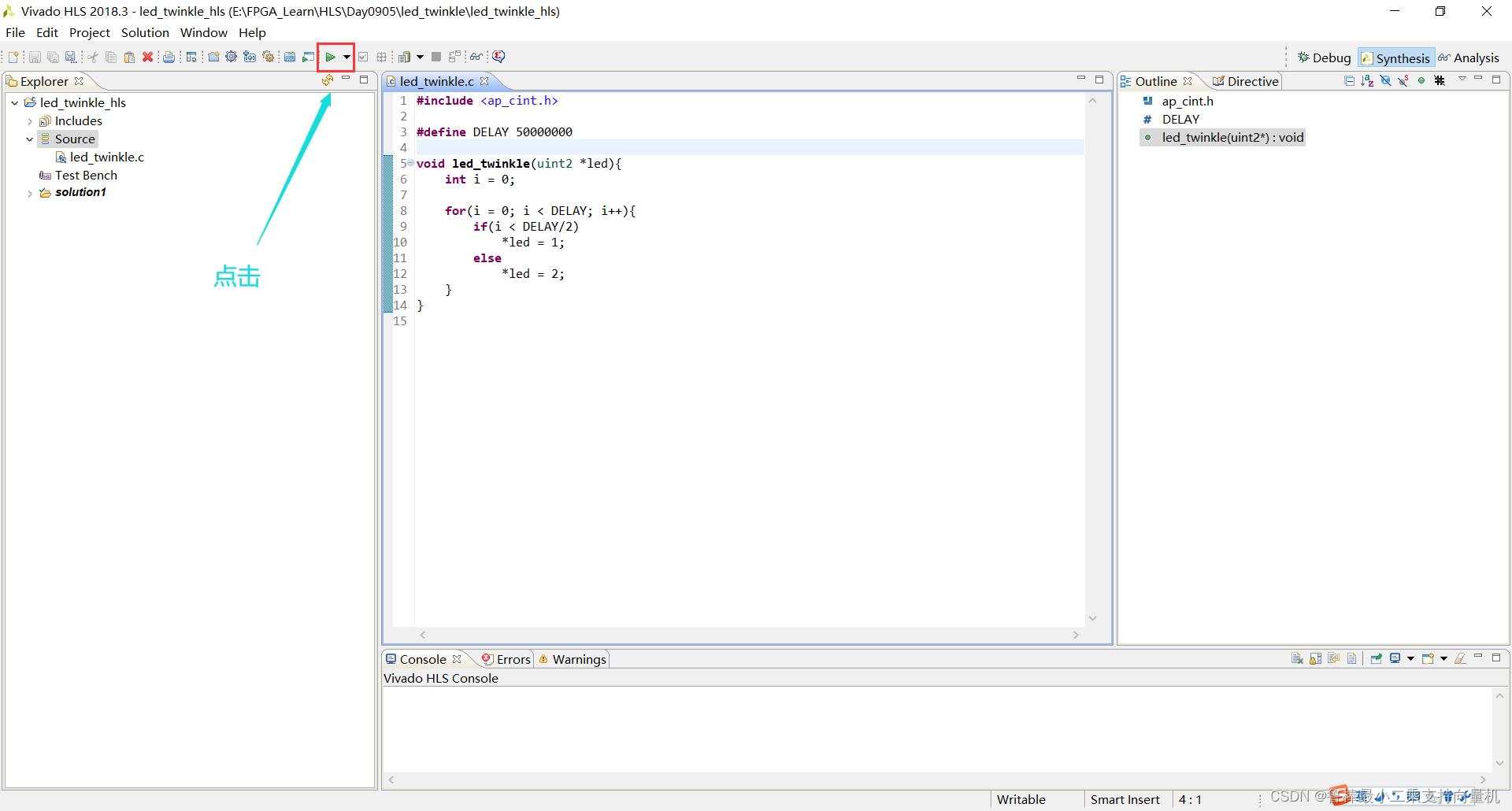

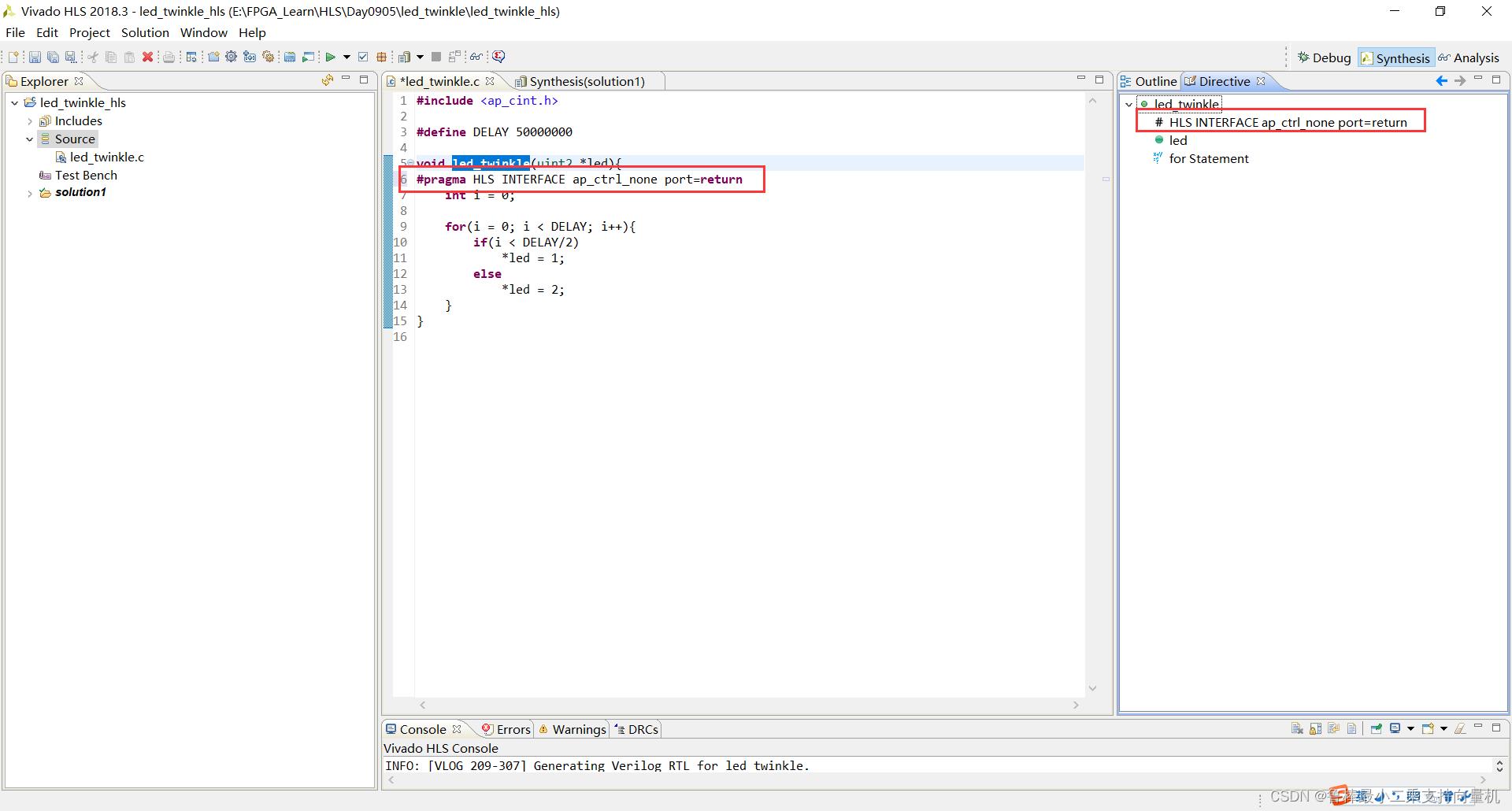

输入代码,进行综合,如图所示:

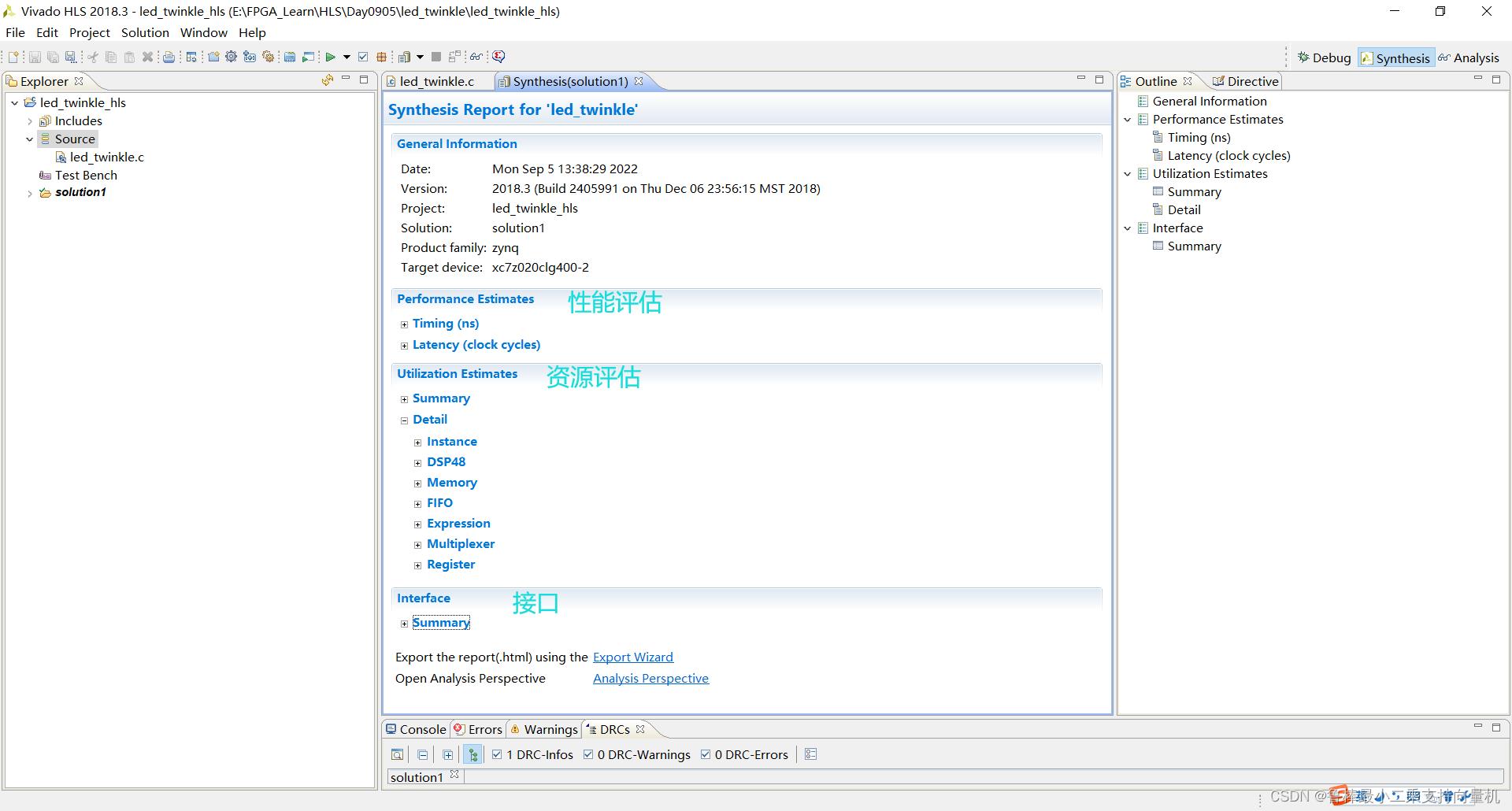

综合结果的报告,如图所示:

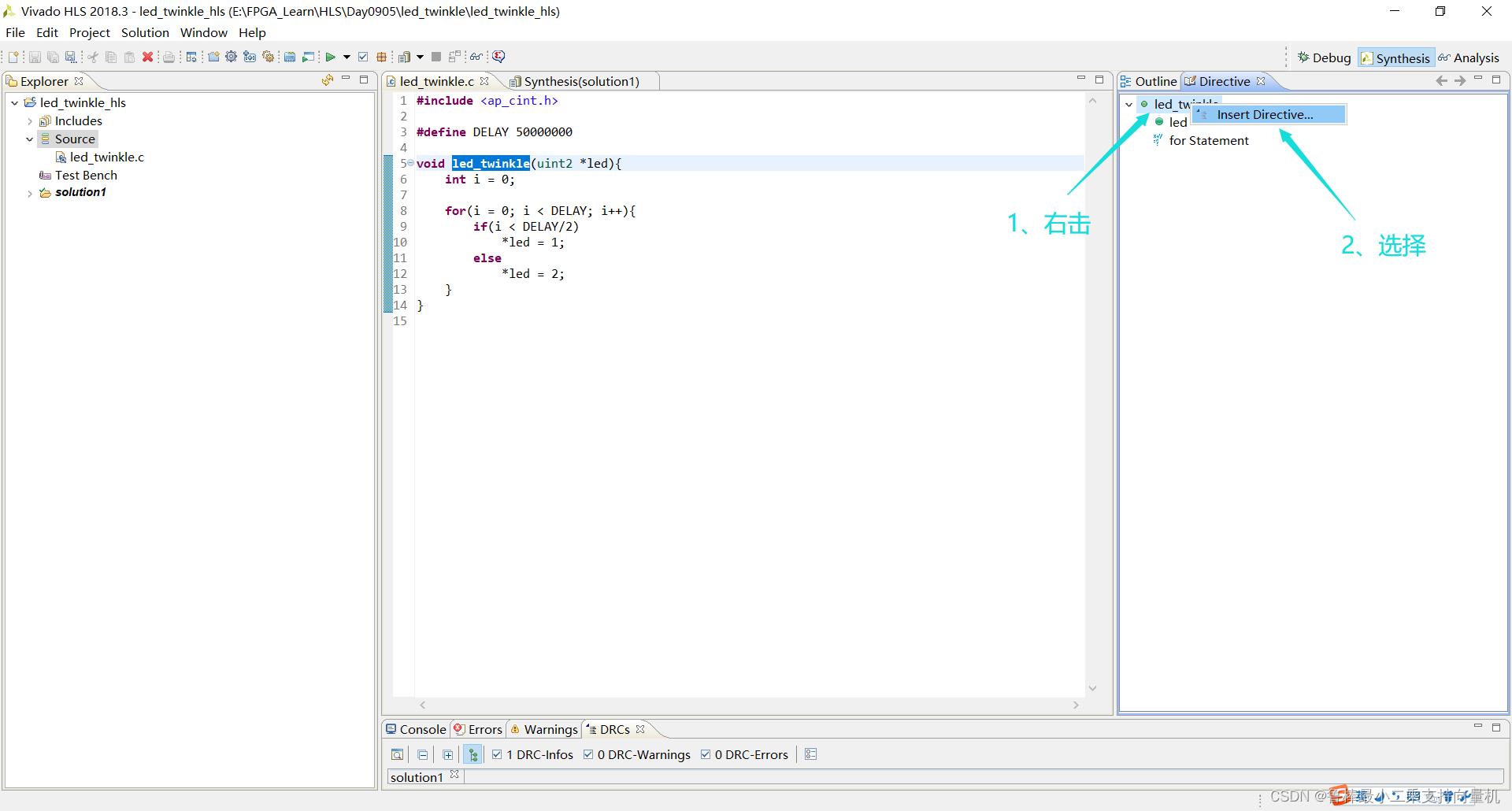

打开 Directive 标签页,右击 led_twinkle ,选择Insert Directive,如图所示:

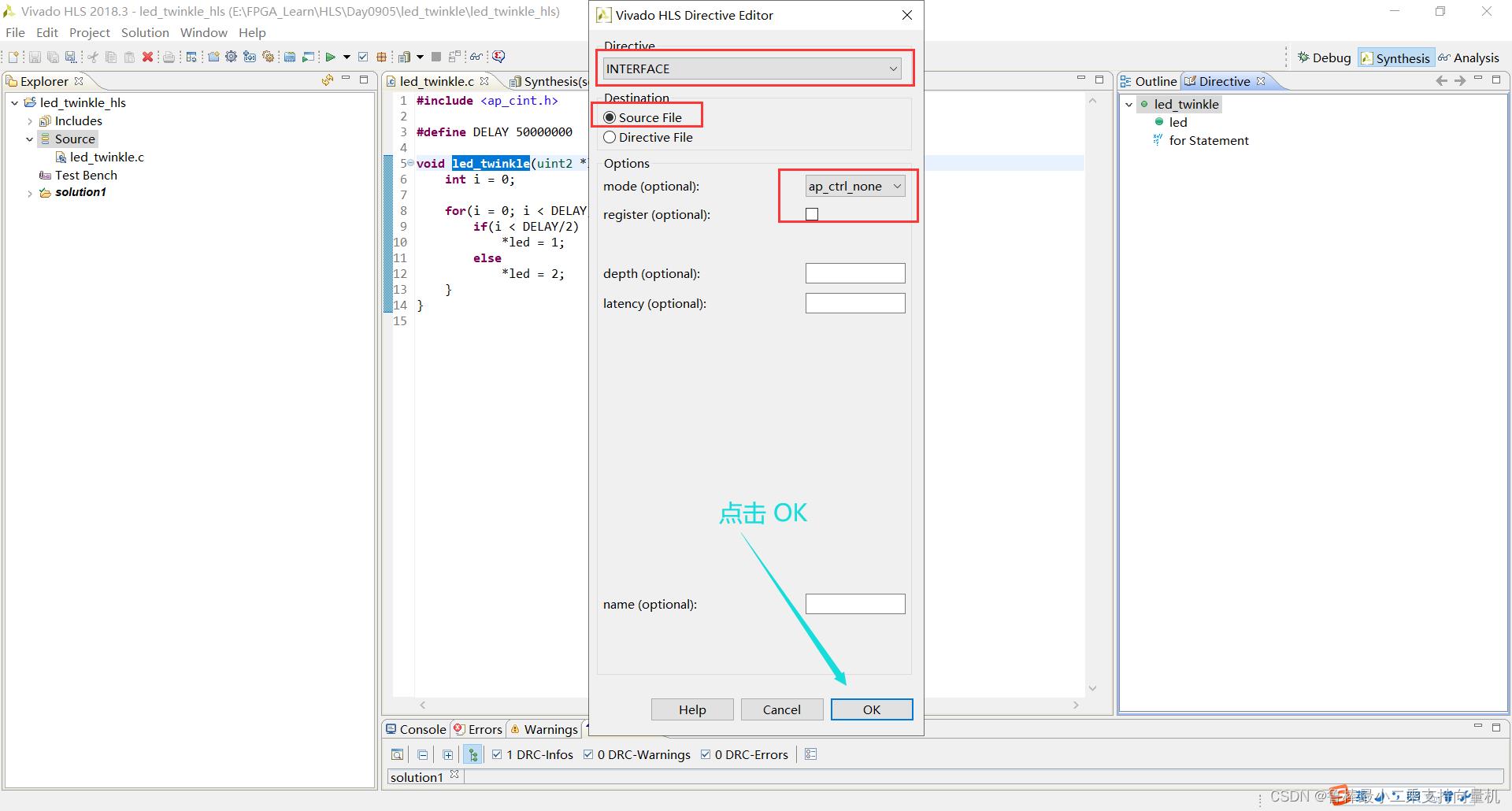

弹出界面,作如下配置:

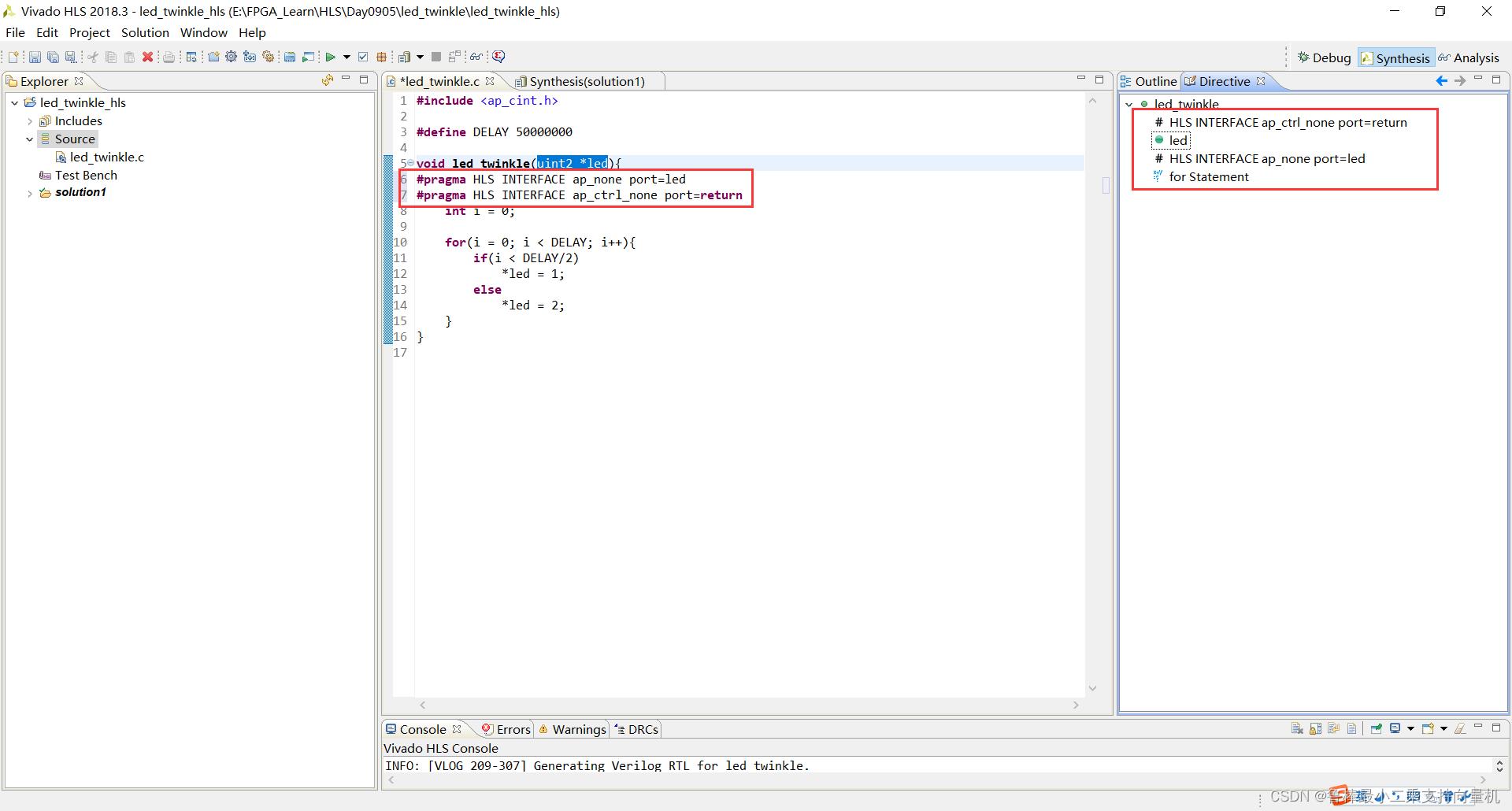

然后,源代码多出语句如下:

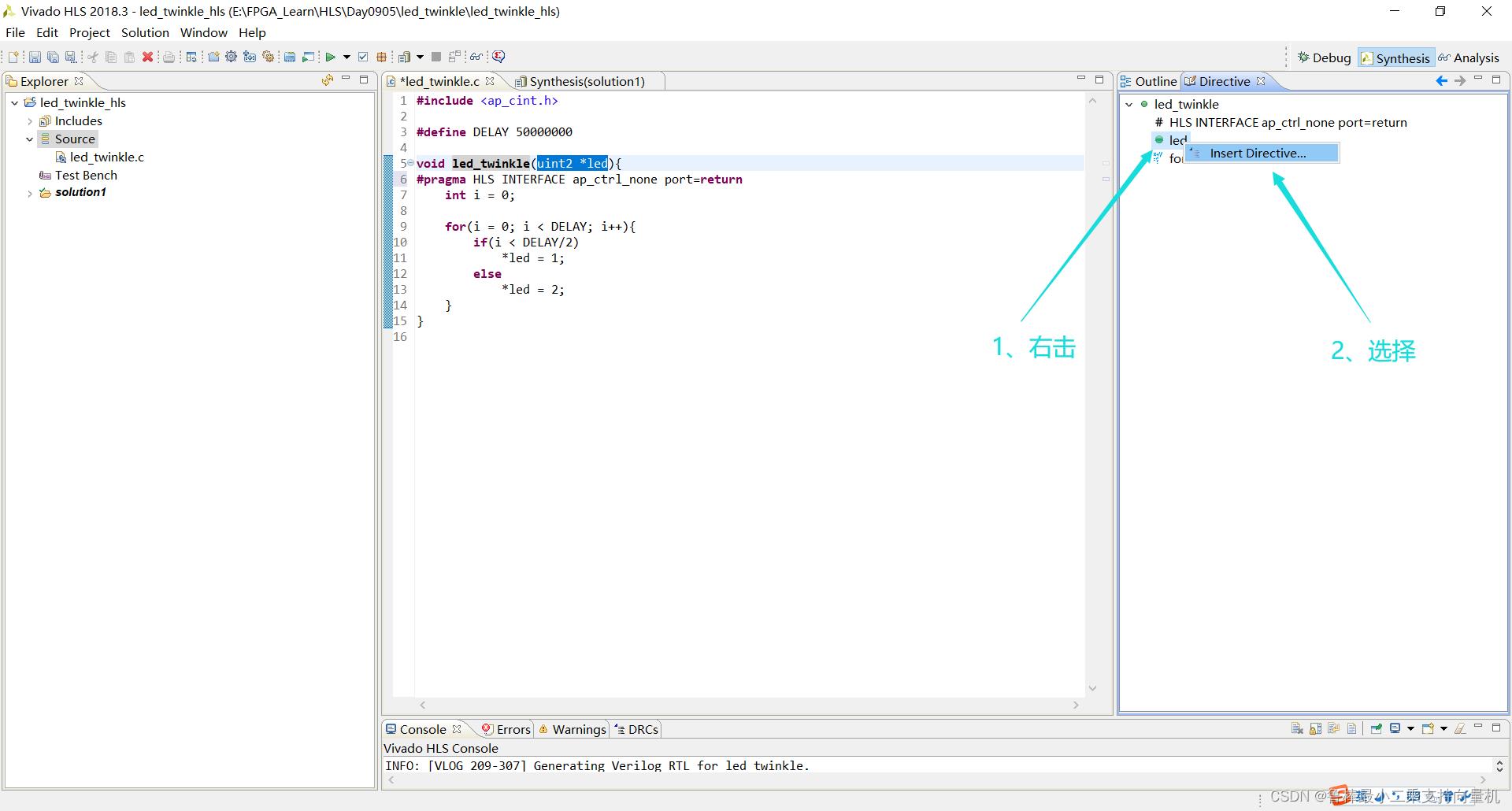

Directive 标签页,右击 led ,然后选择Insert Directive,如图所示:

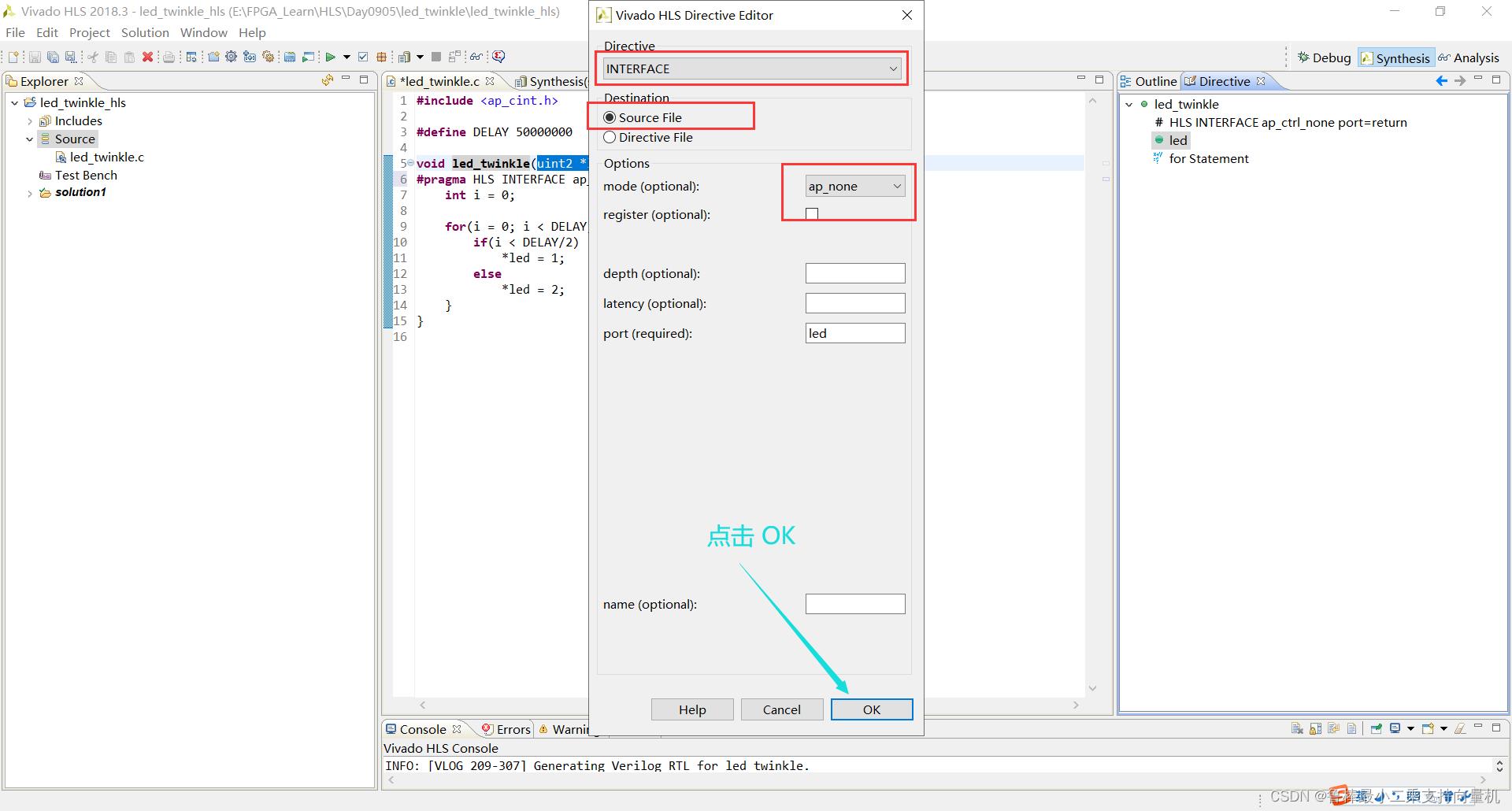

进行如下配置:

源码如下:

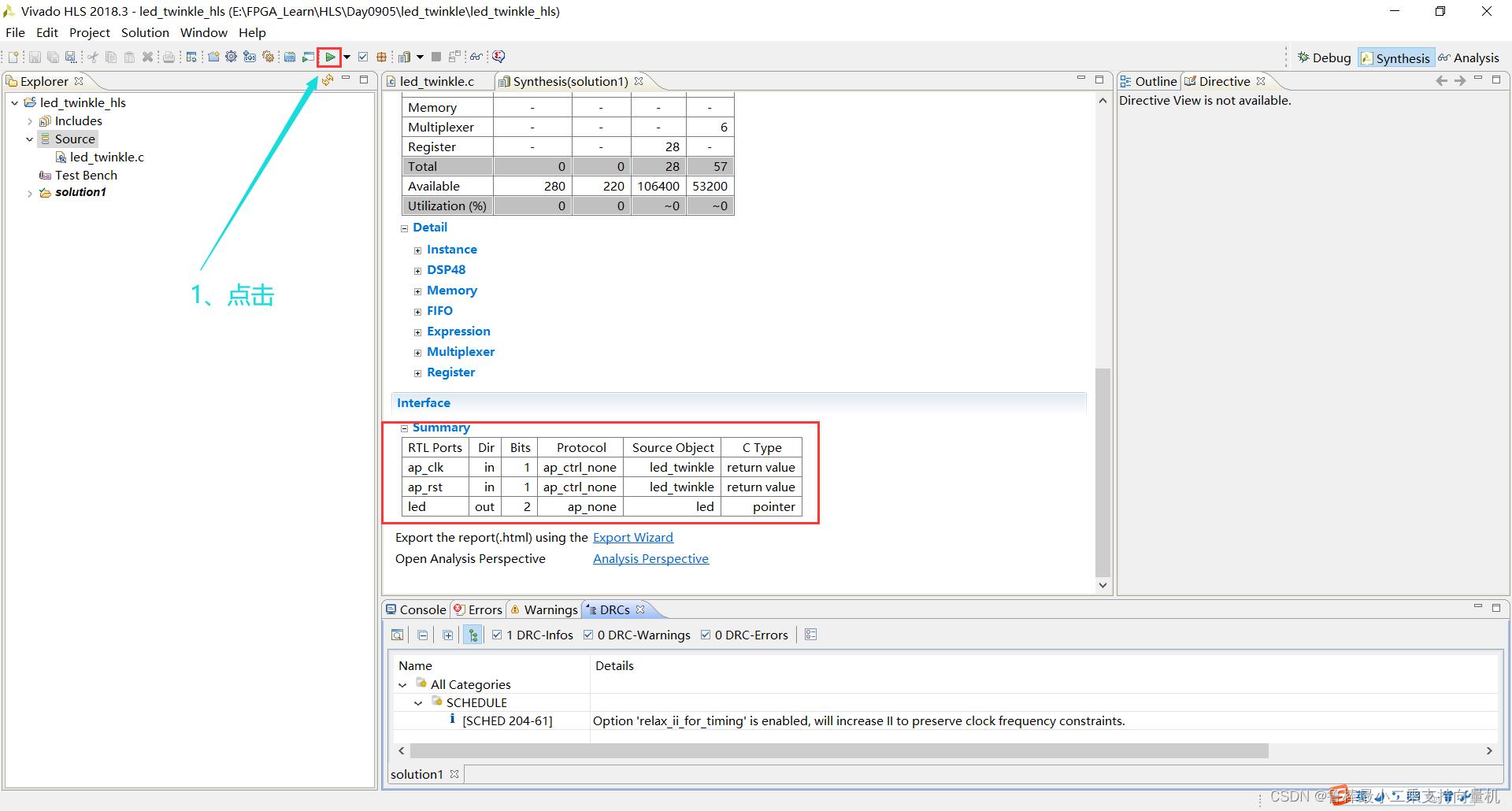

再次进行综合,综合报告如下:

进行如下操作,导出RTL:

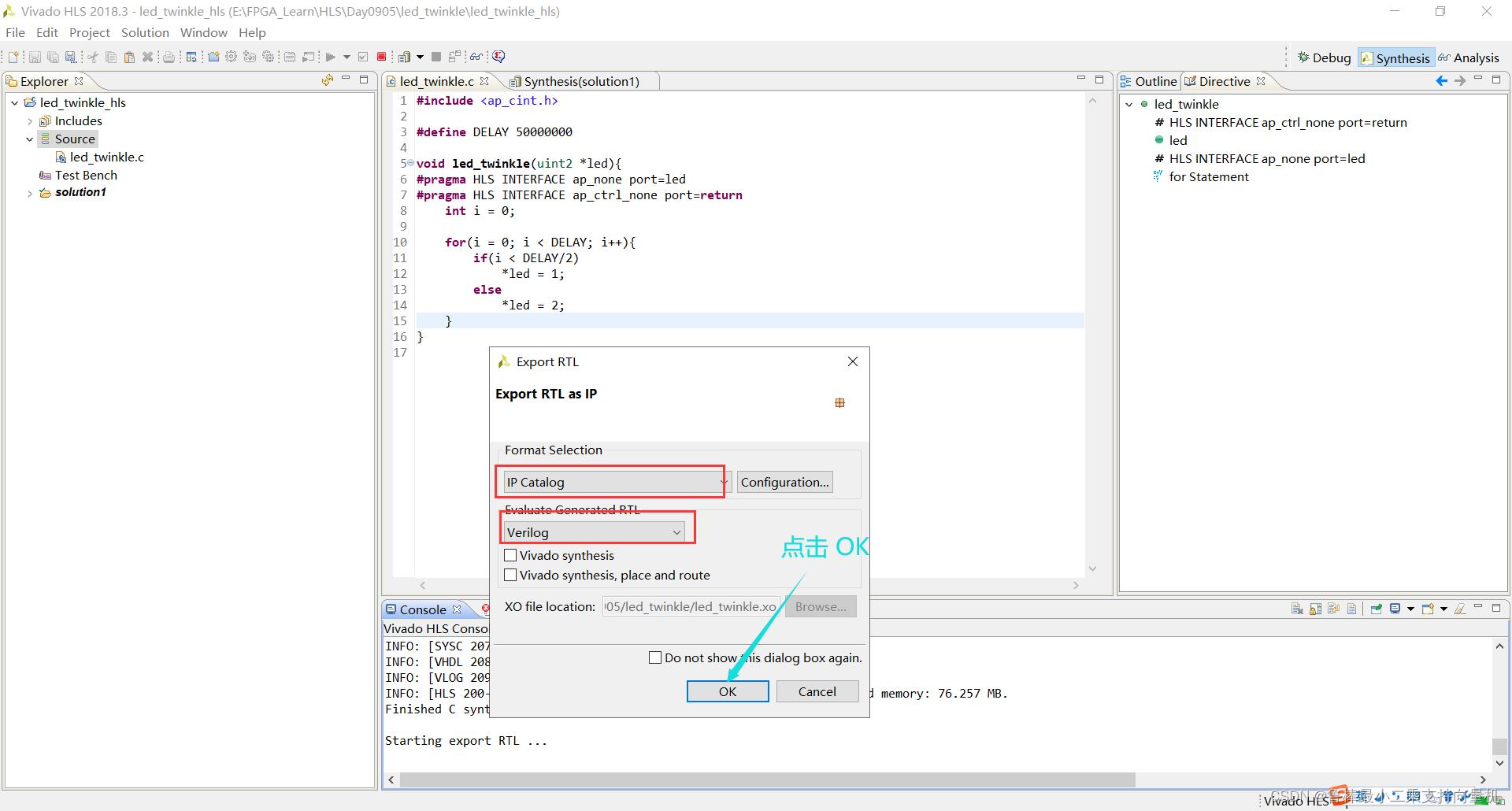

弹出如下窗口,点击OK:

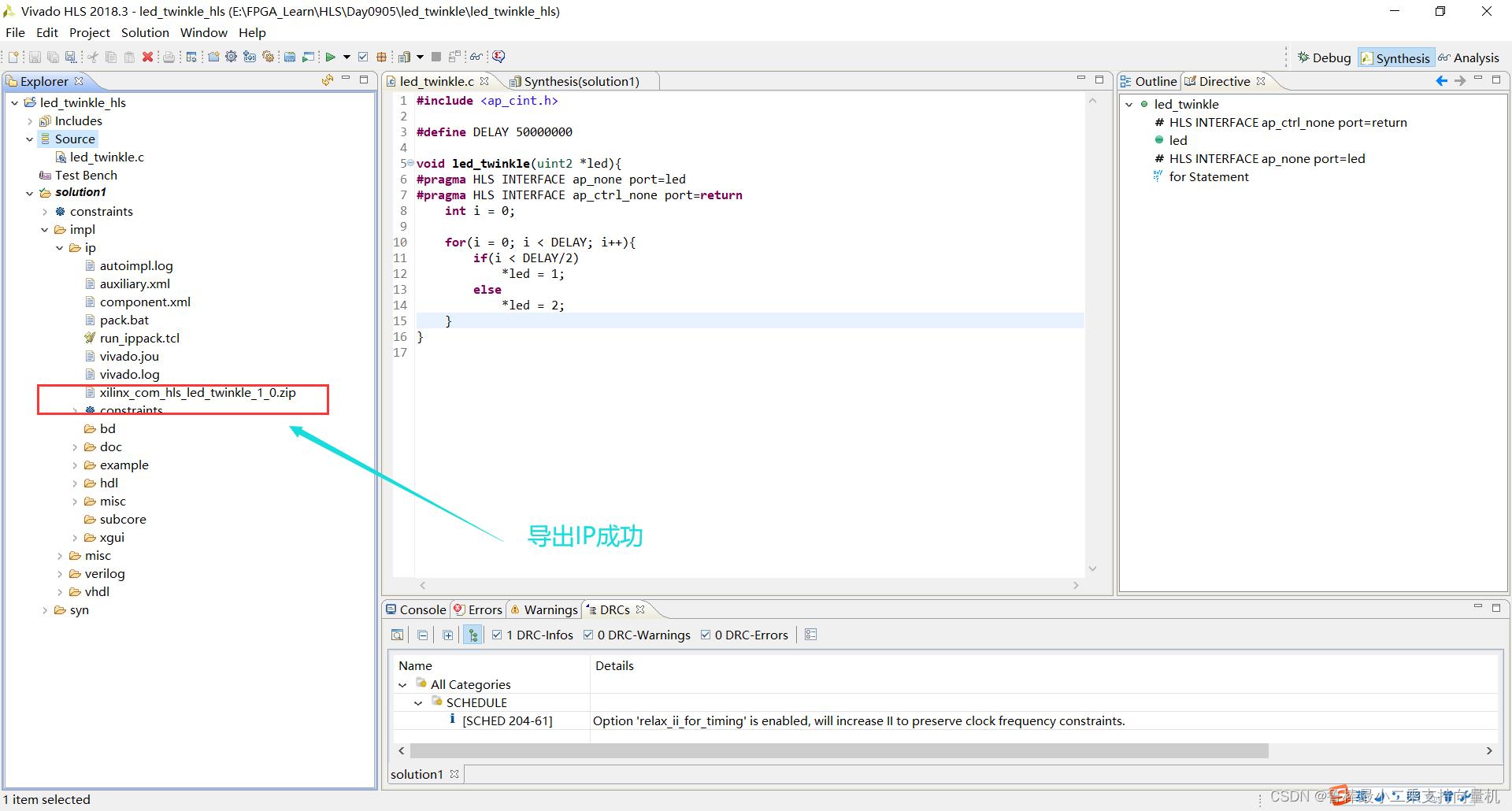

IP核如图所示:

2.2 IP验证

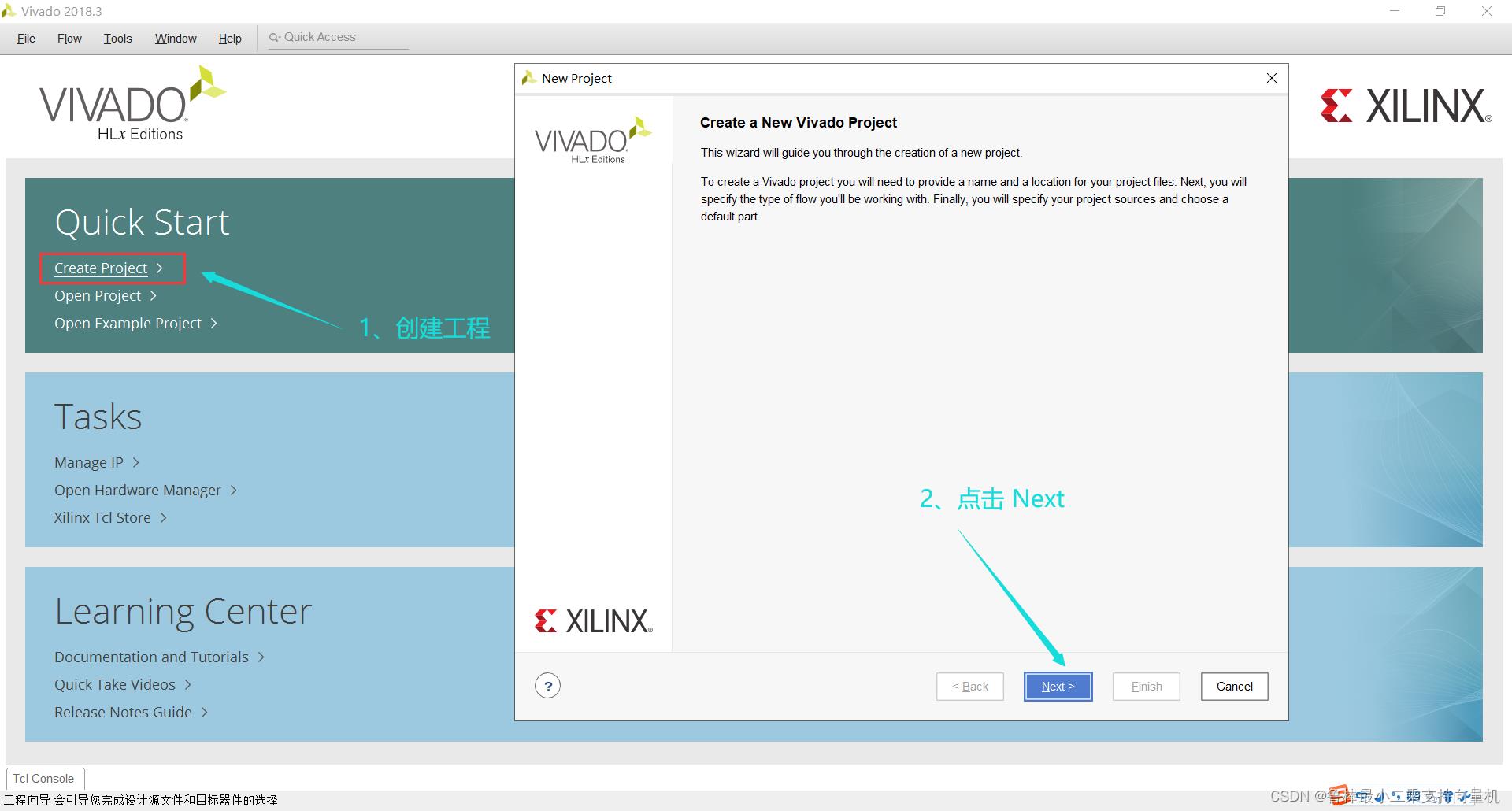

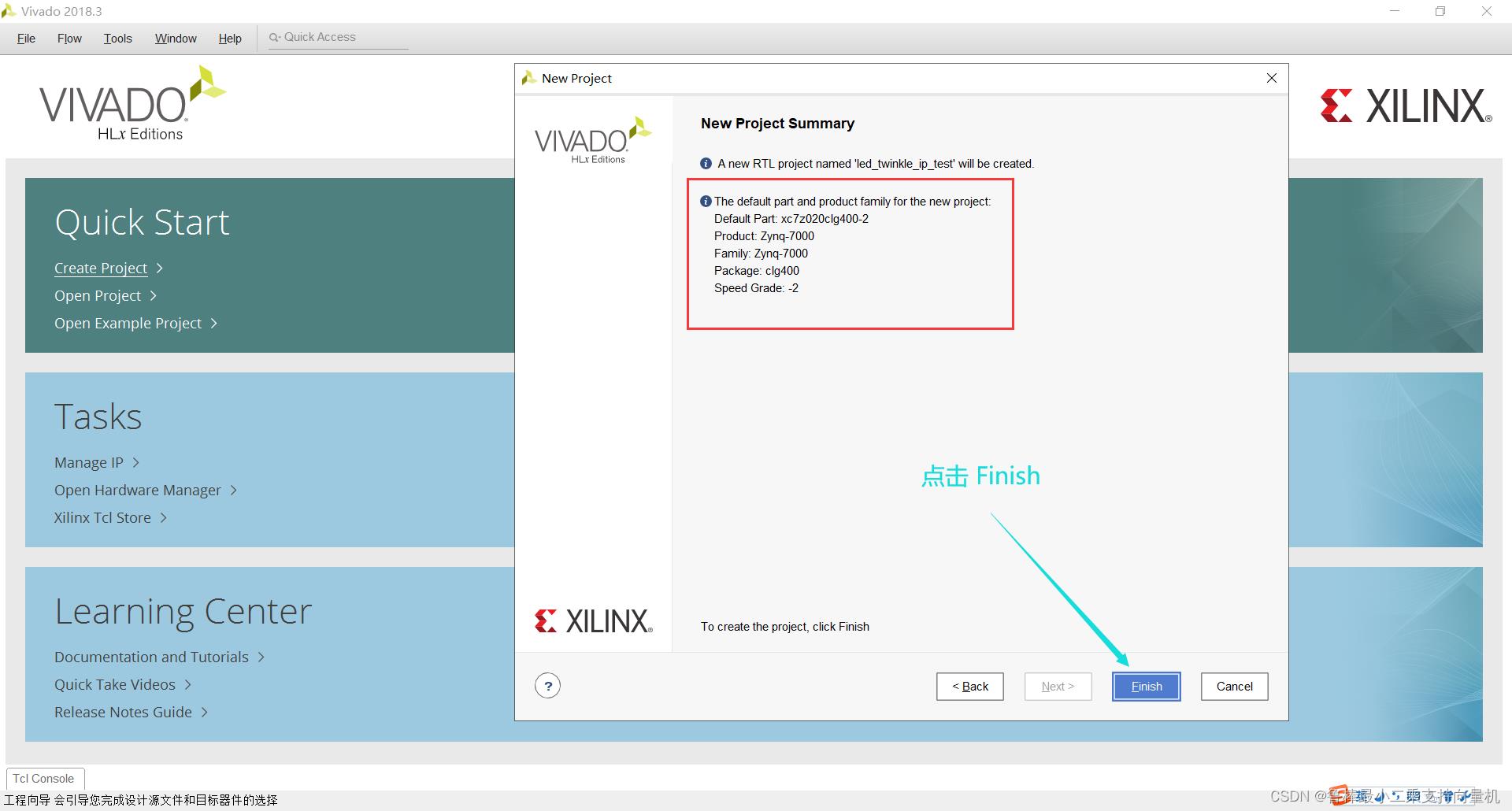

创建工程,如图所示:

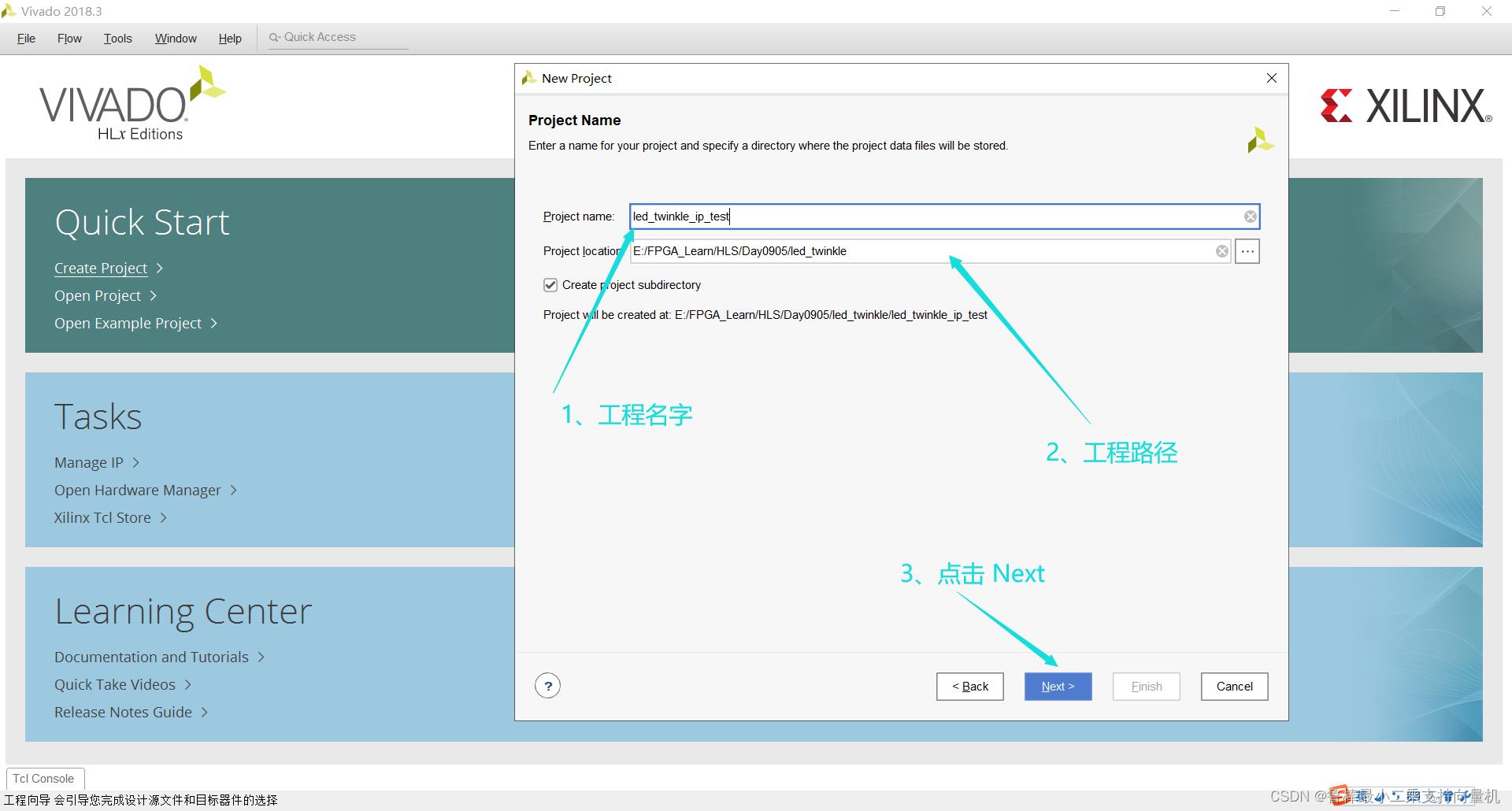

输入工程名和工程路径,该路径与HLS工程路径保持一致:

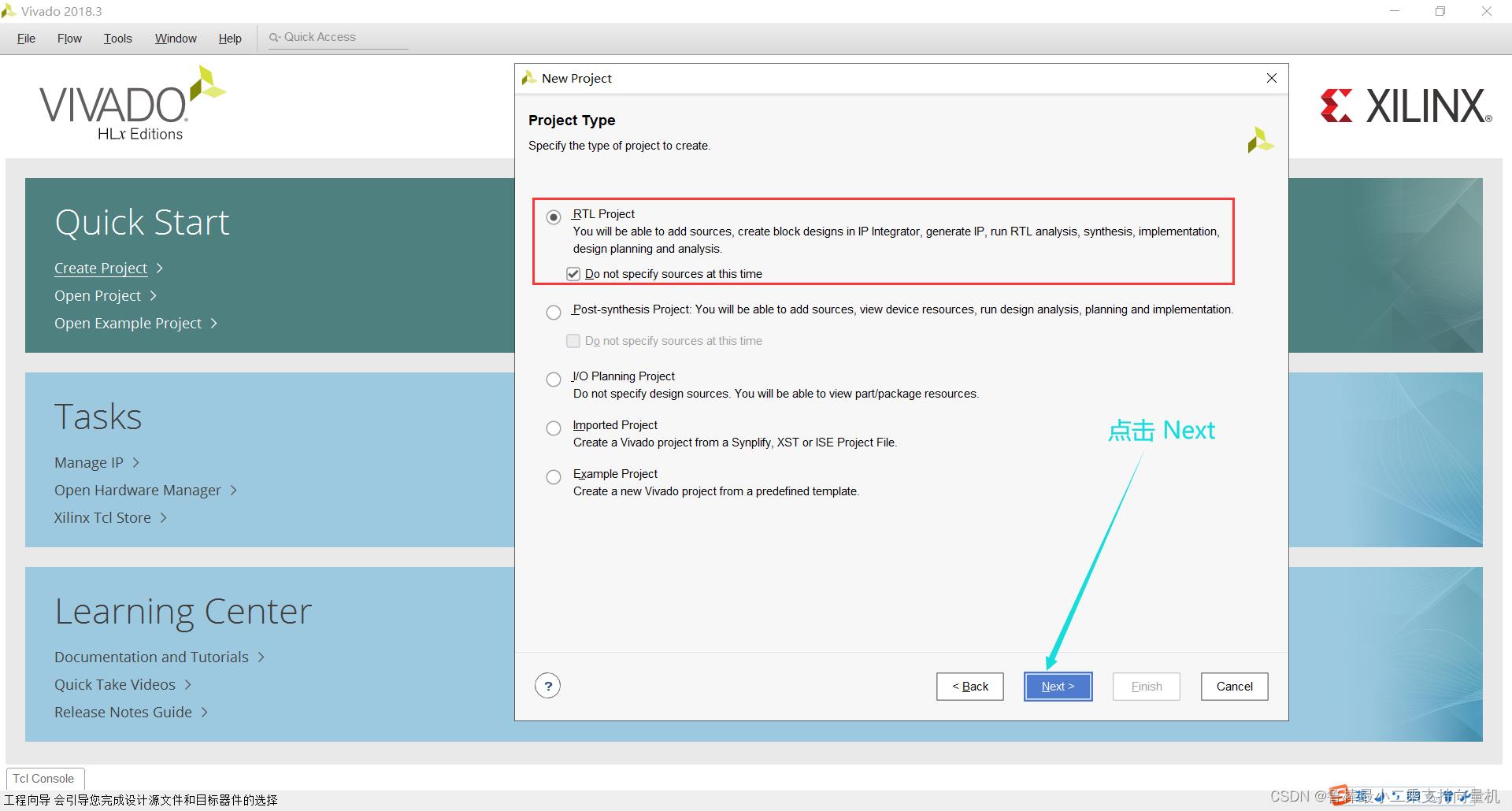

按如下操作:

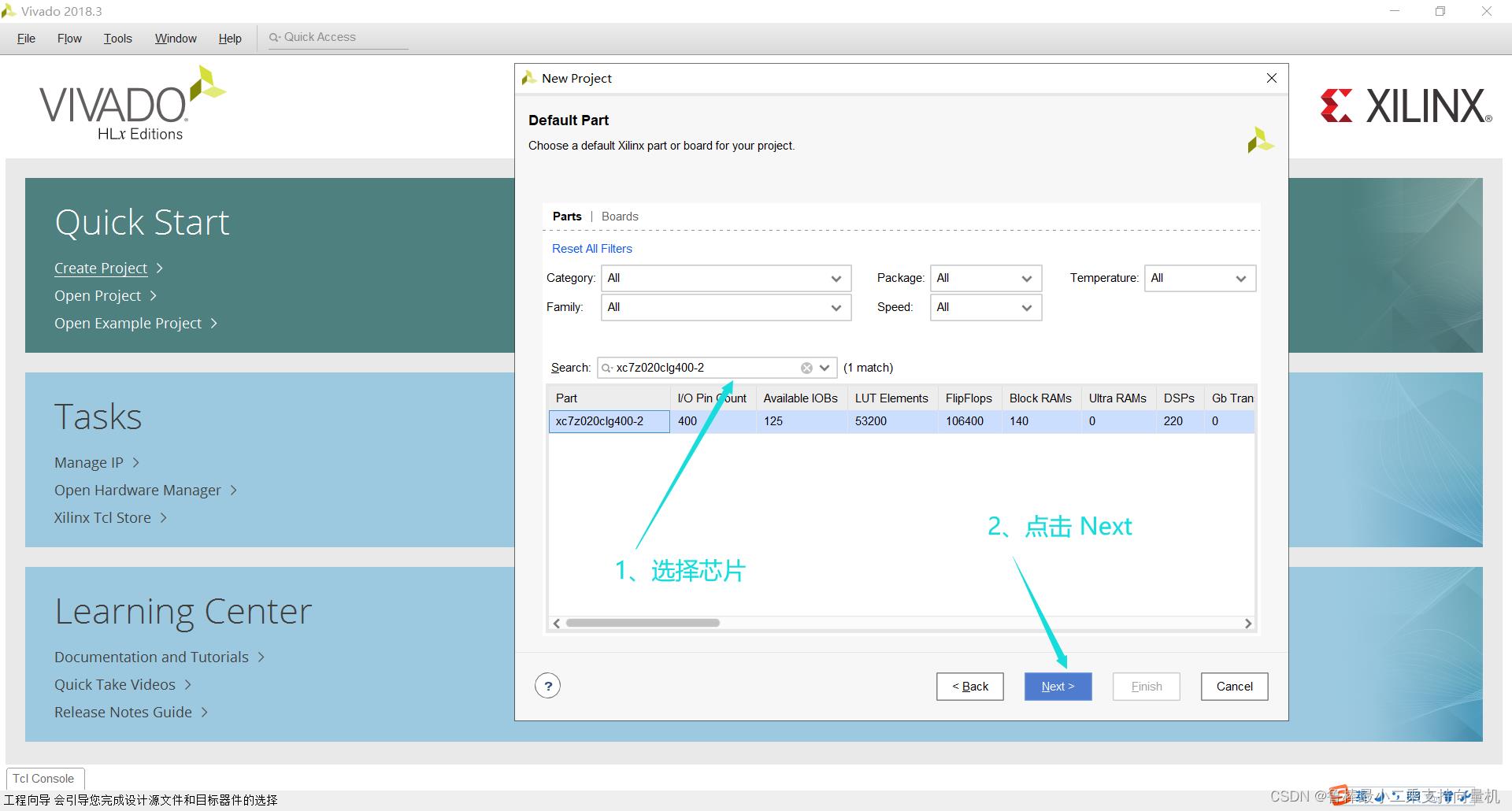

选择芯片型号:

工程创建完成:

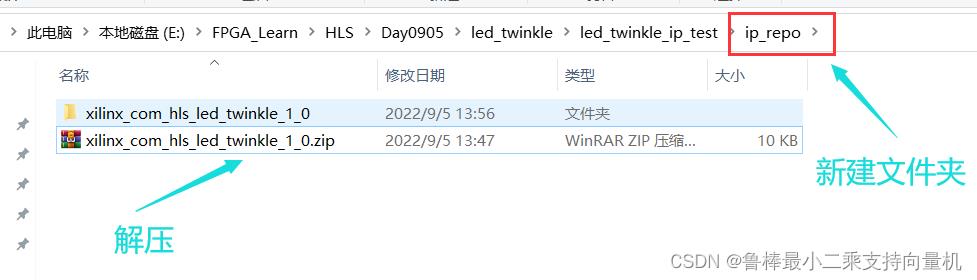

将 HLS 设计过程中导出的 IP 核拷贝到 Vivado 工程目录下,在 Vivado 工

程目录下新建一个名为ip_repo的文件夹,然后拷贝并解压IP核压缩包:

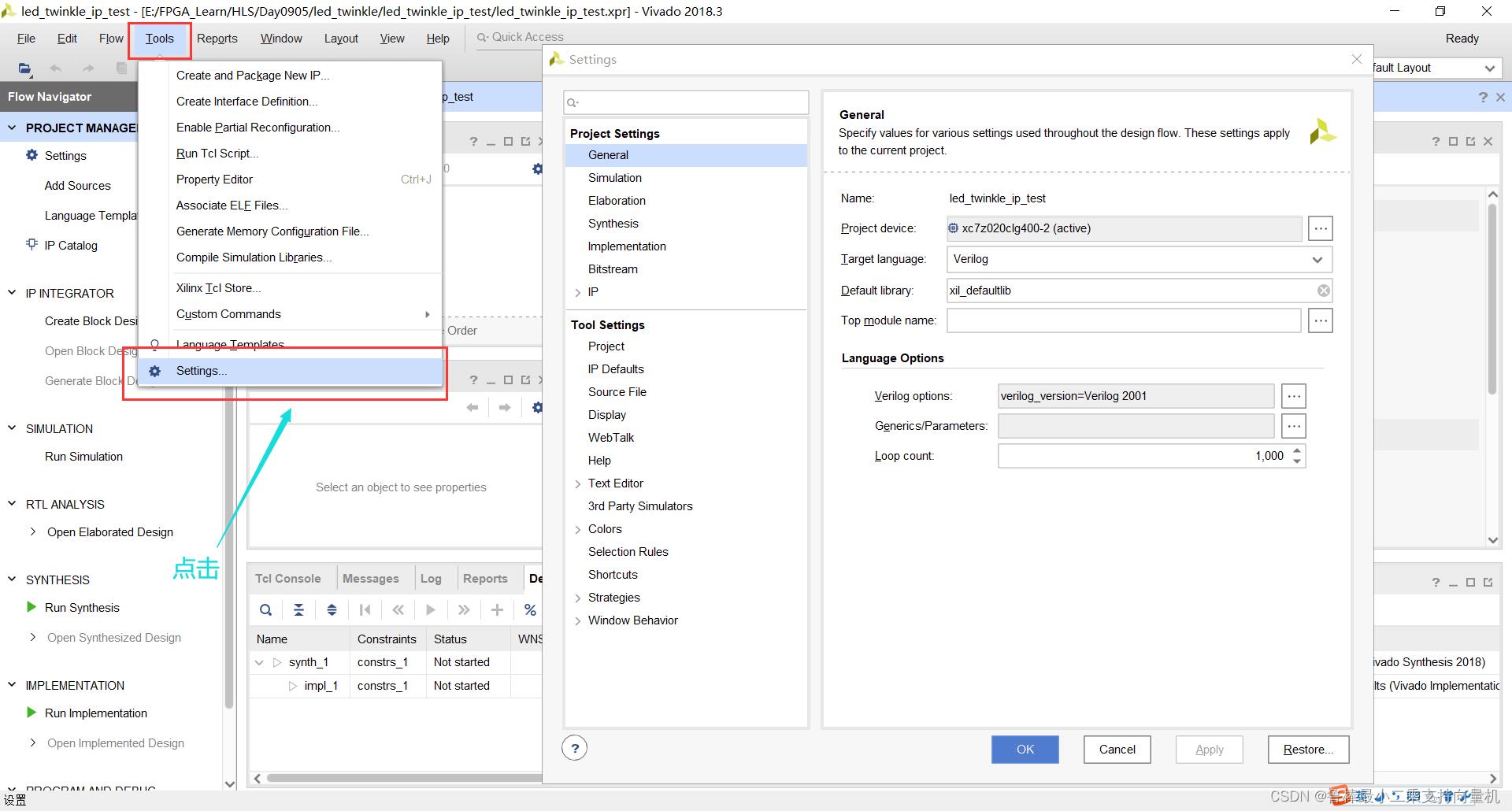

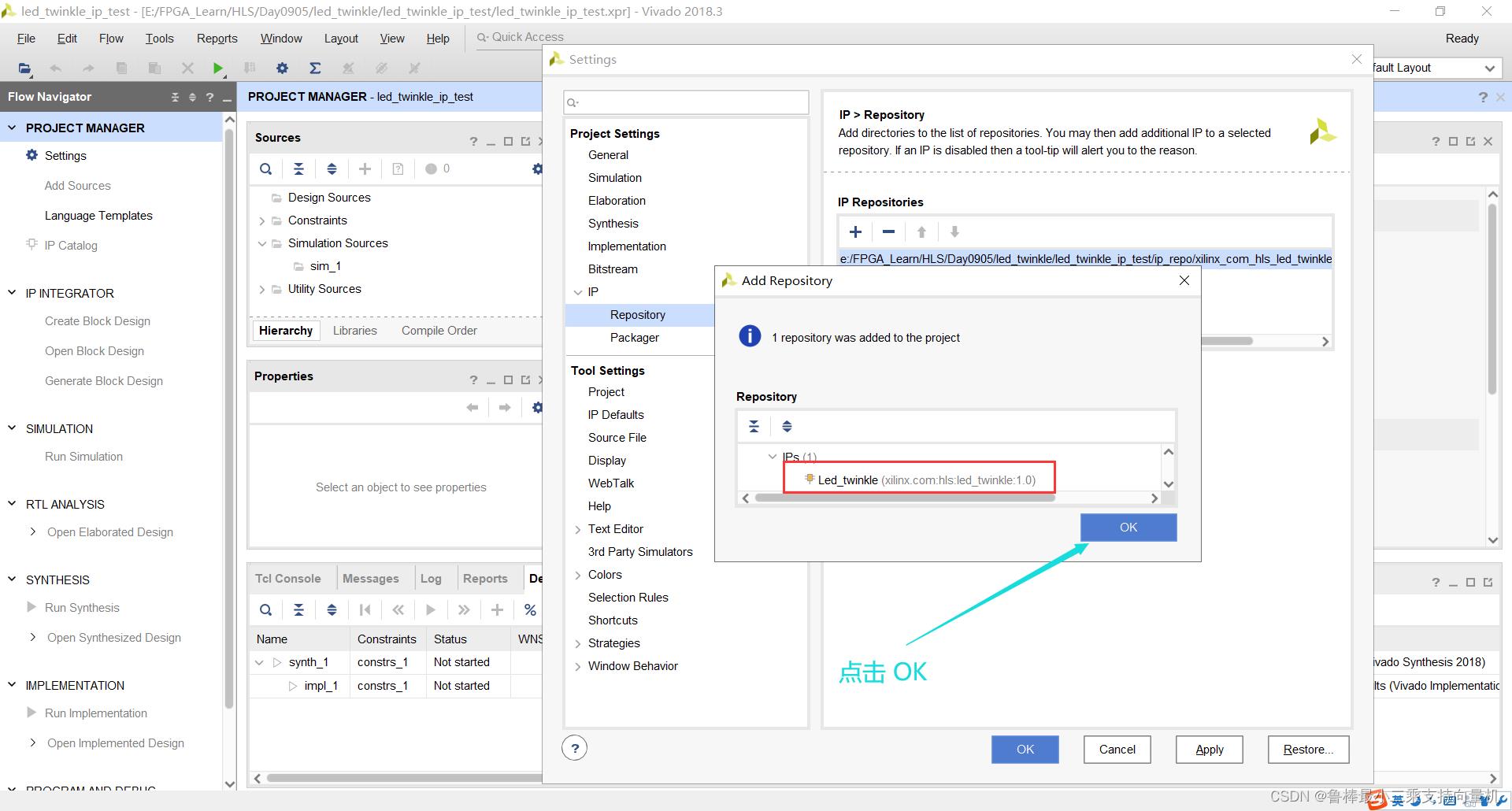

将IP添加到工程的IP库,按如下操作:

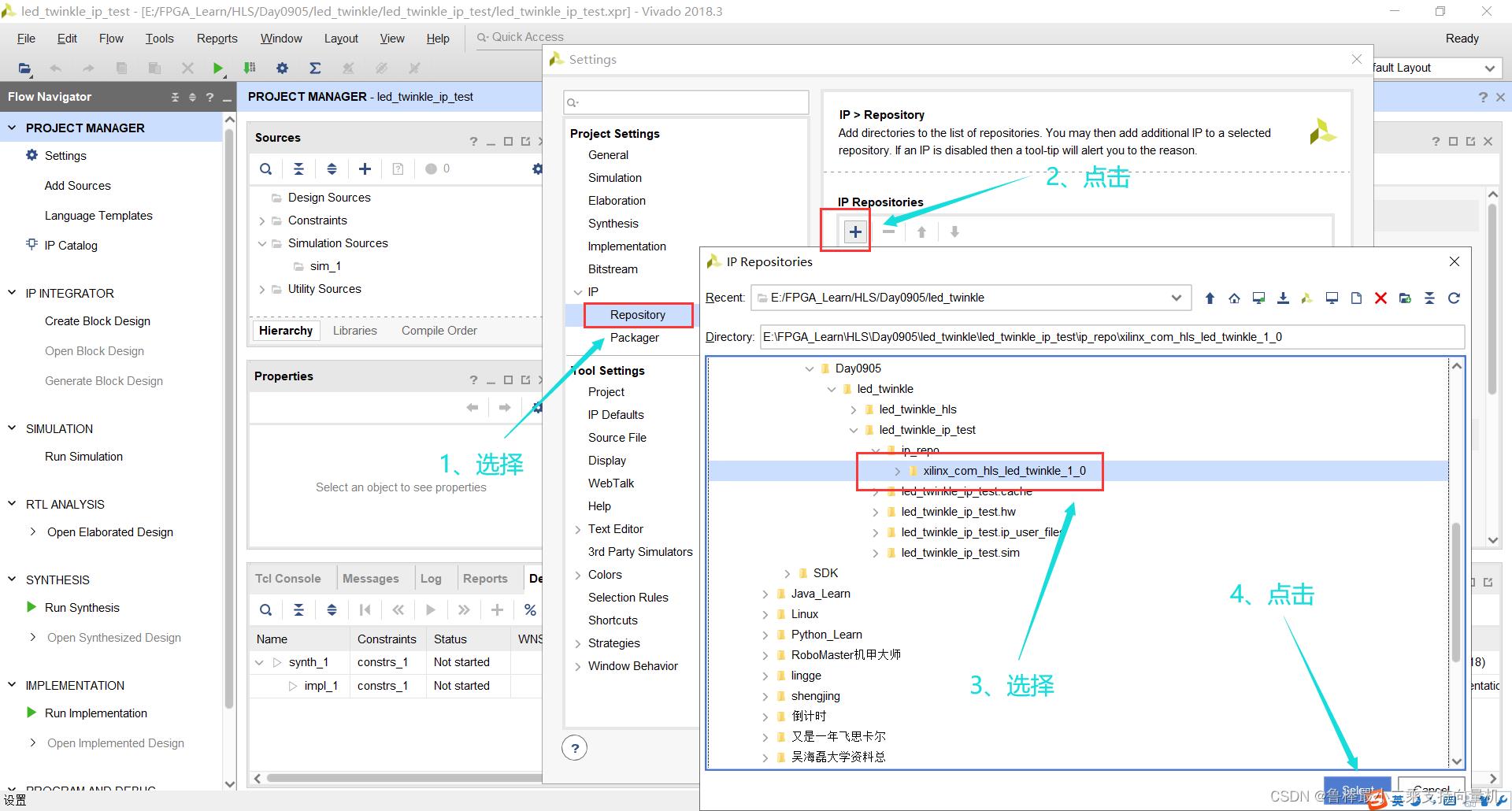

点击IP中的Repository,然后点击+,添加IP核,如图所示:

如图所示,点击OK:

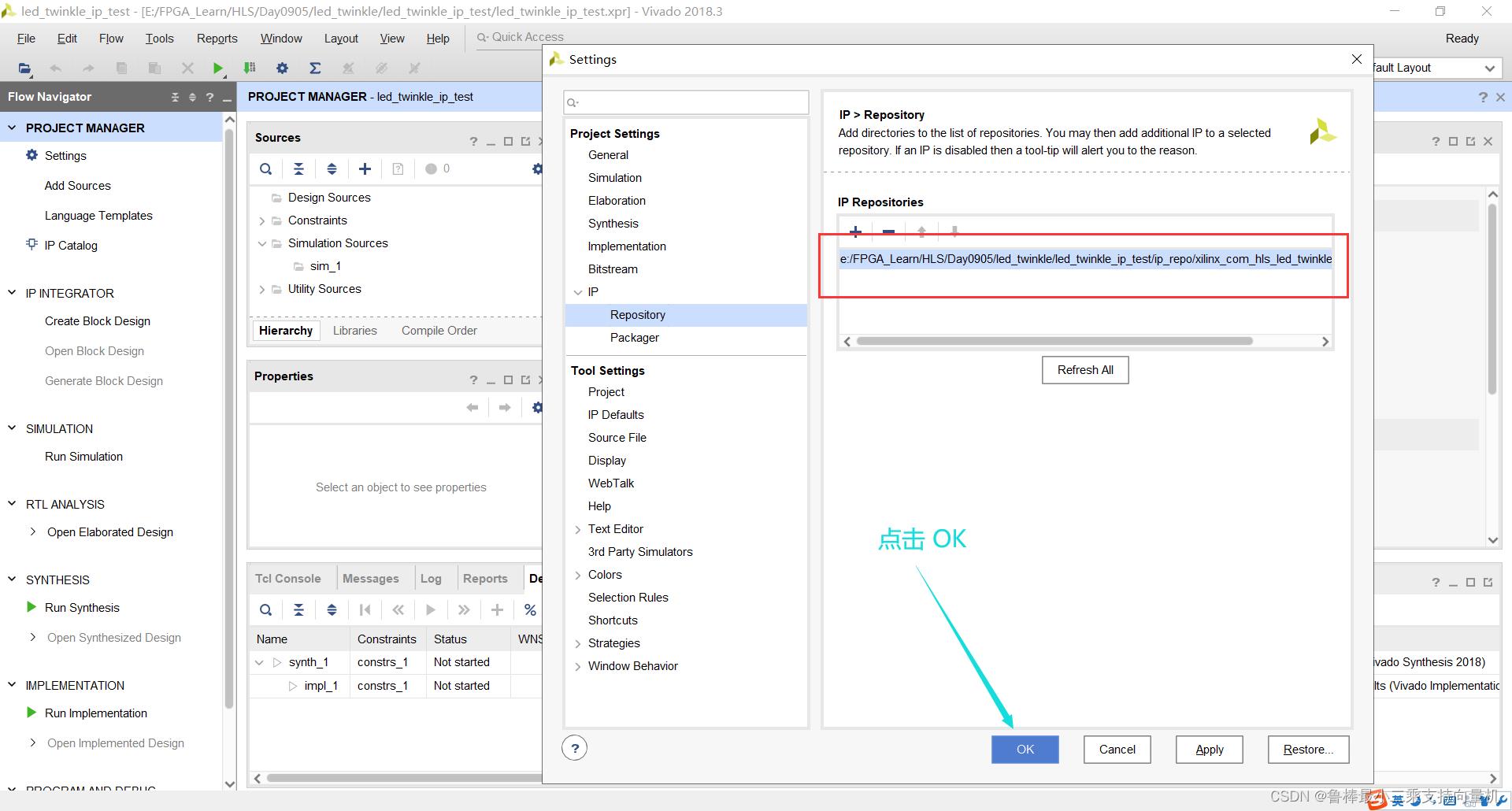

点击OK,完成IP核添加:

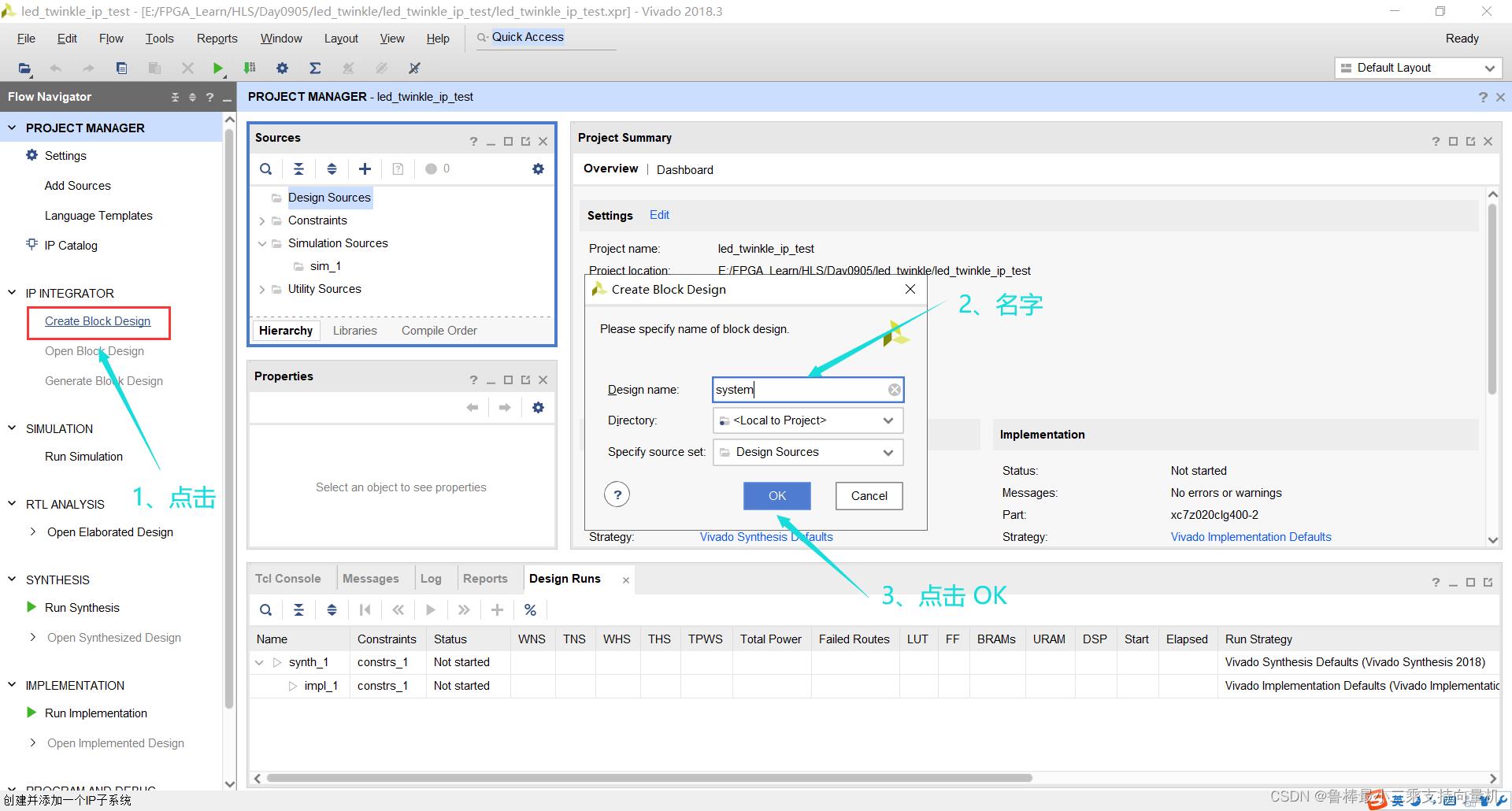

创建Block Design,名字为system,如图所示:

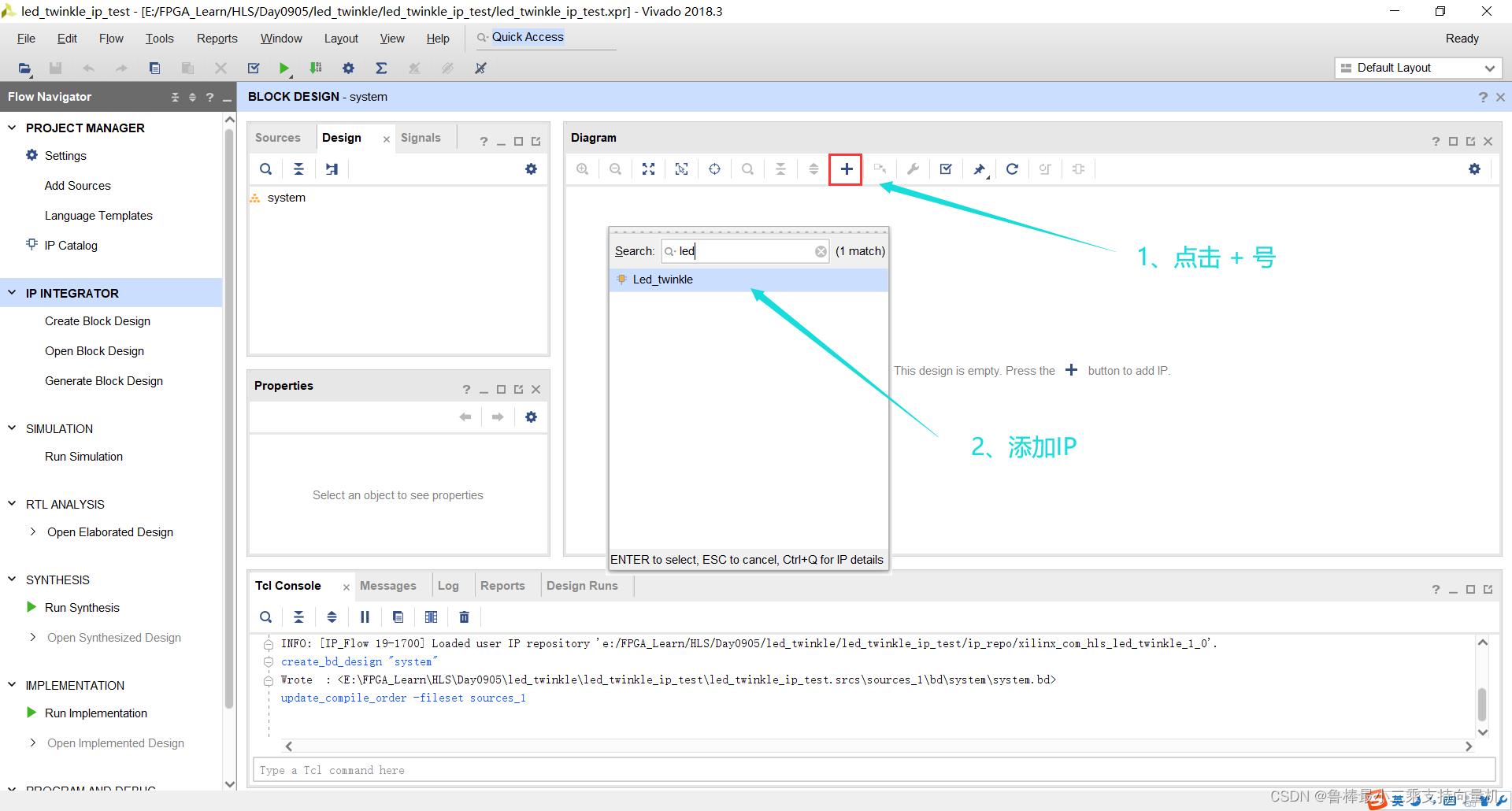

如图操作,添加IP:

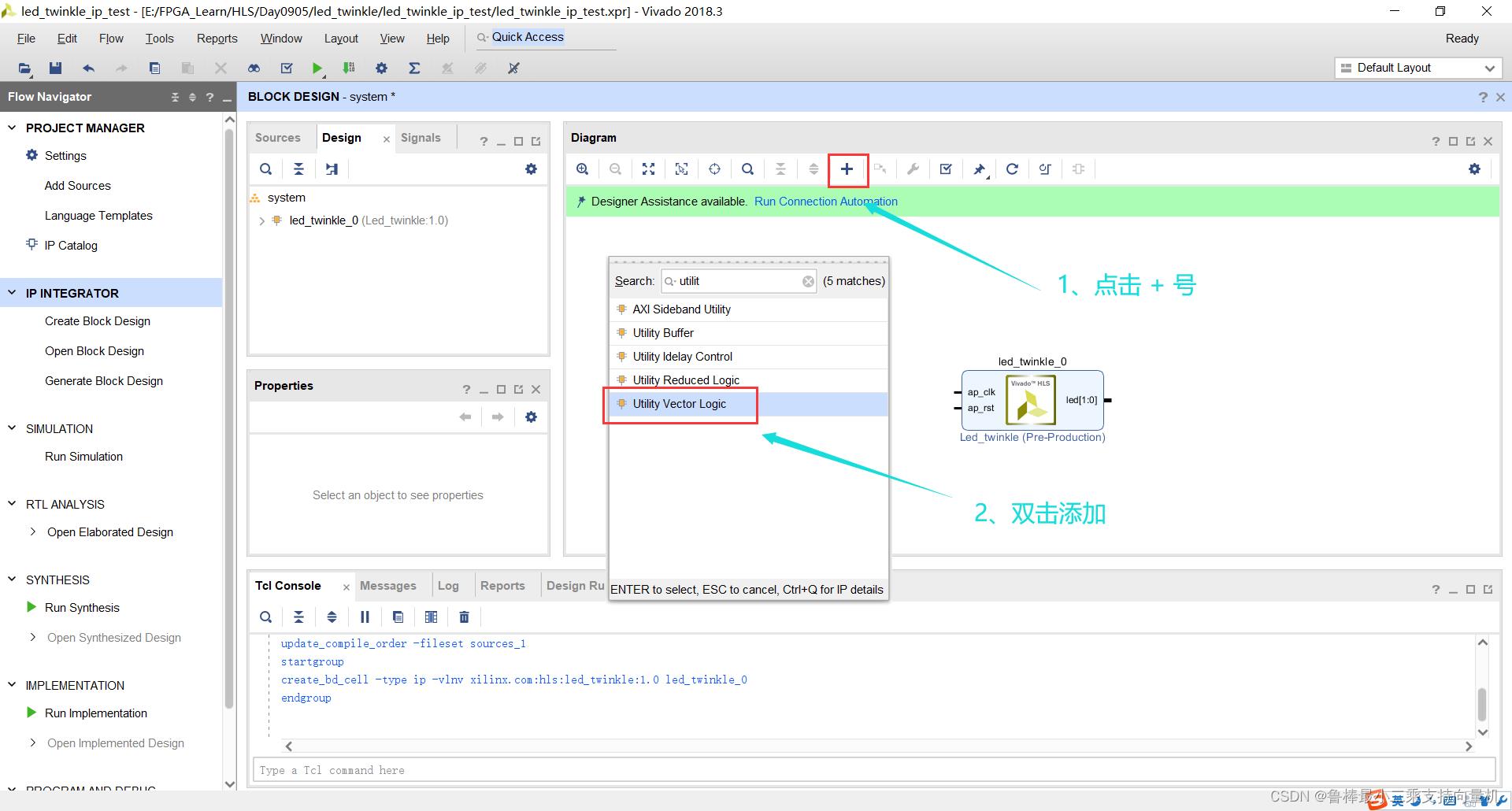

添加Utility Vector Logic IP核:

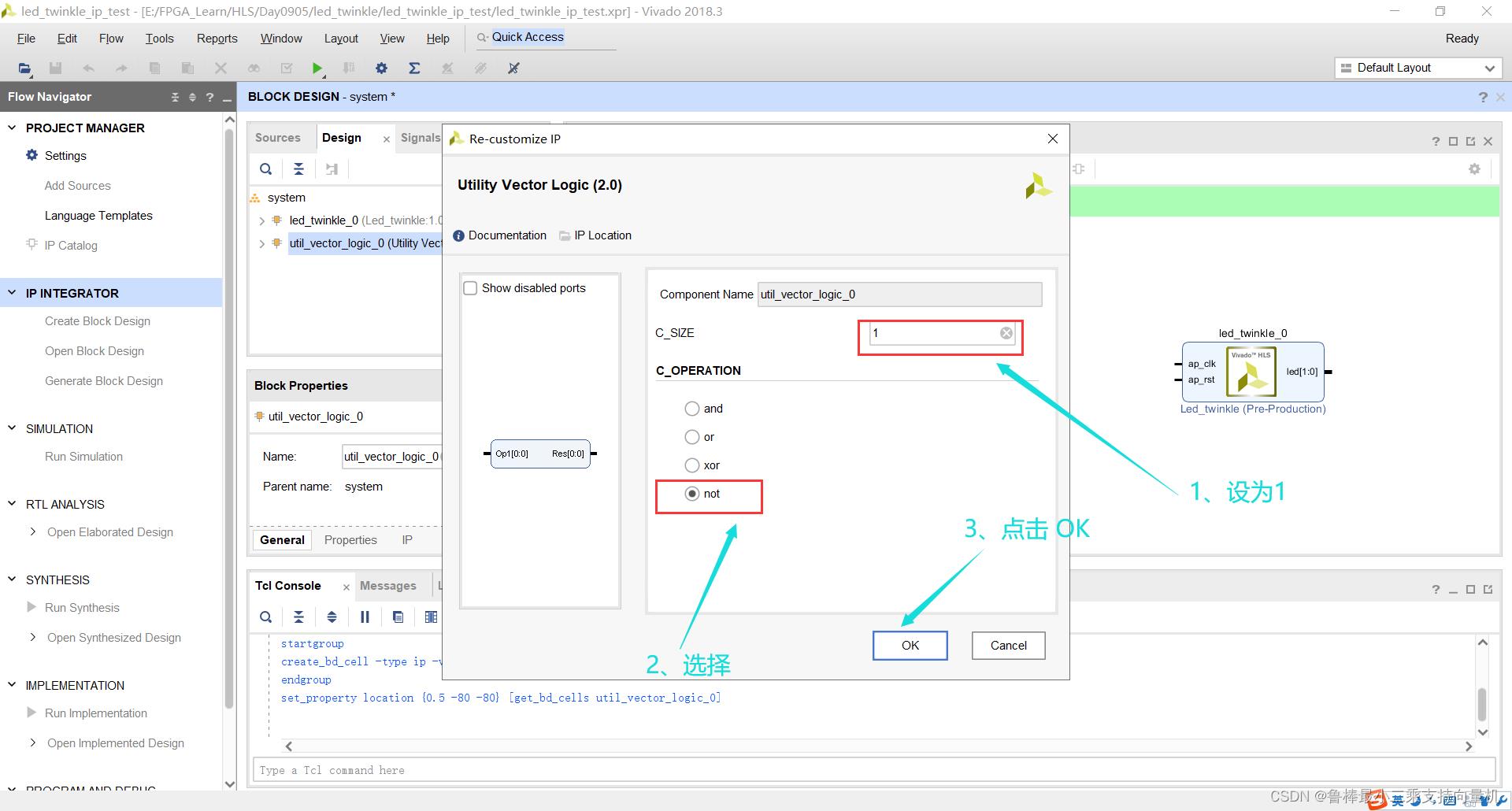

进行如下IP核配置:

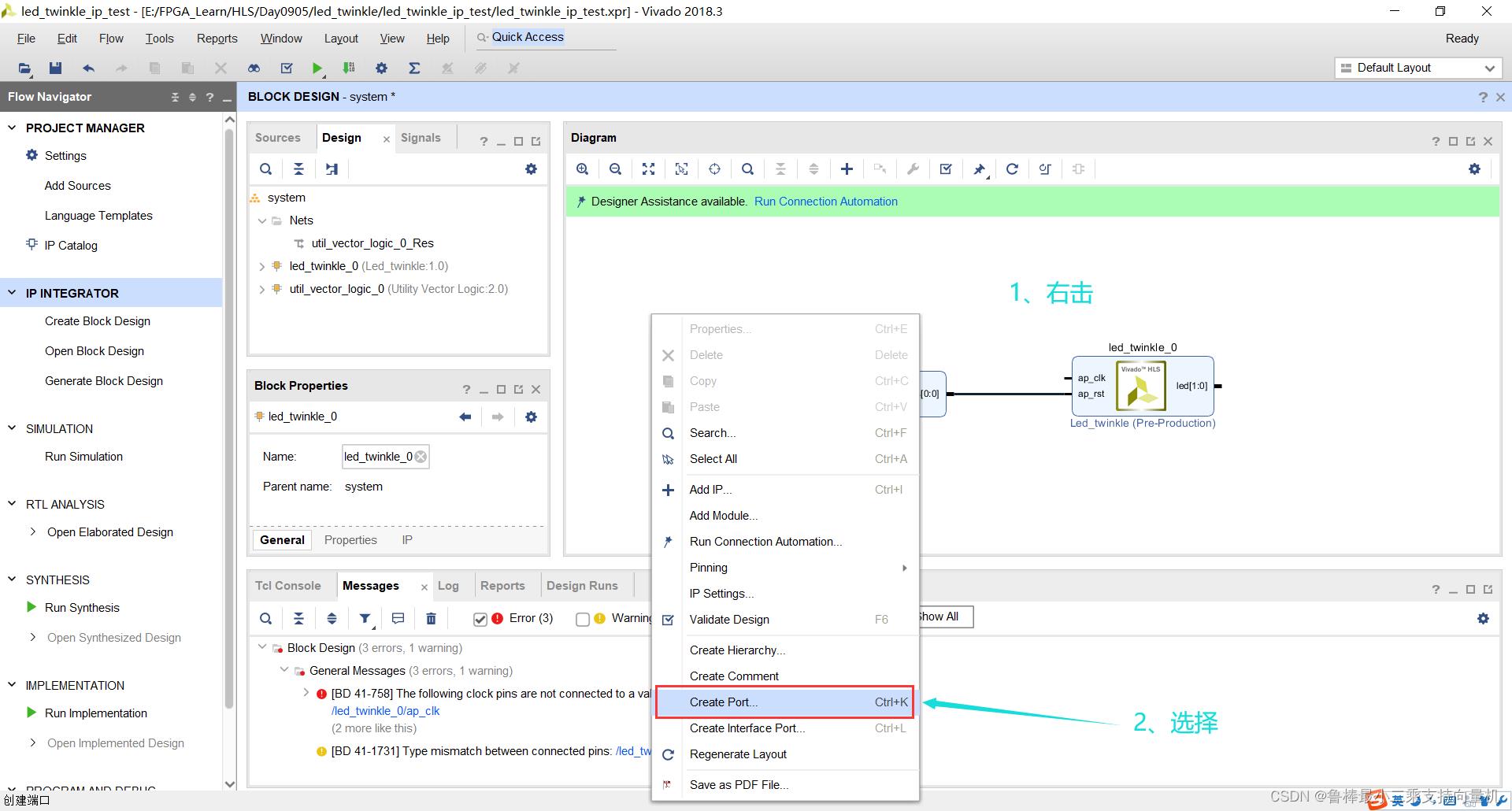

创建Port,如图所示:

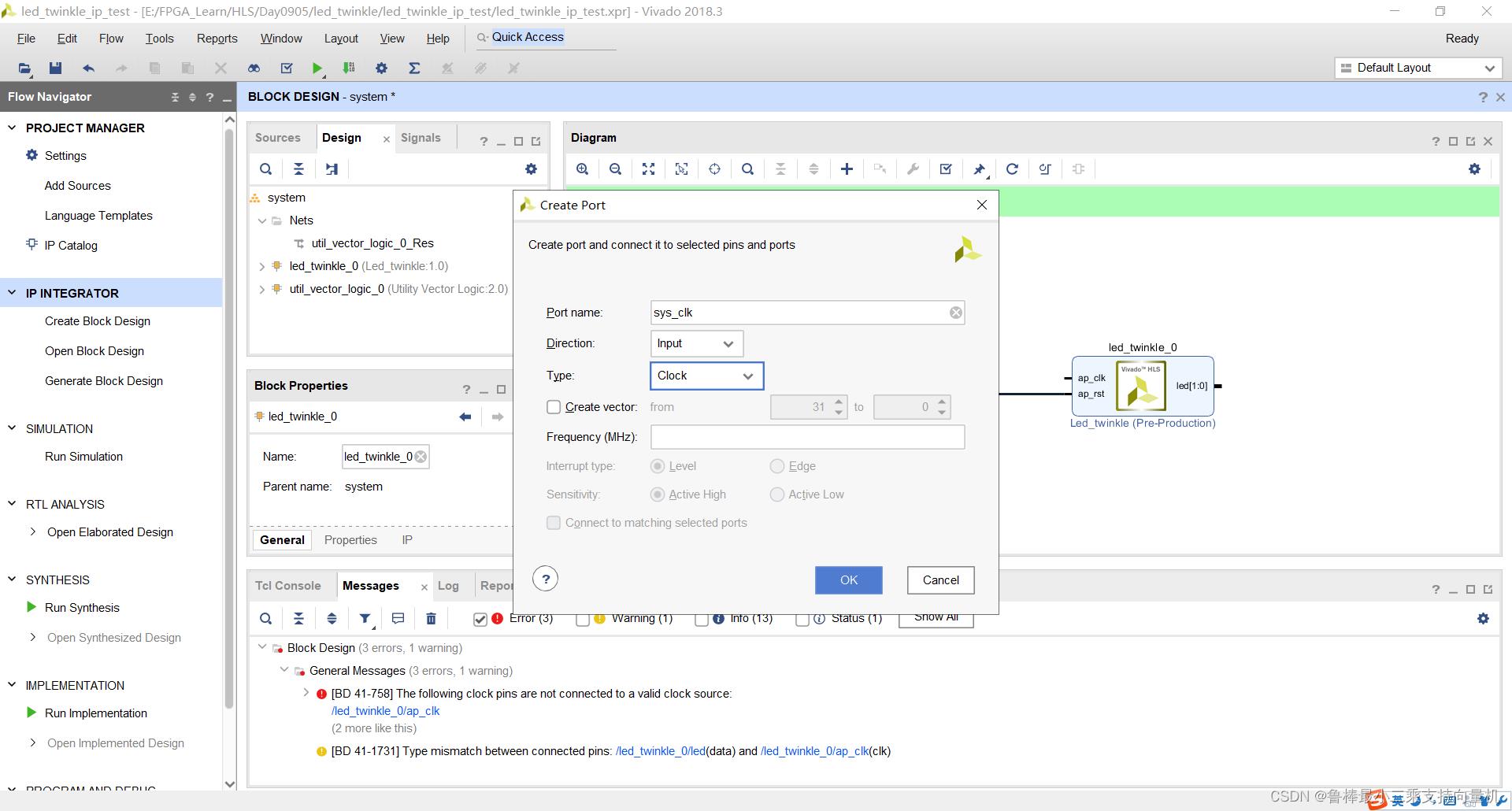

sys_clk Port类型选择Clock:

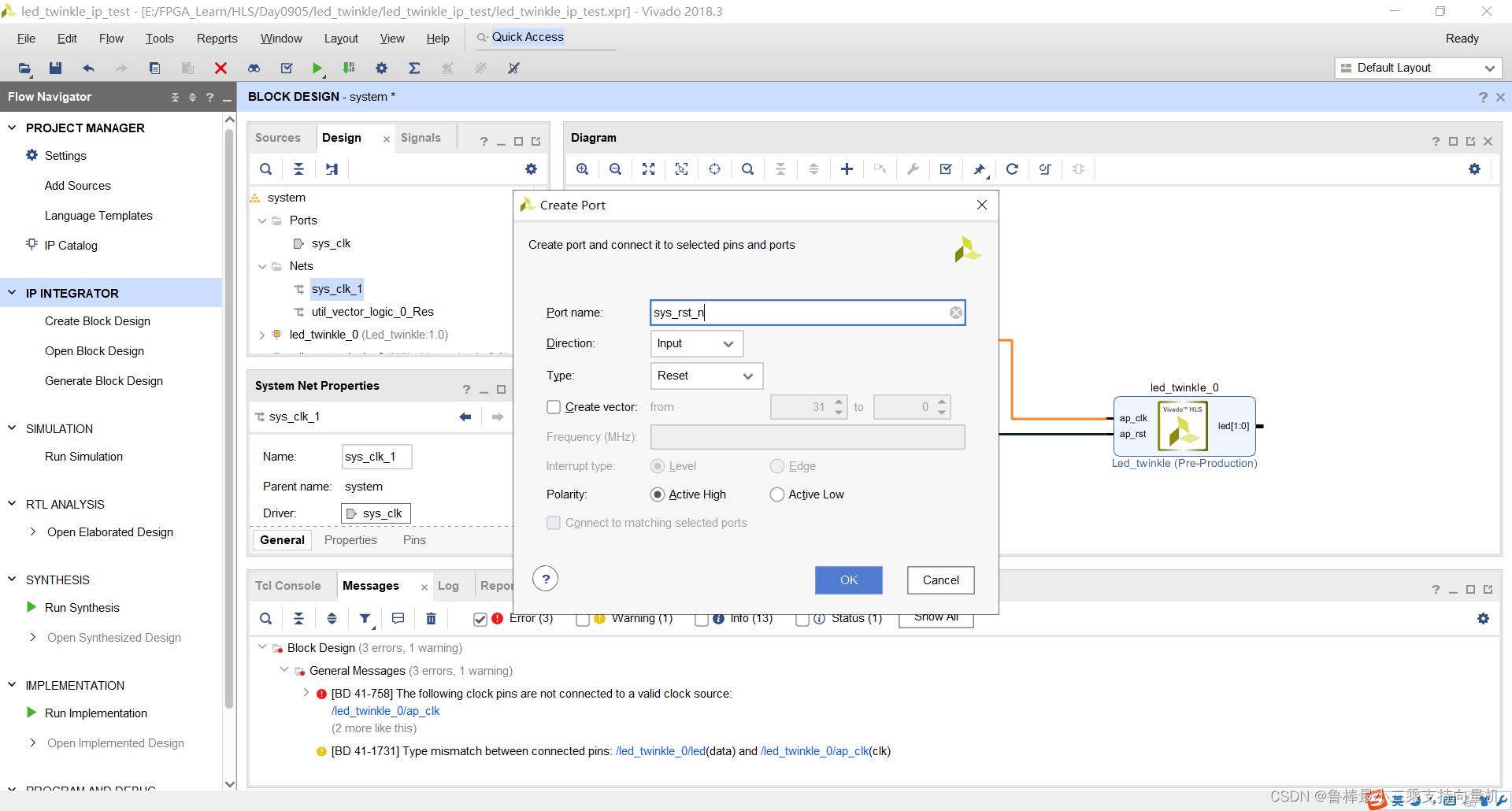

Reset类型的Port重命名为sys_rst_n:

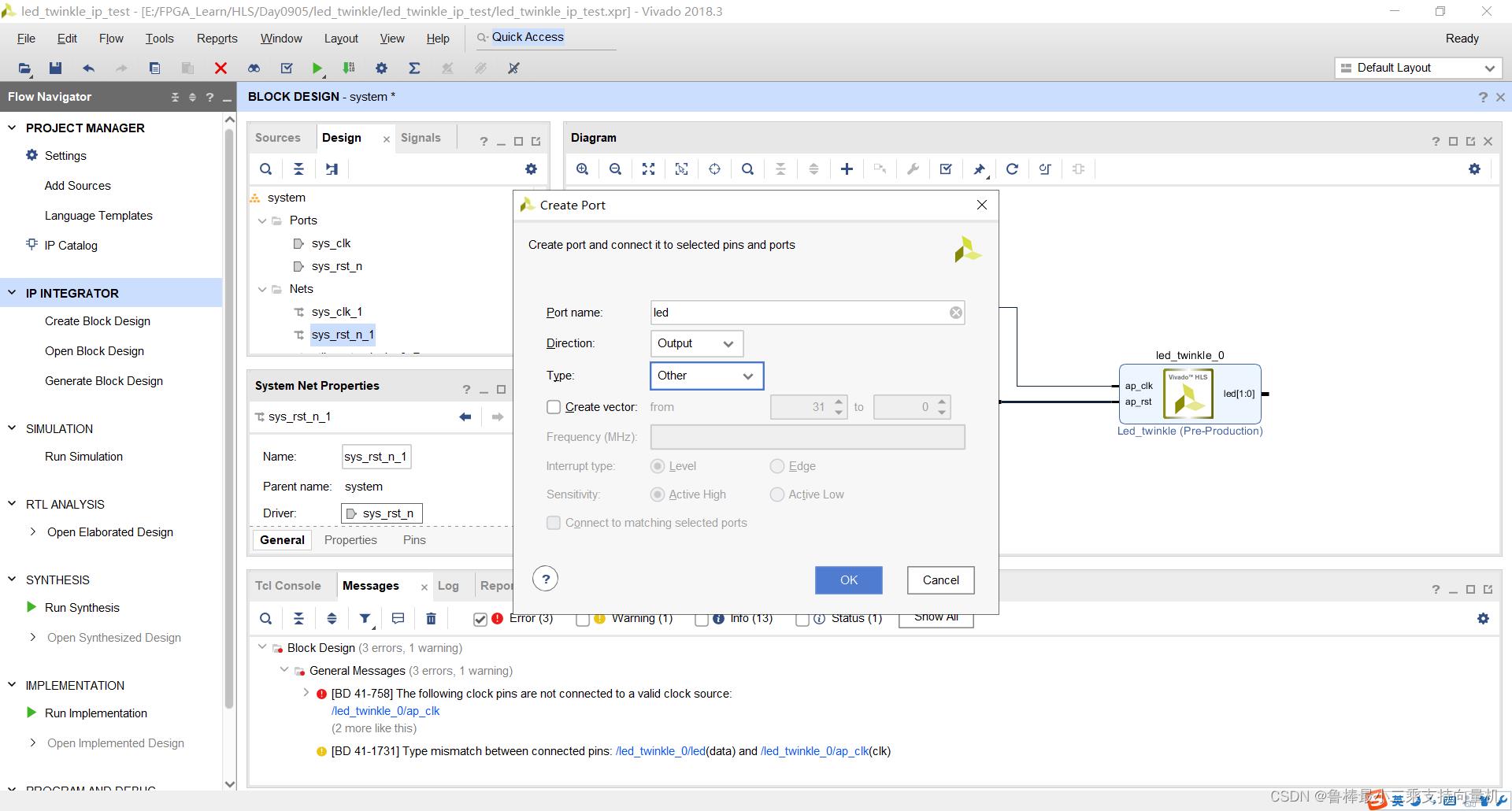

led设置为Other:

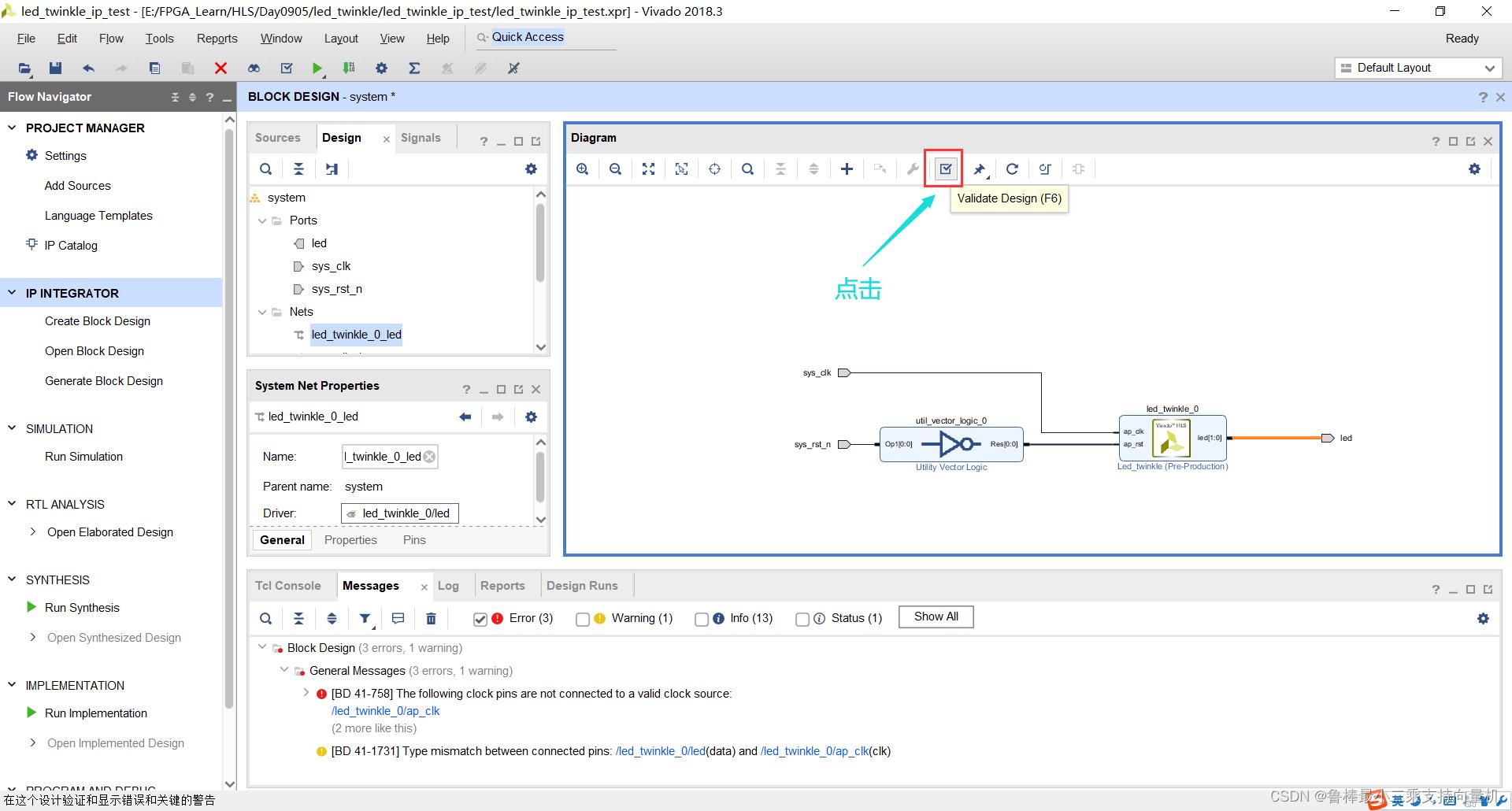

验证设计,如图所示:

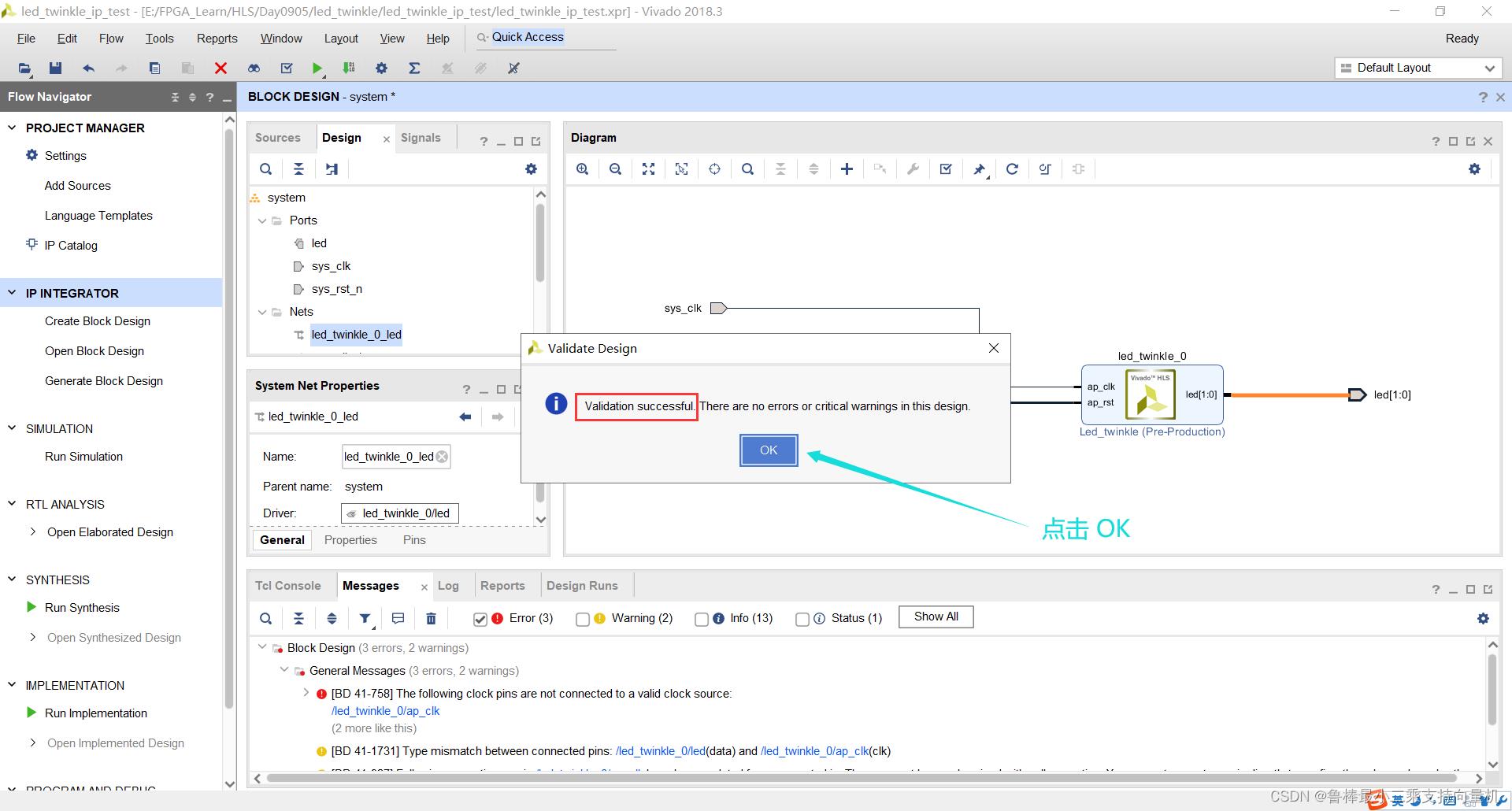

验证成功,点击OK:

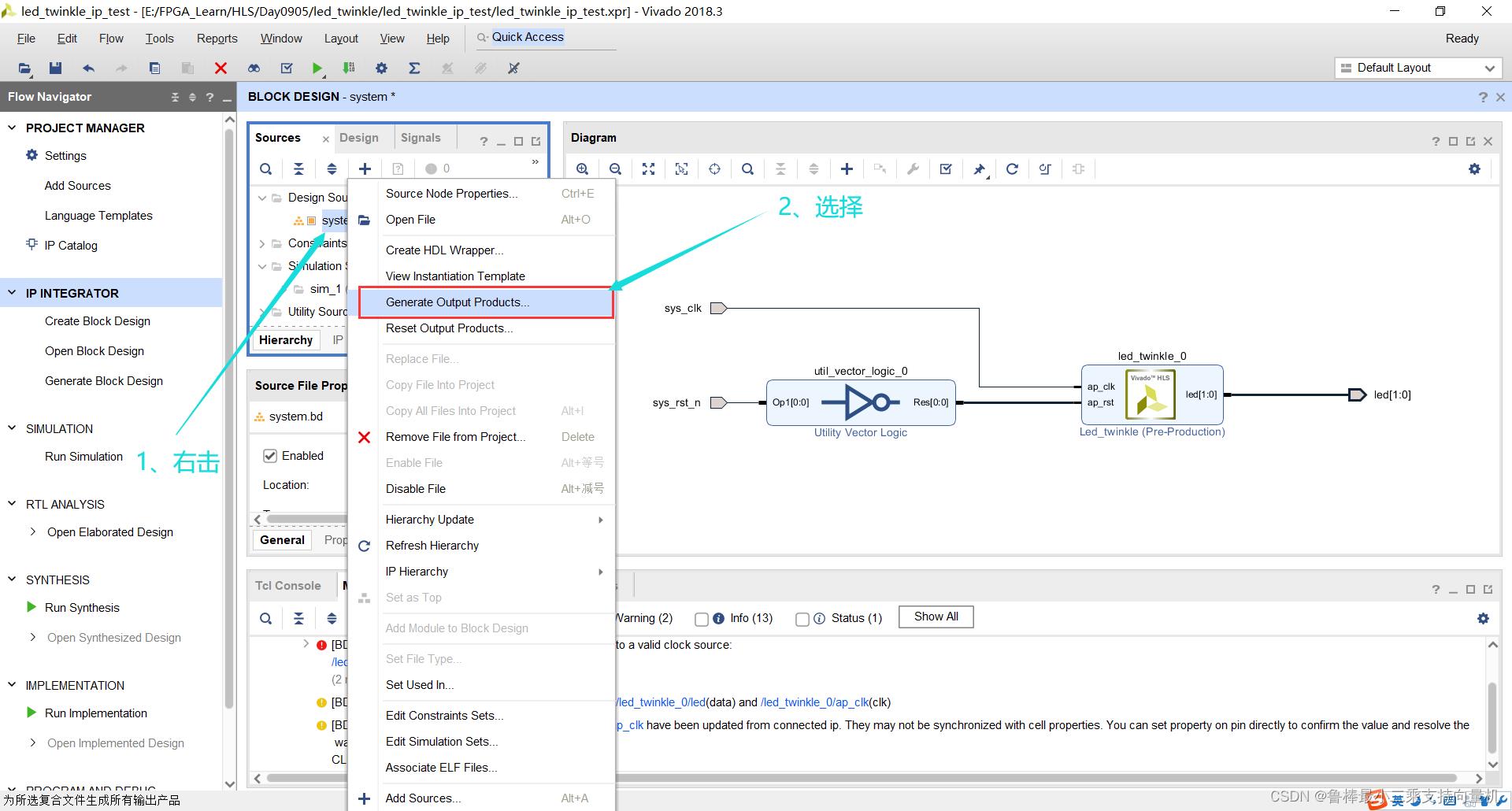

生成输入,操作如下:

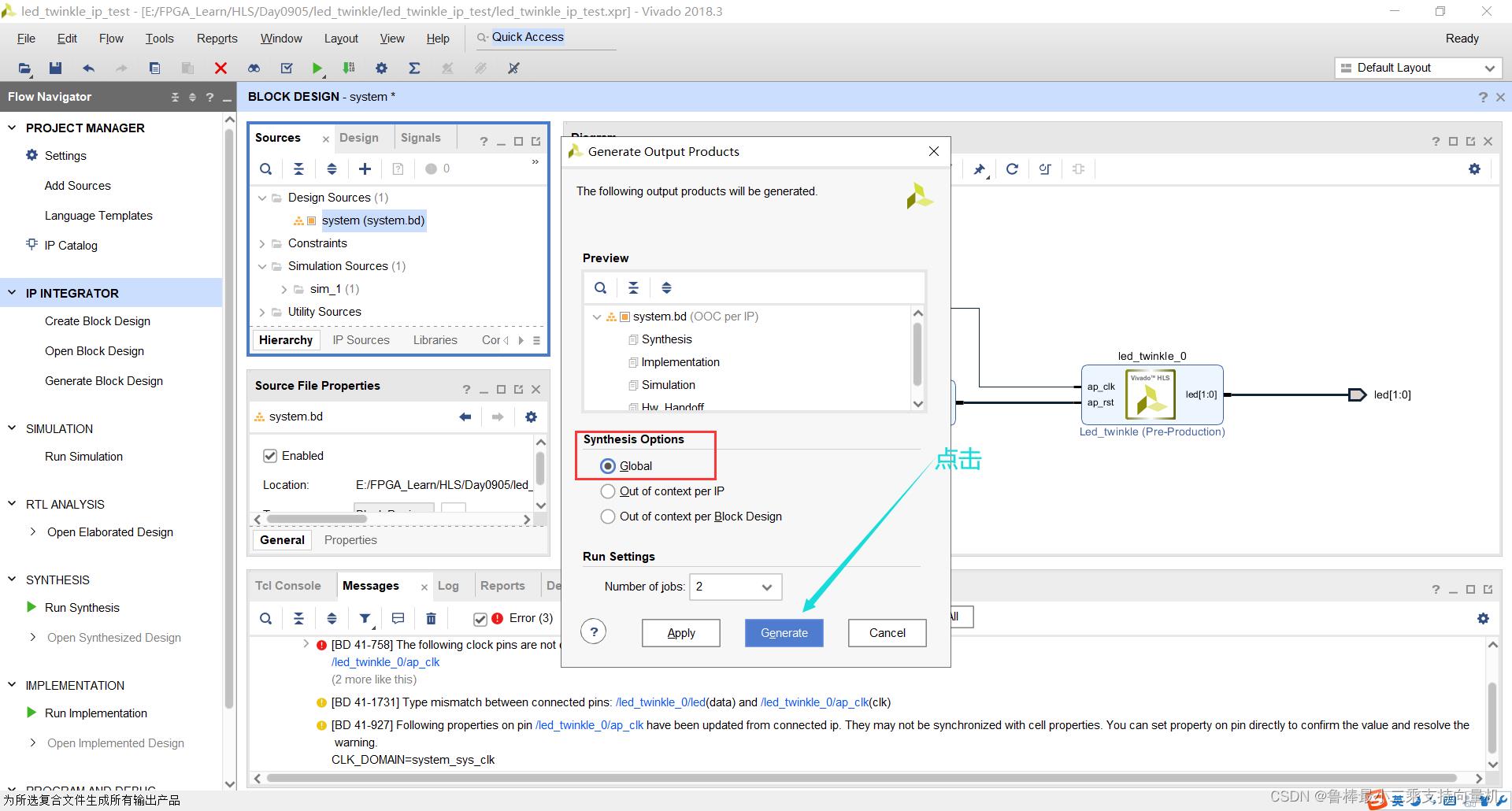

选择Global,点击Generate:

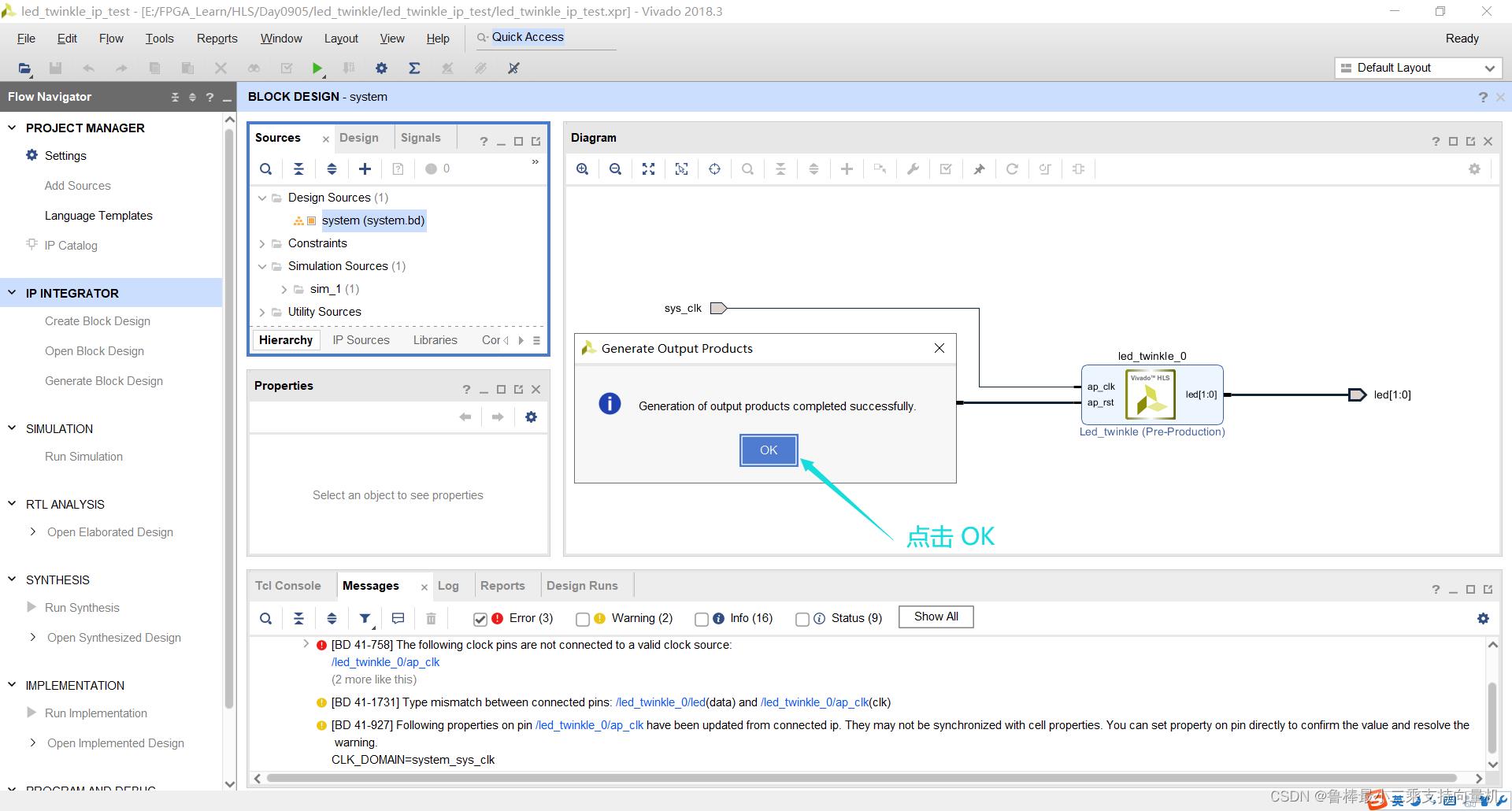

成功后,点击OK:

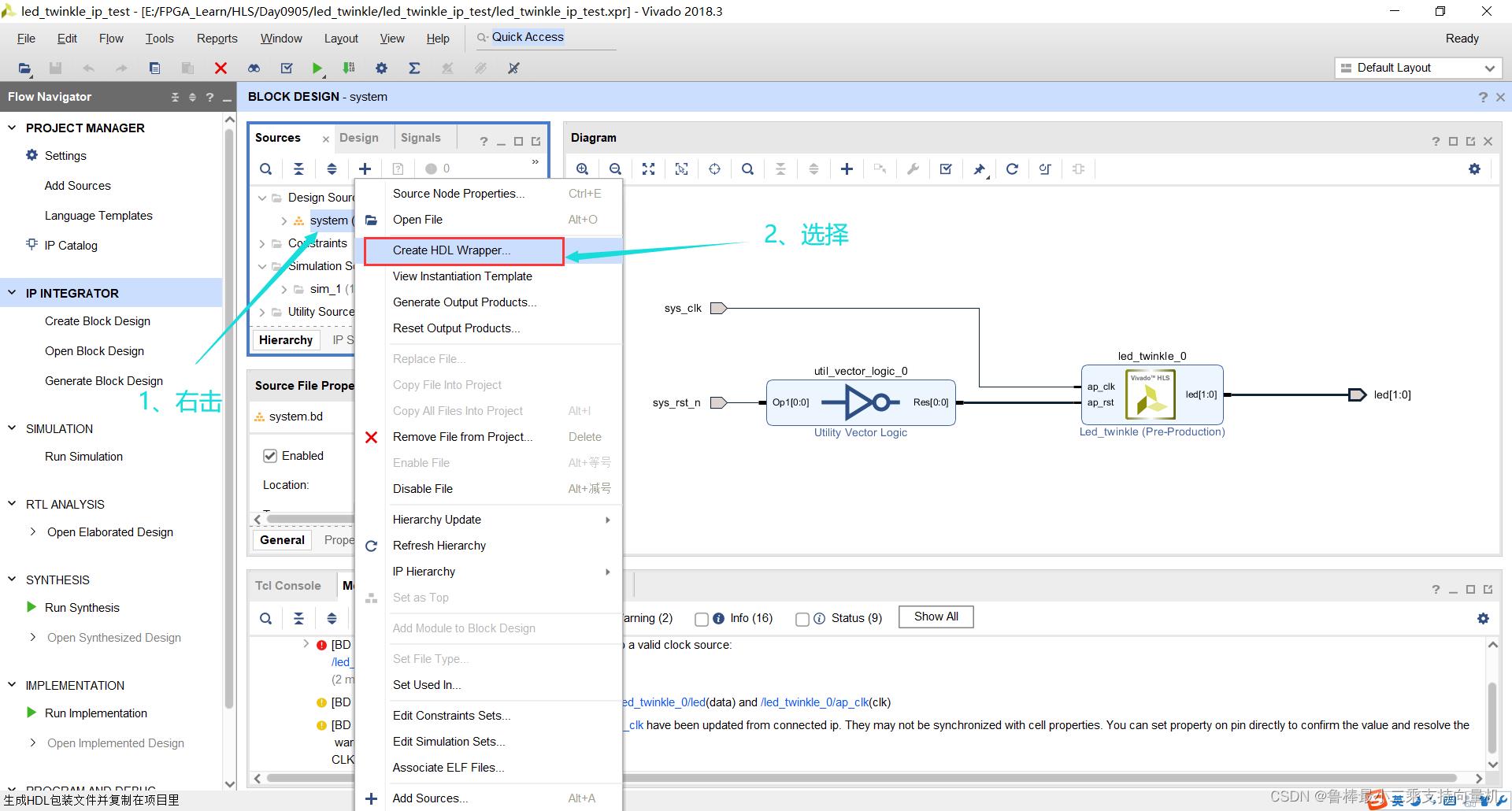

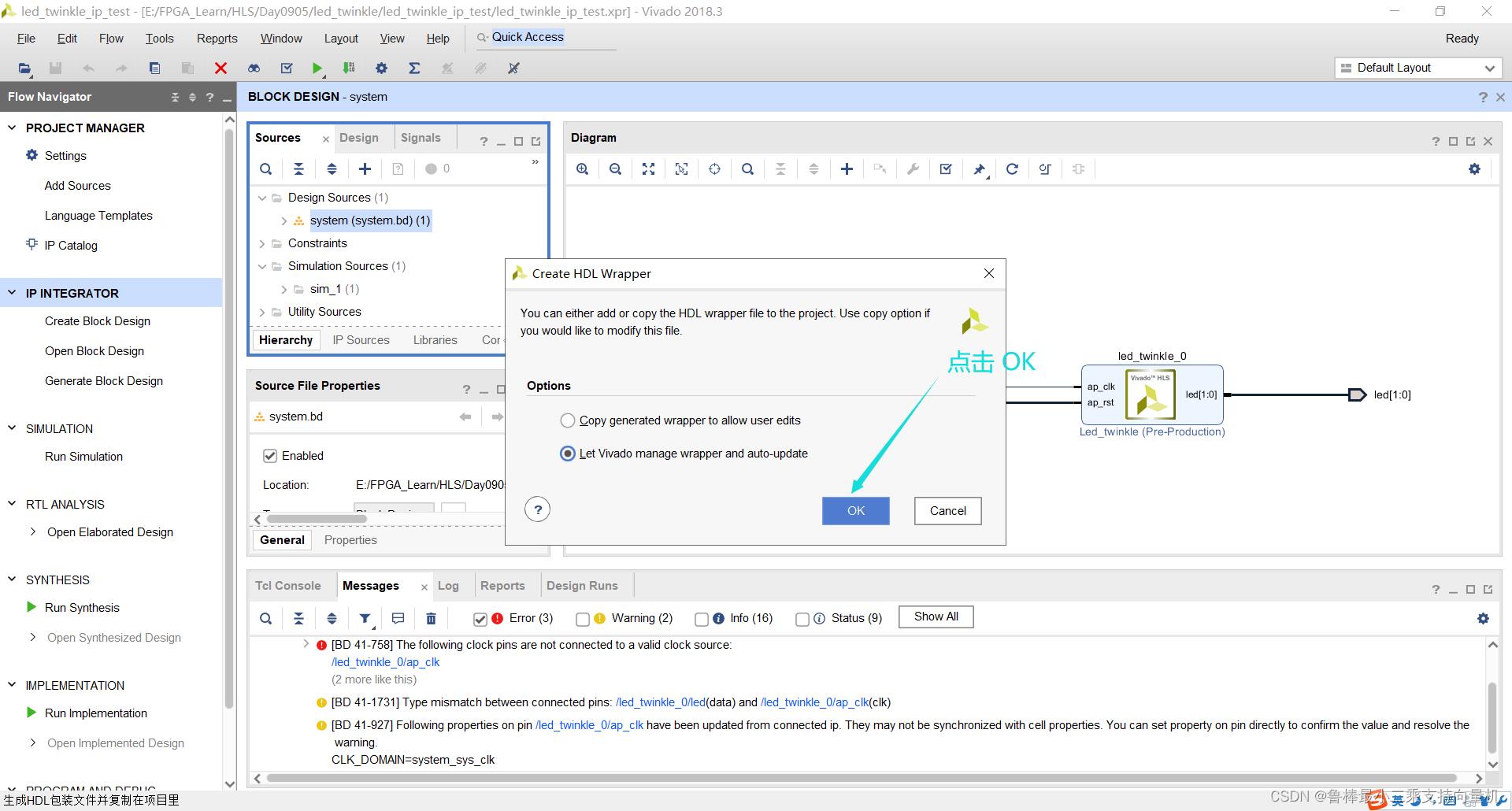

创建HDL,如图操作:

弹出如下窗口,点击OK:

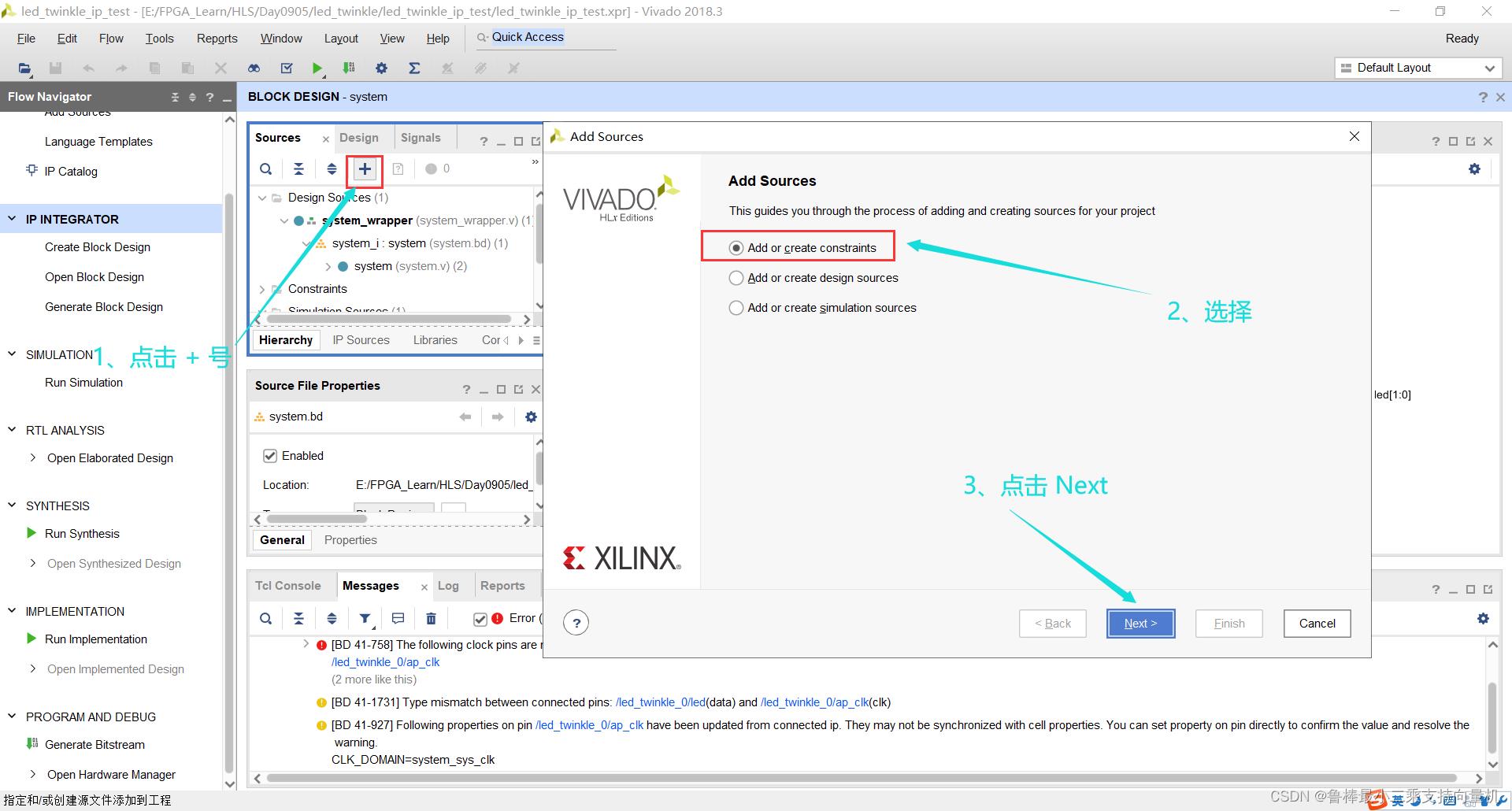

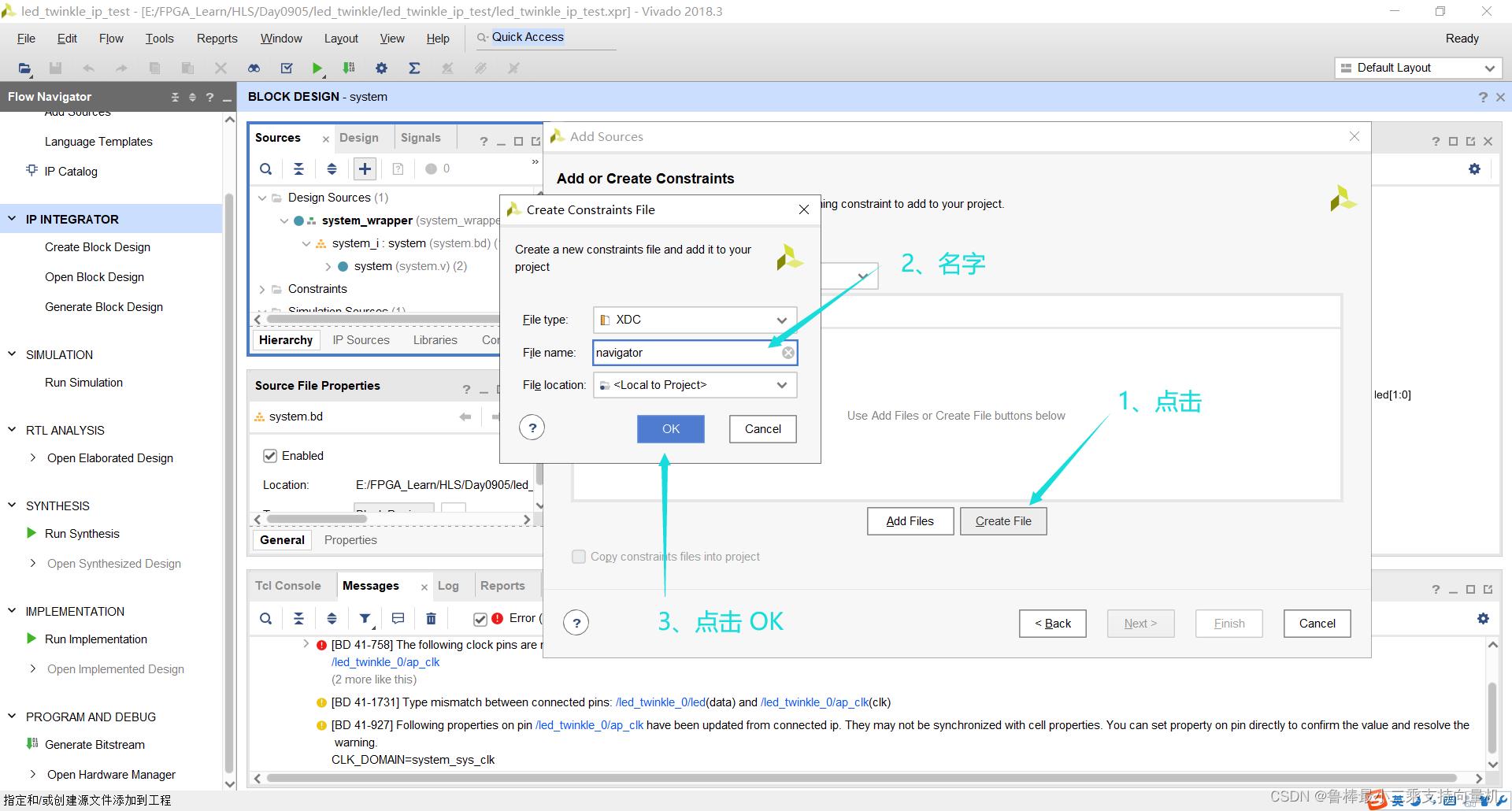

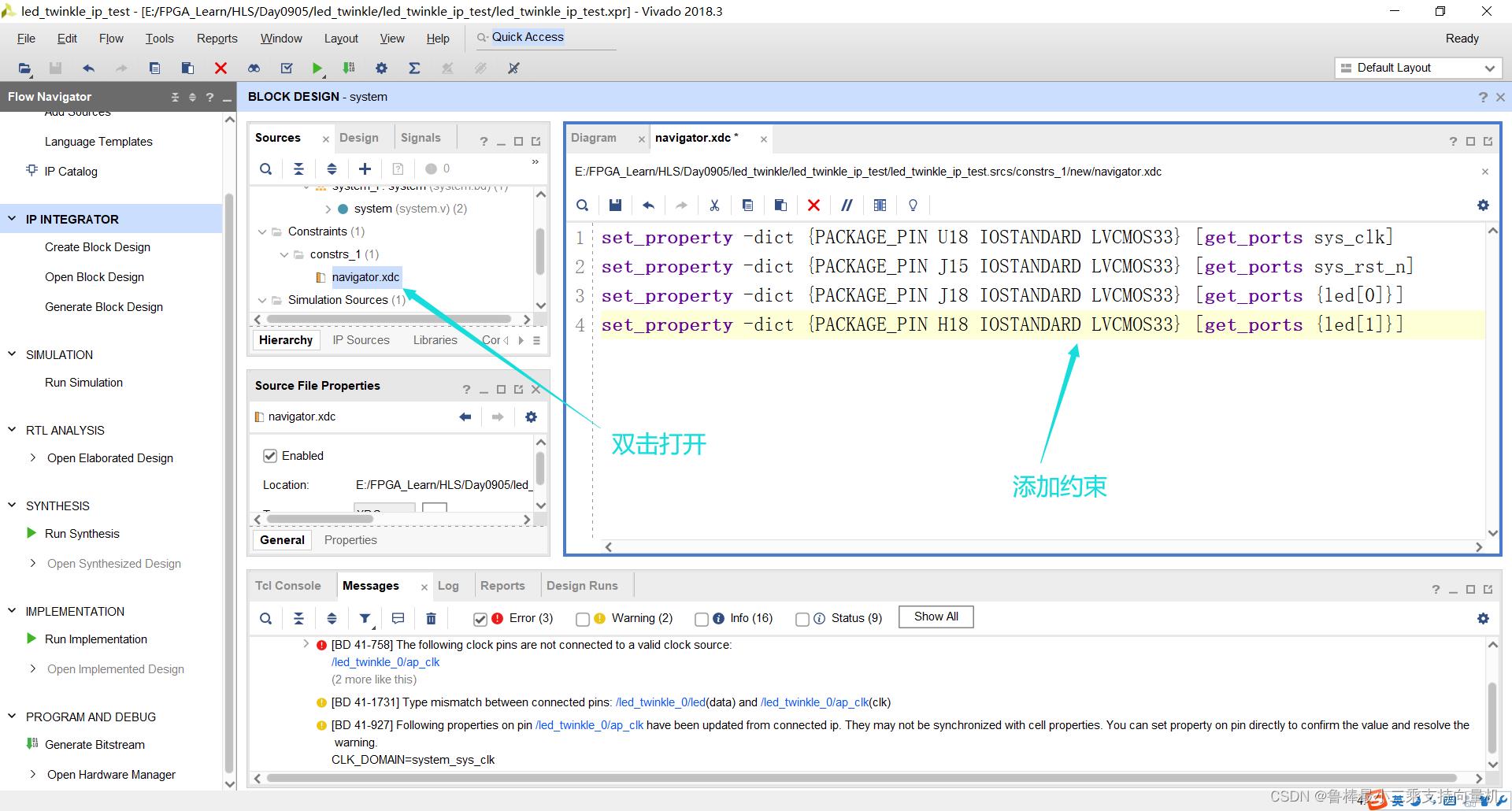

创建约束文件,操作如下:

输入名字,点击OK:

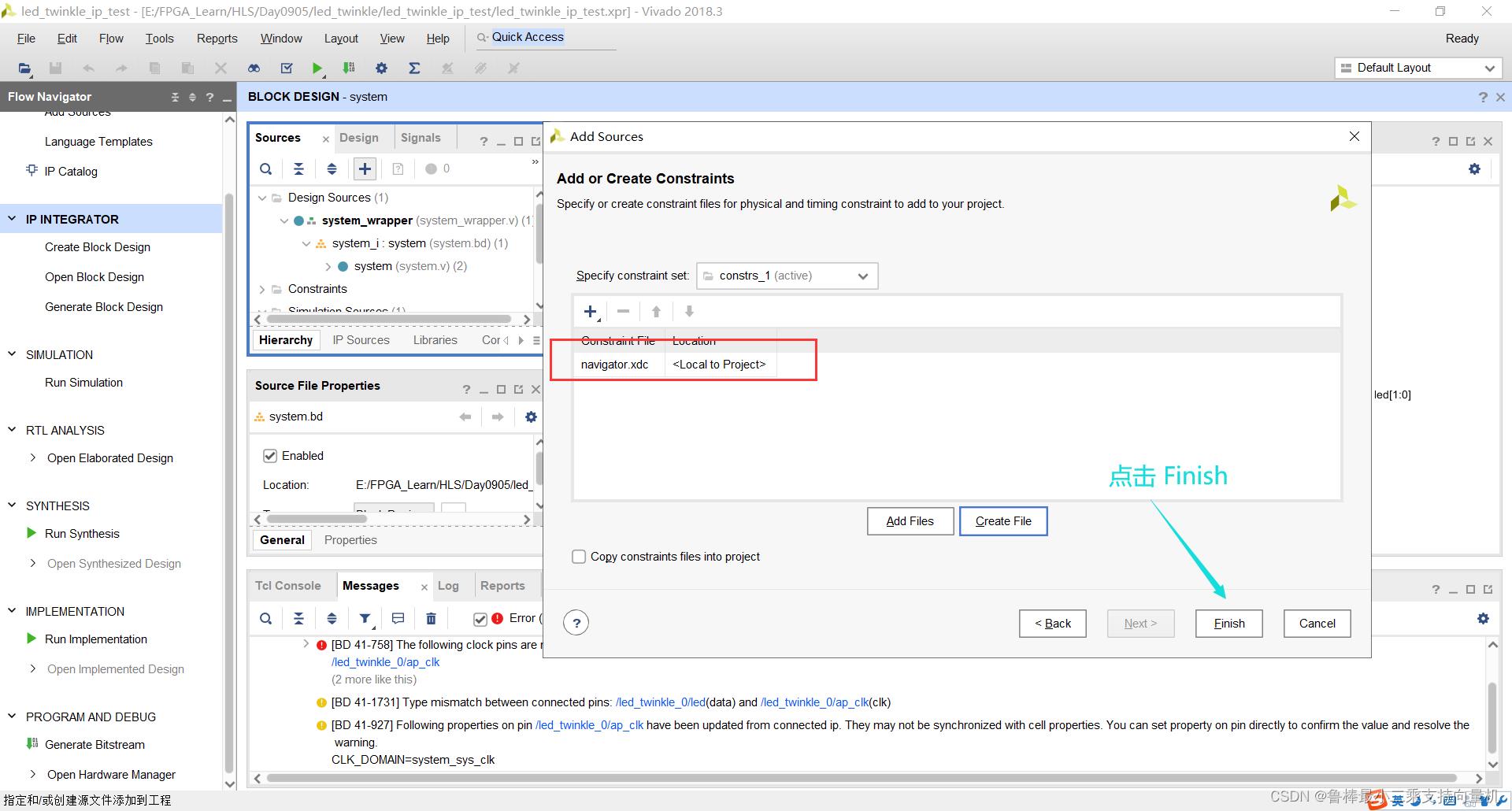

完成约束创建:

管脚约束代码:

set_property -dict PACKAGE_PIN U18 iosTANDARD LVCMOS33 [get_ports sys_clk]

set_property -dict PACKAGE_PIN J15 IOSTANDARD LVCMOS33 [get_ports sys_rst_n]

set_property -dict PACKAGE_PIN J18 IOSTANDARD LVCMOS33 [get_ports led[0]]

set_property -dict PACKAGE_PIN H18 IOSTANDARD LVCMOS33 [get_ports led[1]]

添加管脚约束信息:

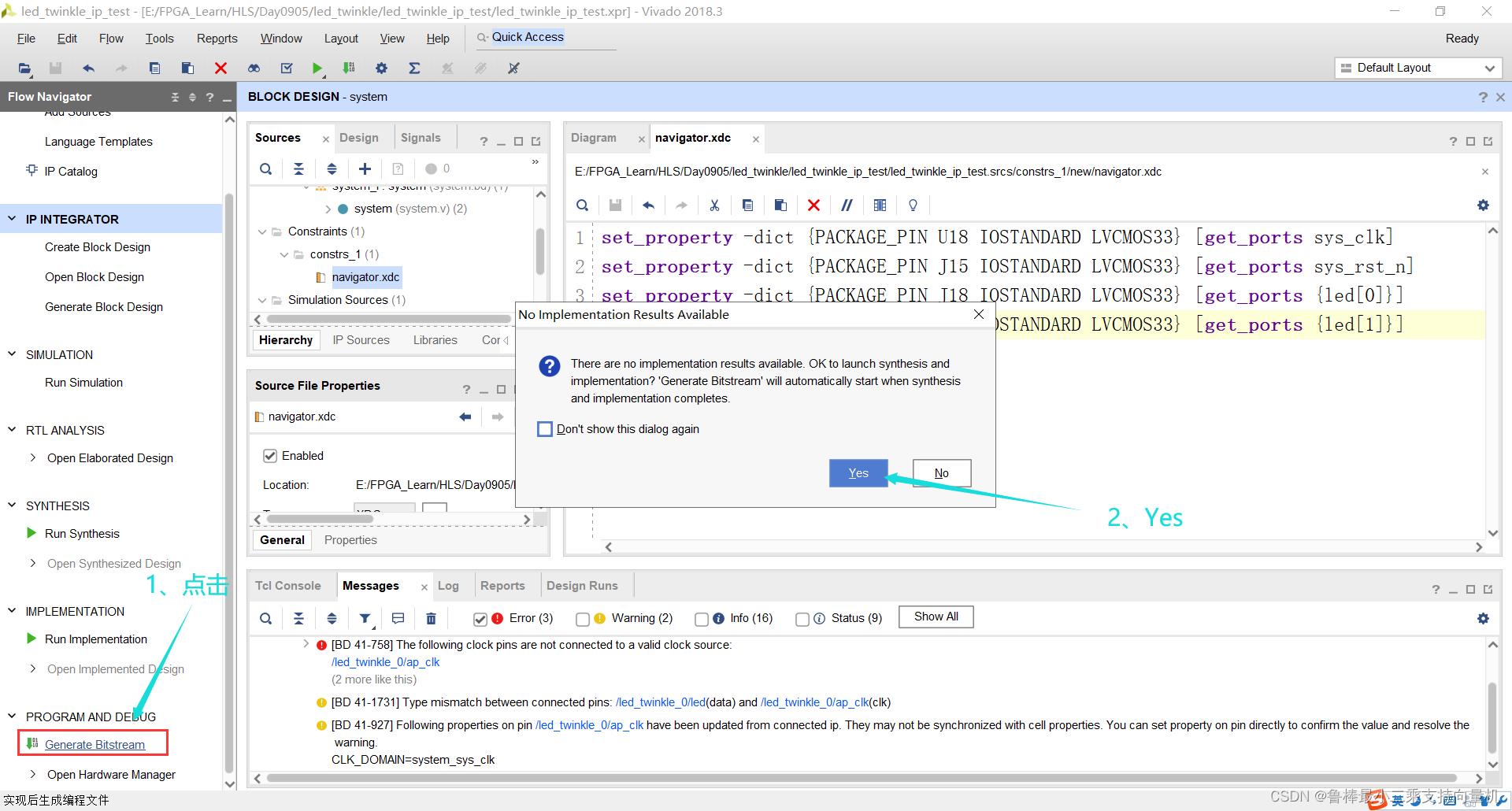

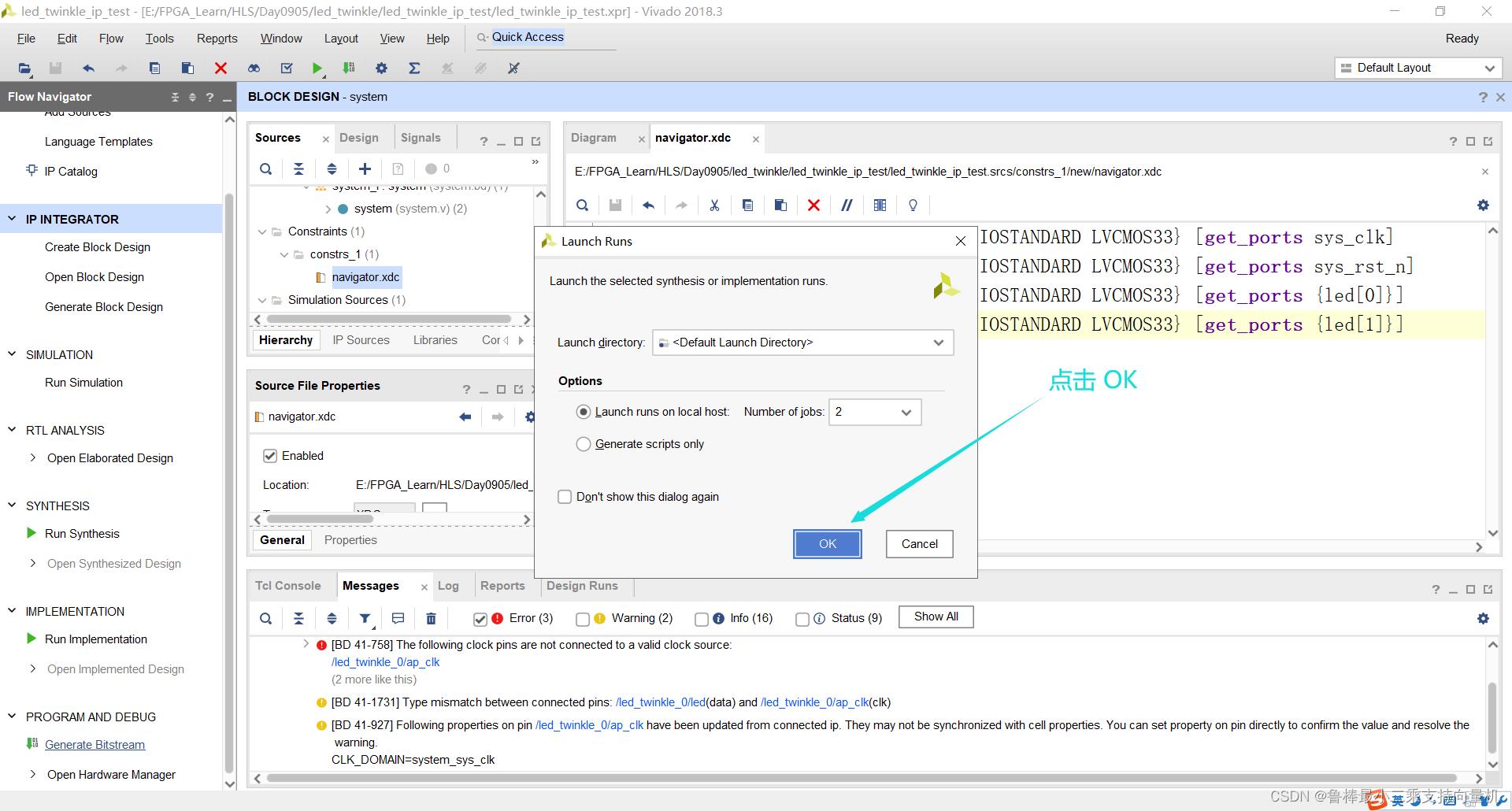

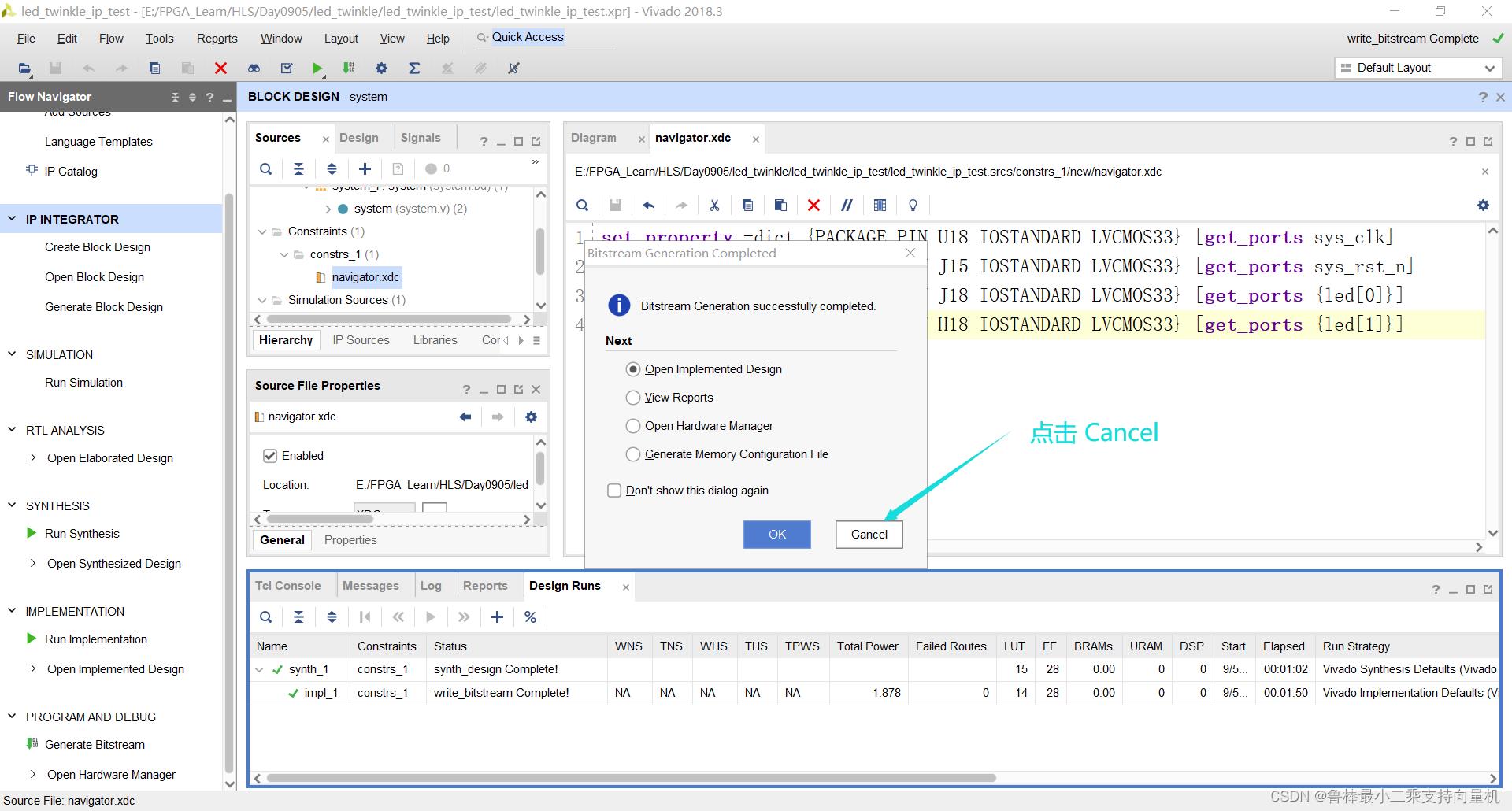

生成比特流文件:

点击OK:

点击Cancel即可:

2.3 下载验证

由于疫情,一直无法去实验室,故ZYNQ开发板不在身边,该步骤内容待更新

致谢领航者ZYNQ开发板,开启ZYNQ学习之路!

希望本文对大家有帮助,上文若有不妥之处,欢迎指正

分享决定高度,学习拉开差距

以上是关于ZYNQ之HLS学习----开篇实验的主要内容,如果未能解决你的问题,请参考以下文章