AXI总线简介

Posted bobuddy

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了AXI总线简介相关的知识,希望对你有一定的参考价值。

XI4.0-lite是AXI的简化版本,ACE4.0 是AXI缓存一致性扩展接口,AXI4.0-stream是ARM公司和Xilinx公司一起提出,主要用在FPGA进行以数据为主导的大量数据的传输应用。

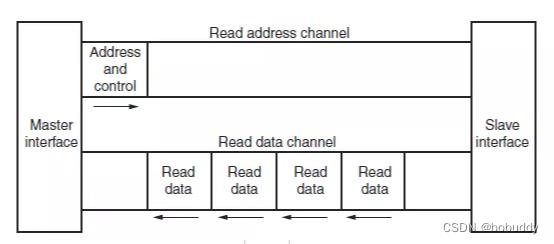

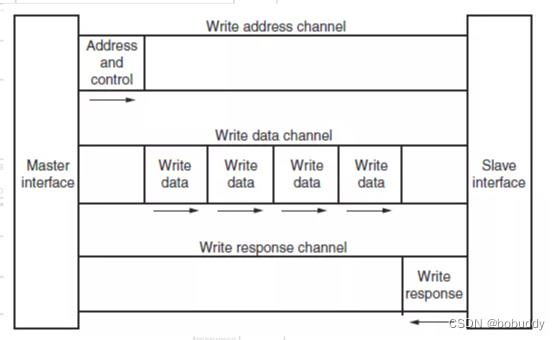

AXI协议是基于burst的传输,并且定义了5个独立的传输通道:读地址通道、读数据通道、写地址通道、写数据通道、写响应通道。地址通道携带控制消息用于描述被传输的数据属性,数据传输使用写通道来实现“主”到“从”的传输,“从”使用写响应通道来完成一次写传输;读通道用来实现数据从“从”到“主”的传输。DSP 地址数据分开

读通道架构

写通道架构

AXI是基于VALID/READY的握手机制数据传输协议,传输源端使用VALID表明地址/控制信号、数据是有效的,目的端使用READY表明自己能够接收信息。

读/写地址通道:读、写传输每个都有自己的地址通道,对应的地址通道承载着对应传输的地址控制信息。

读数据通道:读数据通道承载着读数据和读响应信号包括数据总线(8/16/32/64/128/256/512/1024bit)和指示读传输完成的读响应信号。

写数据通道:写数据通道的数据信息被认为是缓冲(buffered)了的,“主”无需等待“从”对上次写传输的确认即可发起一次新的写传输。写通道包括数据总线(8/16...1024bit)和字节线(用于指示8bit 数据信号的有效性)。

写响应通道:“从”使用写响应通道对写传输进行响应。所有的写传输需要写响应通道的完成信号。

全局信号

信号名 源 描述

ACLK 时钟源 全局时钟信号

ARESETn 复位源 全局复位信号,低有效

写地址通道信号

信号名 源 描述

AWID 主机 写地址ID,用来标志一组写信号

AWADDR 主机 写地址,给出一次写突发传输的写地址

AWLEN 主机 突发长度,给出突发传输的次数

AWSIZE 主机 突发大小,给出每次突发传输的字节数

AWBURST 主机 突发类型

AWLOCK 主机 总线锁信号,可提供操作的原子性

AWCACHE 主机 内存类型,表明一次传输是怎样通过系统的

AWPROT 主机 保护类型,表明一次传输的特权级及安全等级

AWQOS 主机 质量服务QoS

AWREGION 主机 区域标志,能实现单一物理接口对应的多个逻辑接口

AWUSER 主机 用户自定义信号

AWVALID 主机 有效信号,表明此通道的地址控制信号有效

AWREADY 从机 表明“从”可以接收地址和对应的控制信号

写数据通道信号

信号名 源 描述

WID 主机 一次写传输的ID tag

WDATA 主机 写数据

WSTRB 主机 写数据有效的字节线,用来表明哪8bits数据是有效的

WLAST 主机 表明此次传输是最后一个突发传输

WUSER 主机 用户自定义信号

WVALID 主机 写有效,表明此次写有效

WREADY 从机 表明从机可以接收写数据

写响应通道信号

信号名 源 描述

BID 从机 写响应ID tag

BRESP 从机 写响应,表明写传输的状态

BUSER 从机 用户自定义

BVALID 从机 写响应有效

BREADY 主机 表明主机能够接收写响应

读地址通道信号

信号名 源 描述

ARID 主机 读地址ID,用来标志一组写信号

ARADDR 主机 读地址,给出一次写突发传输的读地址

ARLEN 主机 突发长度,给出突发传输的次数

ARSIZE 主机 突发大小,给出每次突发传输的字节数

ARBURST 主机 突发类型

ARLOCK 主机 总线锁信号,可提供操作的原子性

ARCACHE 主机 内存类型,表明一次传输是怎样通过系统的

ARPROT 主机 保护类型,表明一次传输的特权级及安全等级

ARQOS 主机 质量服务QoS

ARREGION 主机 区域标志,能实现单一物理接口对应的多个逻辑接口

ARUSER 主机 用户自定义信号

ARVALID 主机 有效信号,表明此通道的地址控制信号有效

ARREADY 从机 表明“从”可以接收地址和对应的控制信号

读数据通道信号

信号名 源 描述

RID 从机 读ID tag

RDATA 从机 读数据

RRESP 从机 读响应,表明读传输的状态

RLAST 从机 表明读突发的最后一次传输

RUSER 从机 用户自定义

RVALID 从机 表明此通道信号有效

RREADY 主机 表明主机能够接收读数据和响应信息

低功耗接口信号

信号名 源 描述

CSYSREQ 时钟控制器 系统退出低功耗请求,此信号从“时钟控制器”到“外设”

CSYSACK 外设 退出低功耗状态确认

CACTIVE 外设 外设请求时钟有效

AXI协议是基于burst的,主机只给出突发传输的第一个字节的地址,从机必须计算突发传输后续的地址。突发传输不能跨4KB边界(防止突发跨越两个从机的边界,也限制了从机所需支持的地址自增数)。

1)突发长度

ARLEN[7:0]决定读传输的突发长度,AWLEN[7:0]决定写传输的突发长度。AXI3只支持1~16次的突发传输(Burst_length=AxLEN[3:0]+1),AXI4扩展突发长度支持INCR突发类型为1~256次传输,对于其他的传输类型依然保持1~16次突发传输(Burst_Length=AxLEN[7:0]+1)。

burst传输具有如下规则:

wraping burst ,burst长度必须是2,4,8,16

burst不能跨4KB边界

不支持提前终止burst传输

所有的组件都不能提前终止一次突发传输。然而,主机可以通过解断言所有的写的strobes来使非所有的写字节来减少写传输的数量。读burst中,主机可以忽略后续的读数据来减少读个数。也就是说,不管怎样,都必须完成所有的burst传输。

ARSIZE[2:0],读突发传输;

AWSIZE[2:0],写突发传输。

AxSIZE[2:0] bytes in transfer

'b000 1

'b001 2

'b010 4

'b011 8

'b100 16

'b101 32

'b110 64

'b111 128

突发类型

FIXED:突发传输过程中地址固定,用于FIFO访问

INCR:增量突发,传输过程中,地址递增。增加量取决AxSIZE的值。

WRAP:回环突发,和增量突发类似,但会在特定高地址的边界处回到低地址处。回环突发的长度只能是2,4,8,16次传输,传输首地址和每次传输的大小对齐。最低的地址整个传输的数据大小对齐。回环边界等于(AxSIZE*AxLEN)。

AxBURST[1:0] burst type

'b00 FIXED

'b01 INCR

'b10 WRAP

'b11 Reserved

Start_Address=AxADDR

Number_Bytes=2^AxSIZE

Burst_Length=AxLEN+1

Aligned_Addr=(INT(Start_Address/Number_Bytes))xNumber_Bytes。//INT表示向下取整。

对于INCR突发和WRAP突发但没有到达回环边界,地址由下述方程决定:

Address_N=Aligned_Address+(N-1)xNumber_Bytes

WRAP突发,突发边界:

Wrap_Boundary=(INT(Start_Address/(Number_Bytes x Burst_Length)))x(Number_Bytes x Burst_Length)

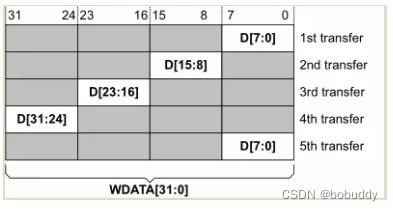

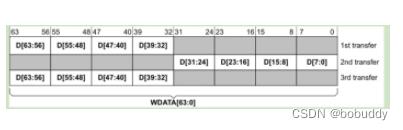

WSTRB[n:0]对应于对应的写字节,WSTRB[n]对应WDATA[8n+7:8n]。WVALID为低时,WSTRB可以为任意值,WVALID为高时,WSTRB为高的字节线必须指示有效的数据。

下图给出了5次突发传输,起始地址为0,每次传输为8bit,数据总线为32bit,突发类型为INCR。

下图给出3次突发,起始地址为4,每次传输32bit,数据总线为64bit。

读写响应结构

读传输的响应信息是附加在读数据通道上的,写传输的响应在写响应通道。

RRESP[1:0],读传输

BRESP[1:0],写传输

OKAY('b00):正常访问成功

EXOKAY('b01):Exclusive 访问成功

SLVERR('b10):从机错误。表明访问已经成功到了从机,但从机希望返回一个错误的情况给主机。

DECERR('b11):译码错误。一般由互联组件给出,表明没有对应的从机地址。

-----------------------------------

以上是关于AXI总线简介的主要内容,如果未能解决你的问题,请参考以下文章