入驻企业 | 芯峰科技发布DEFLATE/GZIP压缩芯片IP,芯片设计进入高铁时代

Posted 广州国际AI研究院

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了入驻企业 | 芯峰科技发布DEFLATE/GZIP压缩芯片IP,芯片设计进入高铁时代相关的知识,希望对你有一定的参考价值。

近日,广州国际AI研究院入驻企业芯峰科技(广州)有限公司成功研发出一款高性能deflate/gzip压缩算法芯片IP,deflate是基础算法,使用LZ77和HUFFMAN编码,gzip在deflate的内核上增加了头尾字节,可以实现无损数据压缩。除了传统的数据备份、内存或缓存压缩,在大数据与人工智能场景下可以通过异构计算与减少网络传输来提高系统的整体性能。

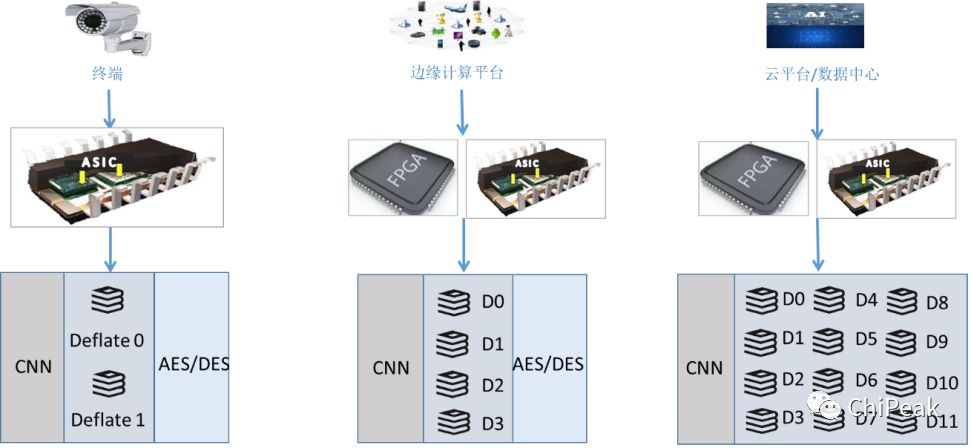

压缩模块是芯峰科技针对大数据与人工智能应用场景提供的整体解决方案的算法芯片系列的一部分,芯峰科技还在研发“芯峰神经网络算法芯片-CNN(Chipeak Neuro Network)”。这是一款通用AI算法芯片,支持多种算法(CNN RNN LSTM)的灵活组网(神经元与层数可调),不仅可以识别上万种物体,而且非结构化数据通过算法后转化成结构化信息,结合压缩算法后可以进一步提高系统的响应速度,使得原本只能离线处理的应用通过芯峰方案可以实现实时处理(如无人机视频分析)。

此外,芯峰科技还将推出加密算法IP(AES/DES等), 为数据传输提供安全保障。芯峰IP的特点是软件定义芯片-SDC(Software Defined Chip),根据所需性能通过配置参数用编译工具自动生成多核设计,可以分别应用于大数据与AI链路的不同位置,比如云计算、边缘计算以及终端。

芯峰AI场景芯片IP组合、多核设计及应用场景

芯峰压缩IP以及后续产品的快速发布,完全得益于芯峰科技独有的HLS工具。这是一款以行为级高级语言为设计语言的新一代芯片设计自动化工具,要比传统设计方法快3-10倍,使得芯片设计告别蒸汽机而进入高铁时代。

芯峰算法芯片设计工具软件

芯峰IP可以运行在FPGA(现场可编程门阵列),也可以集成到SoC或单独ASIC流片,DataShee会在近期发布,敬请期待,欢迎商务洽谈与合作。

据介绍,芯峰科技(广州)有限公司成立于2018年,是一家由IEEE Fellow、具有多年海外工作经验的连续创业者及国内优秀AI芯片设计人员联合创立的AI相关设计与异构计算加速服务企业。同年,加入中国半导体行业协会,成为集成电路设计分会会员和上海集成电路行业协会设计委员会成员,签约入驻广州国际人工智能产业研究院。

以上是关于入驻企业 | 芯峰科技发布DEFLATE/GZIP压缩芯片IP,芯片设计进入高铁时代的主要内容,如果未能解决你的问题,请参考以下文章

远程传输命令出错并出现意外响应:<h1>401: Unauthorized</h1>Unauthorized User: deflate, gzip

使用 PHP ob_start() 与 Apache Deflate/Gzip 压缩内容?

apache_conf .htaccess mod_deflate gZip压缩