AXI协议里面的cacheable和bufferable是啥意思

Posted

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了AXI协议里面的cacheable和bufferable是啥意思相关的知识,希望对你有一定的参考价值。

参考技术A cacheable[计] 可缓存的;

[英][kæ'keɪbl][美][kæ'keɪbl]

bufferable

可缓冲处理本回答被提问者和网友采纳

AXI协议:AXI架构的握手机制和实现细节

握手机制

6.1 握手机制概念介绍

以上5条独立的通道(AR,R,AW,W,B)都相互独立,且包含自身通道对应的一个信息信号和一个双路的VALID、READY信号(比如ARVALID/AWREAADY)来实现握手机制。

官方文档叙述:作为一种双向流控机制,VALID/READY 机制可以使发送接收双方都有能力控制传输速率。

同时还有一个概念,在握手机制中,通信双方分别扮演如下两个角色:

- 源设备,也就是发送方(source),源设备指的是发出某个信号的源

- 目标设备,也就是接收方(destination),目标设备是这个源想要抵达的地方

两者的操作(技能)并不相同。

注意:

并不一定代表VALID信号就来自于master,READY信号就来自于SLAVE。其实是VALID来自于source,READY来自于destination。

记忆方法:

由于读写的不同,是否准备好是由目标设备发出的。

对于读来说,source是slave,destination是master,所以在这个通道内部,VALID其实是slave发出,READY是master发出

对于写来说,source是master,destination是slave,所以在这个通道内部,VALID其实是master发出,READY是slave发出

6.2 握手机制阐释

对于每一个通道,握手机制都是一样的实现过程。即通过这个双路信号实现,其实就是source发送VALID作为确认信息,destination发送READY作为确认信息,其实是反应master和slave之间是否达成共识的一个标志。

- source设备通过使VALID信号有效,来指示通道中的数据或者地址或者控制信息有效。(数据通道VALID表示数据有效,地址控制通道表示地址控制信息有效),并保持在消息总线上

- destination设备通过使READY信号有效,来表示已经为接受做好准备

- 当双方的VALID和READY信号同时为有效(也就是高电平),可以说这时候,各自通道内的东西,达成共识,开始发挥作用,在时钟 ACLK 上升沿,完成一次传输。所有传输完毕后,双方同时置低自己的信号。

- 读数据和写数据通道都包括一个LAST信号,用来指明一个事物传输的最后一个数据。

6.3 双流控制的理解

所谓的双向流控机制,指的是发送方通过置起 VALID 信号控制发送的时机与速度,接收方也可以通过 READY 信号的置起与否控制接收速度。

发送方拥有传输的主动权,但接收方在不具备接收能力时,也能够置低信号停止传输,反压发送方。

6.4 读事务握手机制时序图

显示了四次传输(DA0~DA3)的读取事务。在本例中,master在AR通道给出起始地址和控制信息A,同时ARVALID置高有效,此时(T1上升沿)ARREADY无效,一个周期后(T2),slave的ARREADY有效,握手成功。AR通道握手成功后,A信息就传过去了。这时候T5-T6时候slave准备好了读通道的数据DA0,将RVALID置高有效,等待T6上升沿完成第一个数据的握手传输。在传输突发信号时,slave断言RLAST信号,以表明最后一个数据项正在被传输(这里可以理解一下为什么没有读响应通道,主要是通过这个信号和RREADY还有RVALID的几个逻辑关系,还需要仔细再想一下ZZQ)

备注说明1:主机在给出地址的时候,同时还驱动一组控制信号,但为了清晰起见,图中省略了信号,都用A表示。

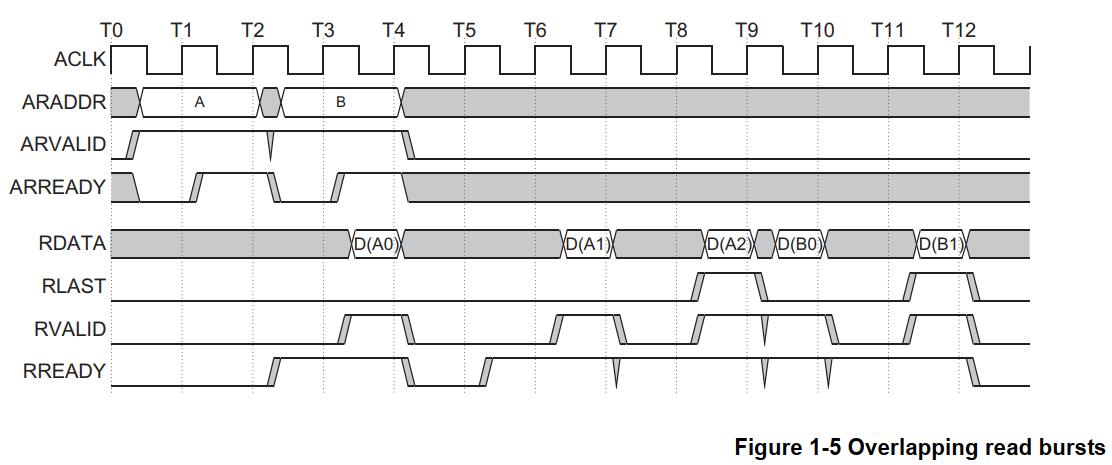

显示了在slave接受第一个地址后,master如何驱动另一个突发地址。这使slave能够在第一个突发完成的同时处理第二个突发的数据DB0~1

6.5 写事务握手机制时序图

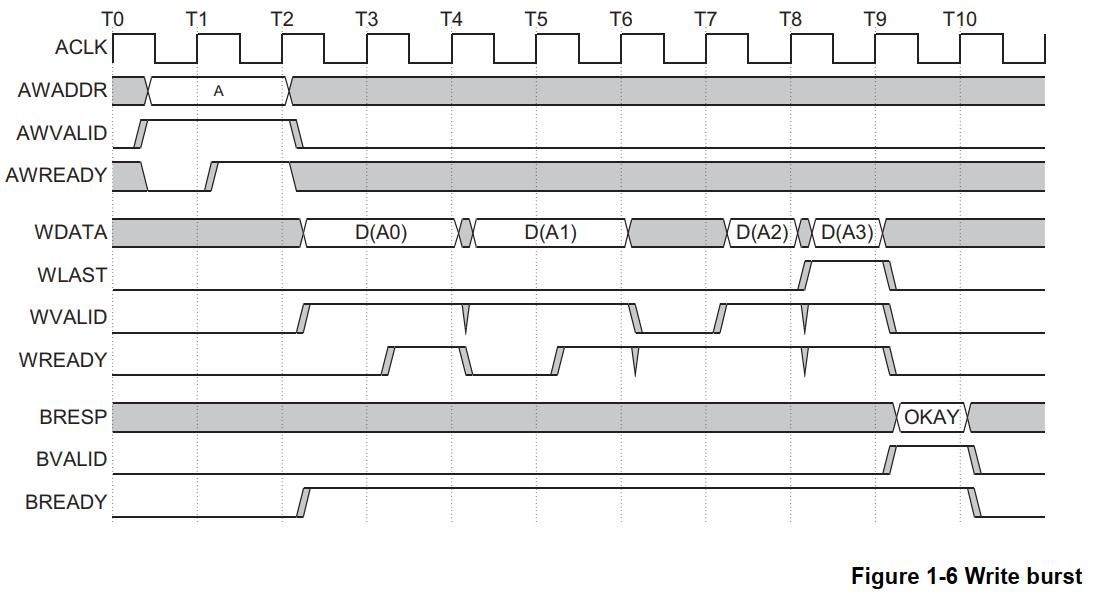

写事务:当主机在写地址通道上发送地址和控制信息A,同时将AWVALID置为有效的时候,该过程开始。然后T2达成握手,master通过写入数据通道发送写入数据DA0,同时WVALID置为有效。WREADY准备好后T4,完成写数据通道的握手,写第一个数据DA0,当主机发送最后一个数据项时,WLAST信号置高。当slave接受了所有数据项时,它会将写响应BRESP通过B通道驱动回主机,以指示写事务已完成。

6.6 VALID/READY 的三种情况,以及常用设置思考

6.6.1 情况1:VALID 信号先到达

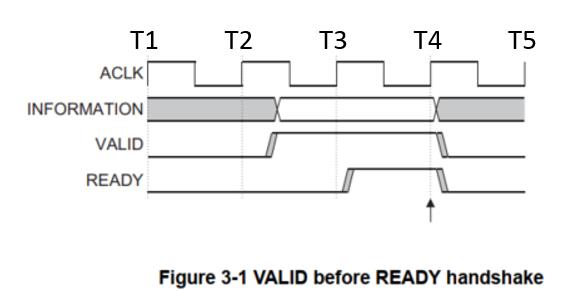

发送方 VALID 信号早早就到了,这时还不到 T3 时刻,并带来了新鲜的数据(数据通道),地址或者控制信息(地址通道),总之是信息(Information)。

但过了 T3 也没见到接收方的 READY 信号。原来是接收方还忙着,可能上一次的数据还没存完,还堵在数据通路上,忙过了 T3 才来。

T4 时刻传输完成。在这种情况下,接收方通过 READY 信号控制了传输速度,反压了发送速度。

协议规定在这种情况下,VALID 信号一旦置起就不能置低,直到完成握手(handshake occurs),至少传输一周期数据。

在设计接收方逻辑时,检测到 VALID 信号置起,如果系统正忙,完全可以让发送方等待,发送方在完成传输之前都不会置低 VALID 信号,不需要考虑发送方撤销传输的可能。

协议另外规定:发送方不能通过等待接收方 READY 信号来确定置起 VALID 信号的时机

这句中文阅读理解有点难,原文为:

A source is not permitted to wait until READY is asserted before asserting VALID.

个人理解,READY 信号可能先到达,如6.1.2的情况。但是设计发送方逻辑时,不能将 READY 信号作为置高 VALID 逻辑的条件,比如将 READY 信号通过组合逻辑生成 VALID 信号。

换句话说,发送方准备发送,置起 VALID 信号是完全主动与独立的过程。接收方 READY 信号按照协议可以依赖发送方 VALID 信号,但如果此时发送方也依赖接收方信号,就会造成死锁的情况,所以协议在这里强调了 VALID 信号的主动性。

module axi_src

...

//assign VALID = SRC_CONDITION && READY;//NOT permitted and may cause deadlock

assign VALID = SRC_CONDITION;//permitted

...

endmodule

module axi_dst

...

assign READY = CONDITION && VALID;//permitted

...

endmodule

6.6.2 情况2:READY 信号先到达

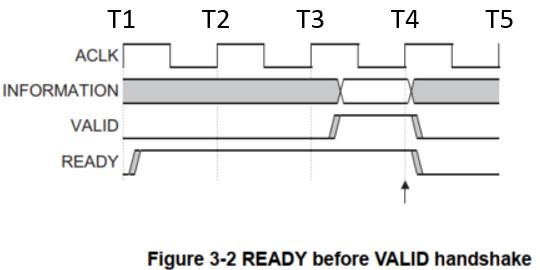

READY 信号很自由,可以等待 VALID 信号到来再做响应,但也完全可以在 VALID 信号到来前就置高,表示接收端已经做好准备了。

而且,READY 信号与 VALID 不同,接收方可以置起 READY 之后发现:其实我好像还挺忙,然后置低 READY 信号。只要此时 VALID 信号没有置起,这种操作是完全可以。

6.6.3 情况3:同时到达

同时到达就很简单,等到下一个时钟上升沿 T2,传输就这么轻松愉快地在一个时钟周期里完成了。

6.6.4 实现细节

前文我们讨论过, READY 信号原则上由接收方自身的接收状况以及 VALID 信号控制。(或者仅由接收方自身的接收状况决定)协议中没有规定 READY 信号的默认状态,即未进行传输时的电平状态(default value)。

协议建议 AW/AR READY 信号的默认电平为高电平。若默认电平为低,则每次传输至少需要 2 个周期才能完成,第一个周期置高 VALID 信号,第二个周期从机才会置高 READY 信号。相当于每次传输增加 1 个周期时间开销,这在某些情况下会对传输效率有较大的影响。

以上是关于AXI协议里面的cacheable和bufferable是啥意思的主要内容,如果未能解决你的问题,请参考以下文章