Quartus II中Power analyzer tool 的使用(功耗预估)

Posted 小鱼FPGA

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了Quartus II中Power analyzer tool 的使用(功耗预估)相关的知识,希望对你有一定的参考价值。

先给出官方的工具使用说明文档(英文的)链接:https://www.altera.com/documentation/osq1513989409475.html 这里面对一些设置选项讲解的很清楚,但是初学者看完之后肯定还是云里雾里,不知道怎么用。

这里我将以一个实例简单的描述一下Power analyzer tool通过后仿真(Gate Level Simulation)得到的VCD(Value Change Dump File )文件来做功耗的预估。

01

—

后仿真(Gate Level Simulation)并获取VCD文件

在做后仿之前先要做一下时序分析以保证电路所给的时钟满足时序要求,后面将会写相关时序仿真的文章。

这里选择后仿真来实现能耗评估是因为后仿真得到的评估数据比前仿真更准确。

具体操作步骤如下(以我设计的一个乘法器为例)。

在工程准备好了的前提下(包括设计与Testbench):

Tools -> Options -> EDA Tool Option

添加Modelsim的启动路径。

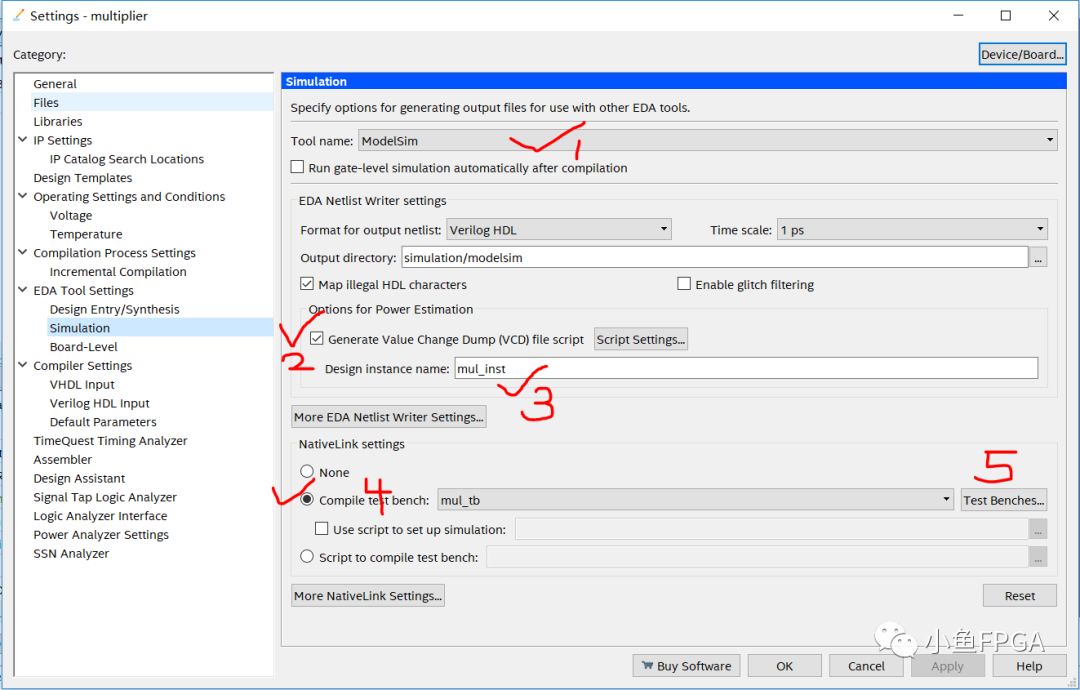

Assignments -> settings -> Simulation

几个重要的设置如下图所示(具体还可以参照文章)。

1. Tool name选择Modelsim

2. Generate Value Change Dump(VCD) file script 勾上。

3. Design Instance name:即你testbench里的例化的设计顶层模块例化名。

4. Compile test bench 勾上。

点击 5 位置的Test Benches,其后的具体设置参考文章的Quartus 调用 Modelsim 联合仿真部分。

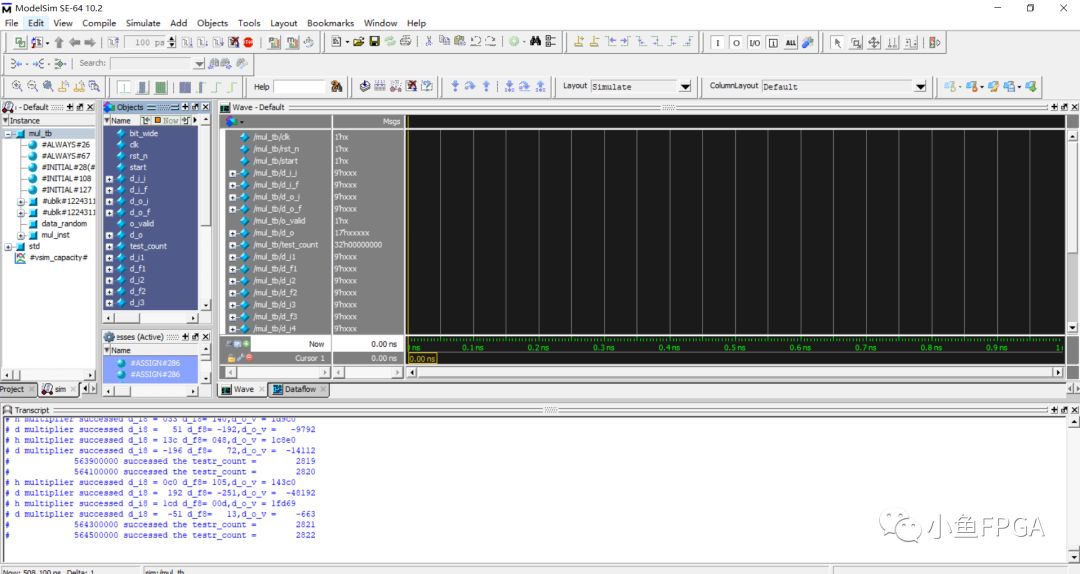

在上述所有设置结束后点击Quartus 的 Tool -> Run simulation tool -> Gate level simulation,其就会调用Modelsim开始仿真。

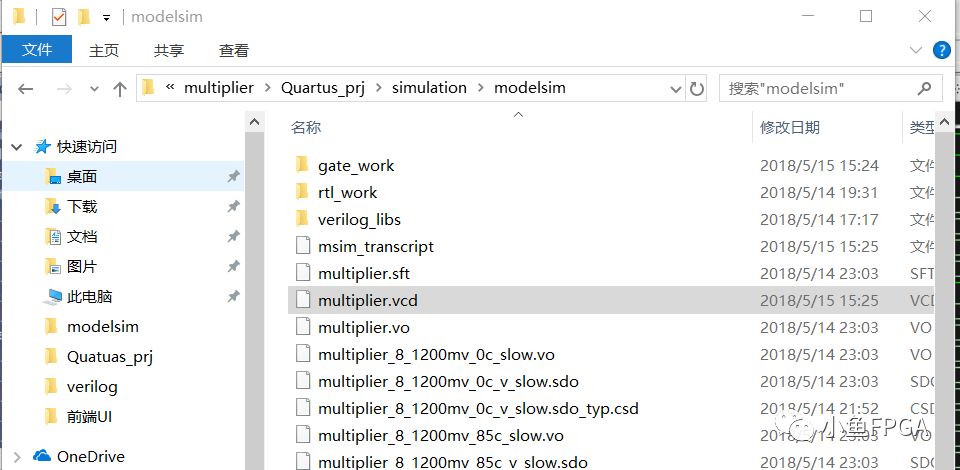

在仿真结束后,关闭Modelsim,此时你在Quartus工程根目录下的 simulation / modelsim下就会看到有一个 .vcd文件,名字与工程名一致。

这个vcd文件保存的就是在仿真过程中寄存器的翻转信息。

所以如果testbench编写的越到位,那么功耗预测也就越准确。

02

—

Power analyzer tool的使用

上述过程完成之后接下来的操作如下。

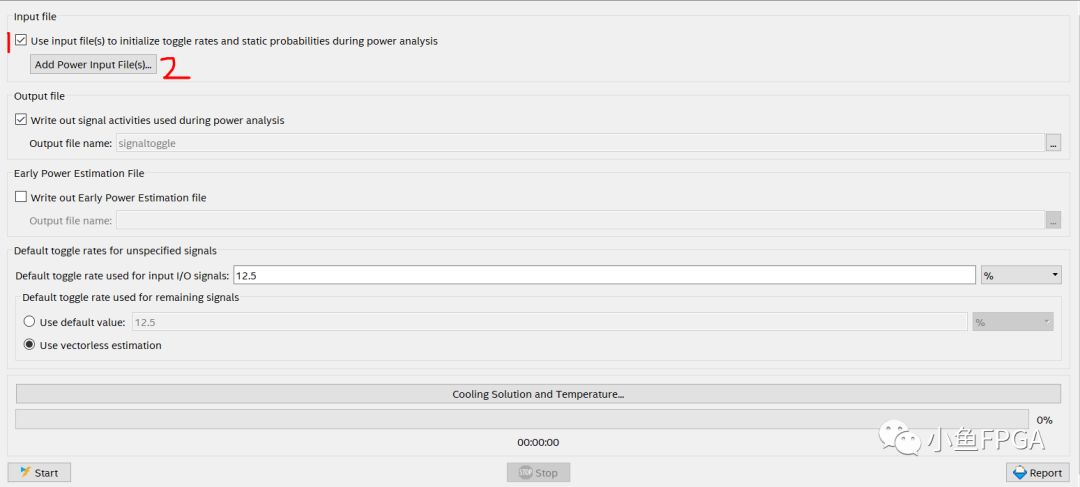

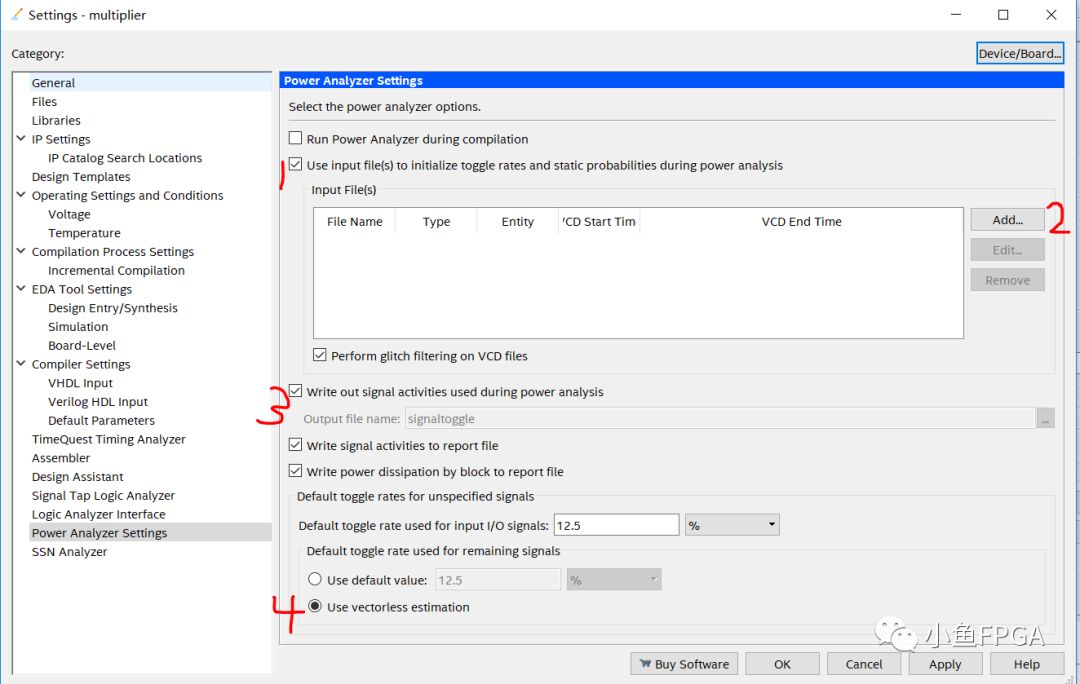

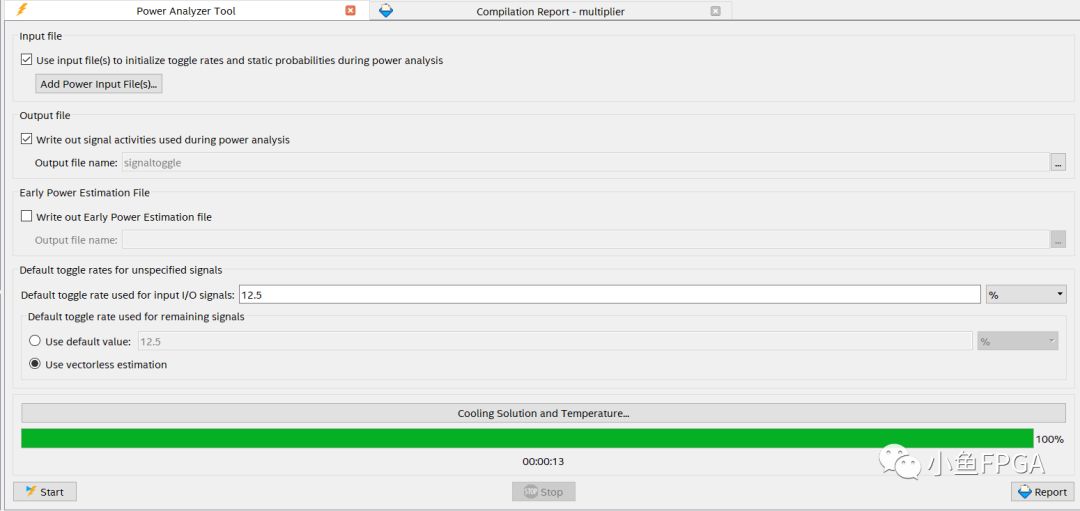

打开Quartus的Processing -> Power Analyzer Tool 得到如下界面。

设置操作如下:

1. 勾上 USE input file(s) to initialize toggle rates and static probabilities during...

2. 点击 Add Power Input File(s) 得到如下界面。

设置操作步骤如下:

1. 勾上 USE input file(s) to initialize toggle rates and static probabilities during...

2. 点击Add 得到如下界面

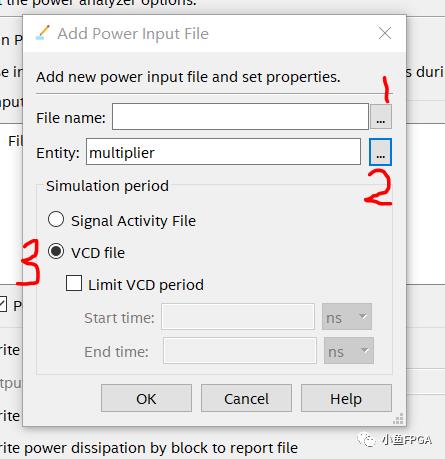

设置操作如下:

1. File name: 添加后仿真得到的VCD文件。

2. Entity: 选择你需要做功耗预测的模块,这里选择设计的顶层即可

3. VCD file 选上

4. Limit 可以不设置,也就是使用默认的,具体表示什么可以参考文章刚开始给出的官方说明文档链接。

5. 点击 OK。回到如下界面。

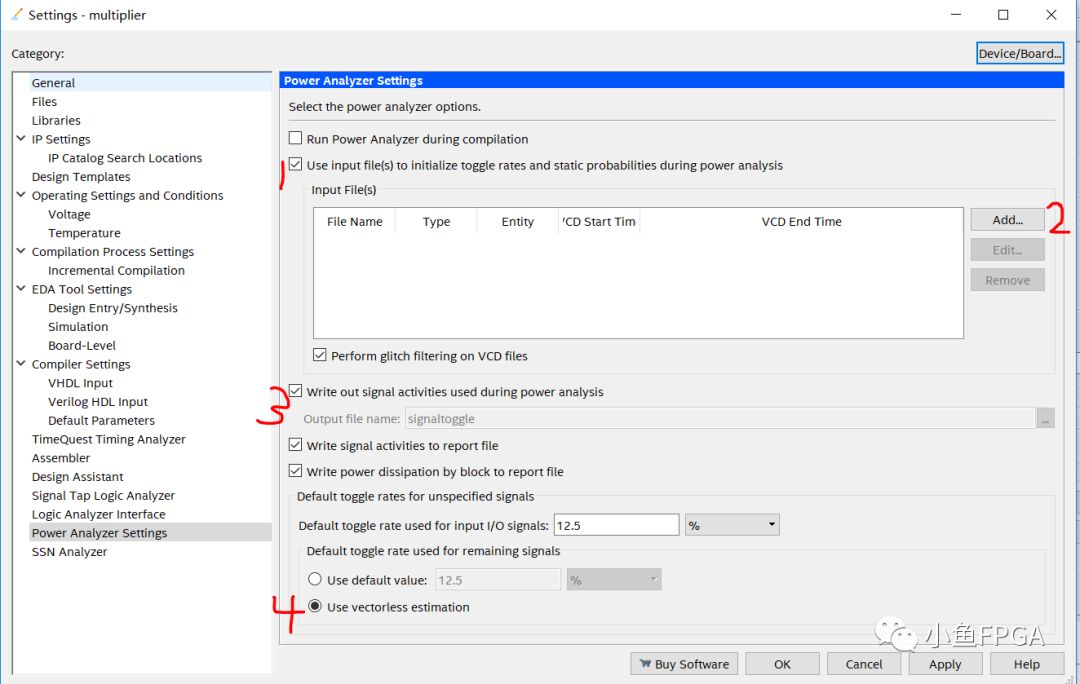

可以直接点击OK。回到界面

对比一下设置,如上。

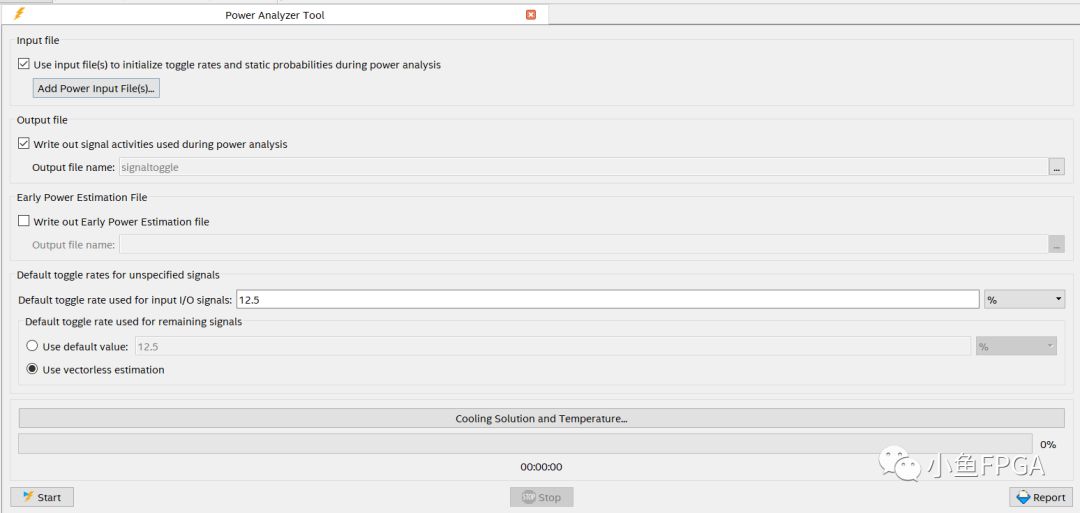

然后点击 Start开始预估操作。完成后,如下图。

此时再点击最右下方的Report按钮。得到报告:

其中你设计的模块的动态功耗是 Core Dynamic Thermal Power Dissipation。

即集成电路里面对应的CMOS的动态功耗。这个功耗跟工艺(即FPGA的器件),工作时钟频率有关。

Core Static Thermal Power Dissipation即FPGA器件的静态功耗,跟所选择的器件型号有关。

具体细节一定要参考官方文档,这样你的理解会更深。

以上是关于Quartus II中Power analyzer tool 的使用(功耗预估)的主要内容,如果未能解决你的问题,请参考以下文章