SLX-FPGA — 高层级FPGA开发工具

Posted 经纬恒润

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了SLX-FPGA — 高层级FPGA开发工具相关的知识,希望对你有一定的参考价值。

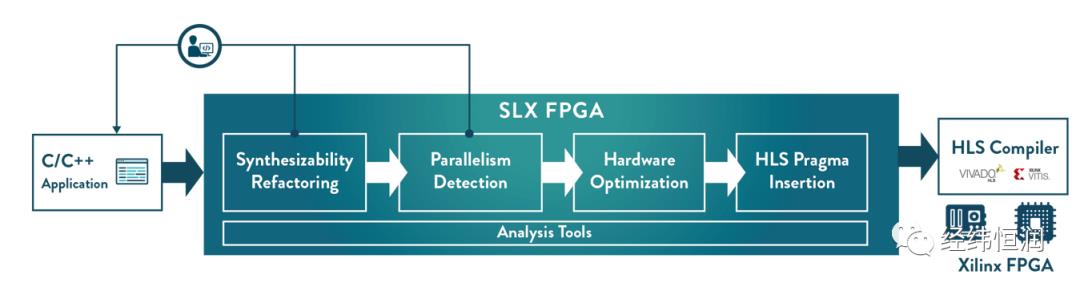

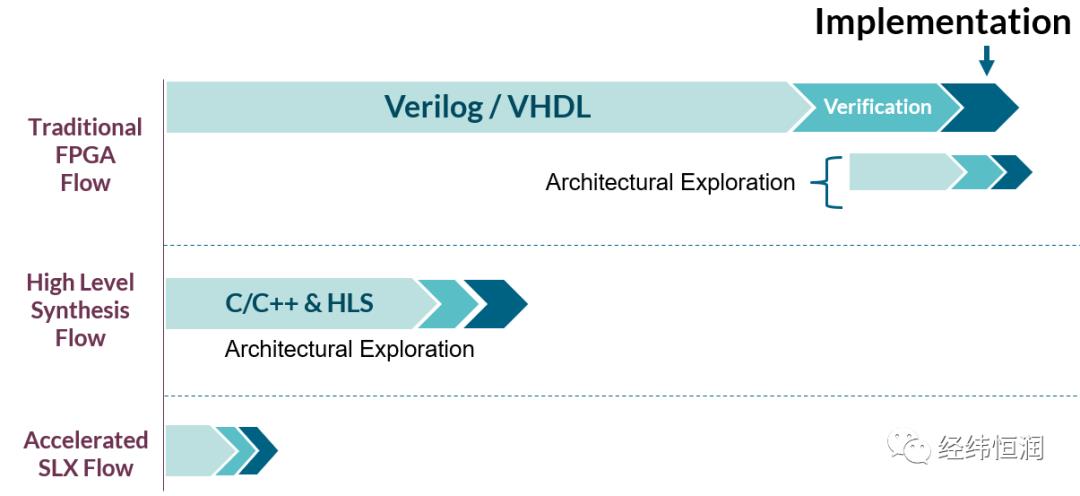

Silexica公司致力于提供缩短创新型软件IP及智能产品研发周期的解决方案。其SLX FPGA工具基于深层次的软件分析,对异构硬件进行充分考虑,从而实现快速的设计空间探索。该工具能够加速软件向专用硬件系统的转化过程,使得算法加速更加普及。

产品介绍

SLX FPGA能够帮助用户更容易、更快、更高效地将C/C++代码转换成RTL代码。

SLX FPGA工具可以解决高层次综合设计流程带来的各种问题,包括处理不可综合或未考虑硬件实现的C/C++代码,检测应用程序并行性,以及自动插入pragma代码,以帮助工程师更好地优化待进行高层次综合的C/C++应用程序。

降低HLS工具使用门槛

开发人员要熟练使用HLS工具,需要阅读上千页的文档,并熟练掌握相关代码规范。

SLX工具能够帮助用户:

快速识别不可综合的代码;

为常见的C库进行自动代码重构;

提供示例来帮助用户实现可综合代码编写。

以上功能有效的降低HLS工具使用门槛,使用户能够方便的通过C/C++进行FPGA的开发。

并行性检测

C/C++代码通常是在标准处理器上顺序执行的。但是在专用硬件中,部分代码模块可以并行地执行,以加速代码的执行效率。

如果只是简单地通过HLS进行代码转换,其设计结果也是顺序执行的硬件,无法有效的利用硬件并行处理的优势。如果要实现硬件层面的并行执行,需要用户根据实际情况进行代码的约束,这对于软件设计工程师而言会是一个很大的挑战。

针对这一挑战,SLX FPGA提供了C/C++代码的分析和检测功能。SLX FPGA工具能够根据代码的分析和检测结果,自动进行代码的并行化约束,让用户轻松实现代码的并行化。

硬件优化

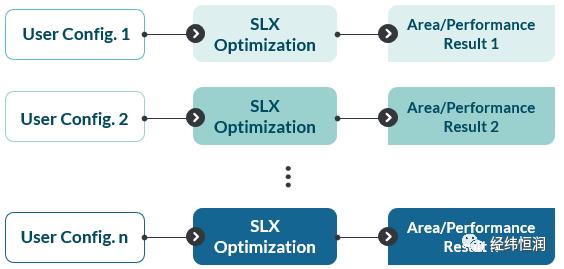

SLX FPGA能够根据用户的相关配置,自动对识别出的可并行函数进行分析,使用Silexica的专有算法确定当前设计优化的最优效果。

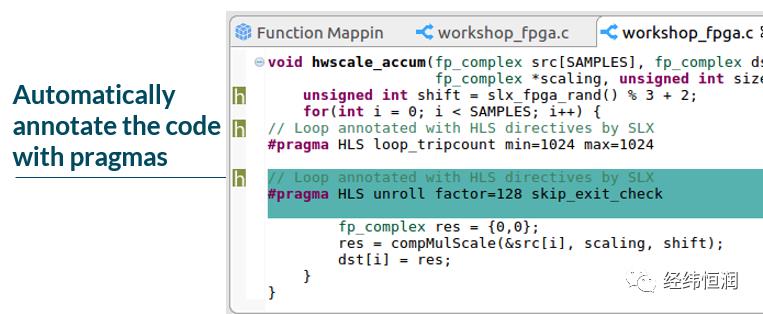

pragma插入

一旦确定了优化的硬件实现,SLX-FPGA将自动插入HLS pragma,以指导HLS编译器对代码的具体硬件实现细节。用户可直接获取优化后代码所生成的IP,将其放入自己的工程中进行使用。

相关链接 (直接点击进入)

|

1 |

|

|

2 |

|

|

3 |

|

|

4 |

|

|

5 |

|

|

6 |

|

经纬恒润通过与IBM、Dassault、ANSYS等全球知名工业软件厂商合作,为用户提供汽车电子领域数十种研发工具,并通过在研发流程、建模仿真、测试验证、平台建设等领域的定制开发和技术服务,助力用户实现研发的流程化、数字化、智能化和平台化,提升产品研发效率和市场竞争力。

THE END

经纬 恒 润

致力于成为国际一流的汽车电子系统科技服务商!

邮箱:market_dept@hirain.com

以上是关于SLX-FPGA — 高层级FPGA开发工具的主要内容,如果未能解决你的问题,请参考以下文章