可靠性案例分享多电源电路的可靠性设计案例

Posted 硬件十万个为什么

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了可靠性案例分享多电源电路的可靠性设计案例相关的知识,希望对你有一定的参考价值。

在通信系统的电路中,大多存在两种以上的电源,实际工程应用中还常有蓄电池提供后备供电的情况,对于这些电路,在电压变化的过程中,可能会引发电路无效复位或上电失败的故障。对此,本文提出了一种实用的解决方案。

图1: FPGA的上电加载机制。

随着通信设备复杂程度的提高,工程应用对设备的可靠性要求也随之提高。各种电源配送方案在工程运用上得到了广泛的应用,在有后备电池供电的应用上,由于供电系统的切换,通信设备内各部件将面临一次上电初始化的考验。

电路上电问题分析

现在通信机房大多采用-48V直流电源,而电子元器件一般采用低电压供电,以5V和3.3V最为常见,近几年随着低功耗器件的大量使用,1.5V、1.8V、2.5V电源也被采用。电路设计中往往采用DC-DC电源转化模块提供二次电源。在同时使用多种电源时,可采用多种电源模块,或采用一种电源模块加多个直流电压转换器的方案,下面就两种典型情况作简单分析。

1.采用多电源模块设计的电路

这种设计一般包括1只48-5V电源模块和1只48-3.3V电源模块。其中5V电源模块主要给电路内5V器件供电;3.3V电源模块主要给电路内FPGA、ASIC供电,以及供给直流电压转换器进行更小电压的转换。这里应当指出,如果采用线性调压器(LDO)进行小电压转换时,上级电压通常采用3.3V,因为常用的1.5V、1.8V、2.5V与5V的压降很大,在进行电压转换的时候将损失更多功率,同时增加系统的散热负担。

对于这种设计,由于不同电源模块的指标差异,存在上电顺序的问题。如果5V达到稳定的时间比3.3V早,那么将可能造成如下问题:

a. 5V器件已经运行正常,而3.3V的FPGA、ASIC还未加载或初始化完毕。如果电路内MCU单元为5V供电,那么MCU初始化FPGA和ASIC失败,电路工作将不正常,这种情况理论上可以通过在MCU程序代码里添加空转等待语句,但是实际上仍然存在问题,见下面的分析。

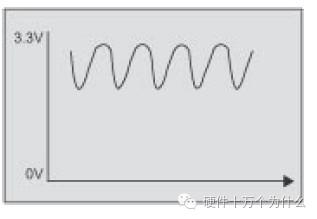

b. FPGA加载失败。图1显示了一般可编程逻辑器件的上电加载机制。图2显示了48-3.3V的某品牌电源模块在用蓄电池加电时,其电压在上升过程中与达到稳定状态前出现的较为严重的波动,测试其他电压,也发现类似情况。

从图1、图2可以分析到,FPGA在上电过程中需要自检电压,一旦所有要求的电压值大于某个范围就开始加载,而此时如果电压波动较大,那么FPGA可能会加载失败,因为当波动的电压处于波峰时FPGA快速检查电压并可能通过,在FPGA加载正进行到下面某一步时,电压值突然下降直至波谷,那么FPGA的后续加载操作将异常。当然,现在不少FPGA在上电自检的时候都有个监测电压是否稳定的过程,加载失败的情况基本上很少,不过大部分的FPGA对电压都有严格的要求。

图2:电源纹波示例。

c.与b类似,很多ASIC专用芯片、CPLD在上电初始化的时候都需要有稳定的电压,这里不再累述,可以参阅相关芯片资料。

2.采用单电源模块设计的电路

目前在系统设计中,为了兼容各种电压也常采用48-5V单电源模块和加直流电压转换器的方案。其实采用单电源模块的设计同样面临上面提到的问题。单电源模块也存在上电顺序先后的问题。因为电源模块直接输出5V,其他电压值通过直流电压转换器转换,因此小于5V的电压上电肯定晚于5V。

在蓄电池供电的情况下,由于蓄电池的本身特性,在上电的时候其电压是缓慢上升的,由于现在DC-DC模块的设计差异,某些模块在慢上电的过程中出现的电压摆动仍然会影响FPGA和ASIC的初始化。

解决方法

对应可能出现的问题,可以找到相应的解决方法。在前文分析的第一种情况(采用多电源模块)下,对应a,可以复位MCU;对应b,可以复位FPGA;对应c,可以复位相关芯片。对于第2种情况(采用单电源模块),复位相应的芯片也可以解决问题。所以最直接有效的方法就是复位。

当然我们不可能等到故障出现的时候再去手动复位,这里可以考虑使用Maxim公司的MAX708芯片来完成自动复位的功能。

MAX708是一种微处理器电源监控芯片,可同时输出高电平有效和低电平有效的复位信号。复位信号可由VCC 电压、手动复位输入或由独立的比较器触发。独立的比较器可用于监视第二个电源信号。在电路设计中,MCU单元一般由51单片机构成,单片机的复位信号是高有效。一般FPGA和ASIC的复位信号都是低有效。由于MAX708可同时输出高电平有效和低电平有效的复位信号,因此可以利用MAX708的这个特点来解决电路内MCU、FPGA、ASIC的上电复位问题。

如图3所示,当PFI端子上的电压值小于1.25V时,PFO端子将输出低电平(平时为高)。由于PFI端子的这个特性,可以用它来监控电路上的1.5V电压。在通信设备里,电路上一般含有5V、3.3V、2.5V、1.8V、1.5V的电压值,1.5V应该属于末级电压,就是说通过直流电压转换器最后转压出来的,我们监控了最小电压(1.5V),自然也就不必理会它的上级电压了。

图3:利用MAX708实现上电复位应用。

这里PFI上的电压值大概为1.3V,当然电压值越接近1.25V,电压监控的灵敏度越高。可以用公式{(Vsupply-VPFI)/R1}=(VPFI/R2)计算出需要的电阻比值。这里Vsupply为1.5V,VPFI为1.3V。

可以想象,电路上电过程中,1.5V的末级电压如果没有达到要求,复位信号将一直存在,包括给MCU的RST复位信号,和给其它芯片的低电平有效的复位信号。图3中的MREST为手动添加的复位信号。

需要指出的是,MAX708本身可以监控VCC电压(这里为5V),这对电路采用多电源模块的设计是很有用的。因为两个电源模块相互独立,5V和1.5V可能不是源于同一个电源模块,所以在监控1.5V的同时也需要监控5V电压。

当然,由于MAX708芯片本身的限制,它无法监控小于1.25V的电压。但是在电信级设备中,功耗问题并不很迫切,所以这样小的电压基本上应用很少。

本文小结

电源波动造成的电路上电失败故障,只是涉及电源可靠性的一个方面。这里举的一个实际应用的例子可能并不适合于各种情况,其目的只是在于提醒设计人员在有关电源设计中可能存在的隐患。

现在,FPGA和ASIC在降低功耗的同时,也具有越来越多的驱动电压,某些器件还特别对各种电压的上电顺序有严格的要求。硬件工程师在应用这些器件进行系统功能设计的同时,也将越来越多的面临如何提高电源可靠性方面的挑战。

加入《可靠性案例分享群》获得更多可靠性资讯。每晚讨论分享案例细节。

硬件十万个为什么,《电路可靠性案例征文》大赛:

主办方:硬件十万个为什么、信号完整性

论文形式:不限

比赛奖品:

一等奖一个4核A9开发板1名

二等奖飞思卡尔M4开发板2名

三等奖STM32F103开发板4名

已发布投稿内容:

前期可靠性类文章:

以上是关于可靠性案例分享多电源电路的可靠性设计案例的主要内容,如果未能解决你的问题,请参考以下文章

PCB电磁兼容设计与案例与硬件电路可靠性设计测试与案例分析培训

硬件电路可靠性设计及其案例分析技术高级研修班--2018年4月19日北京举行

案例分享——低压电力线载波通信模组(借助电源线实现远距离数据传输宽压输入波特率范围广应用场景多样化)