中兴新支点嵌入式操作系统为飞思卡尔硬件方案带来可视化图形界面体验

Posted 中兴新支点操作系统

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了中兴新支点嵌入式操作系统为飞思卡尔硬件方案带来可视化图形界面体验相关的知识,希望对你有一定的参考价值。

飞思卡尔的硬件方案以高度的稳定性和可靠性使其成为诸多国企采用嵌入式系统控制平台的首选硬件方案。很多国企系统的硬件平台都是针对PC8377_RDB而改造的,然而随着嵌入式系统对图形界面的要求越来越强烈,使得很多企业开始提出了可视化图形界面的要求。

为了实现以上需求,飞思卡尔选择了中兴新支点嵌入式操作系统来优化完善该硬件方案。一起来看看他们是如何分工合作,完成这个出色效果的吧。

MPC8377处理器本身是不带图形界面处理器的,因此需要通过外接显卡才能够显示图形界面。MPC8377提供的针对外接显卡的接口只有PCI或PCI-E的接口,本方案采用的是PCI的接口。

一、硬件介绍

CPU:MPC8377

内存:512M

Nor Flash:32M

NAND Flash:1G

显卡:Radeon M6(PCI接口) 64M显存

二、显卡驱动原理

Radeon显卡驱动的工作:显存空间分配和管理、微码加载、CP(命令处理器)驱动&ring buffer管理、pm4包命令封包、CPU与GPU fence同步。

显存分配管理

显存管理主要针对两种内存:PCI空间的内存,这种内存是卡上的内存,存在显卡上;转换表内存,通过动态分配内存页,绑定到转换表,从而使得GPU能够访问内存页。

微码加载

显卡的微码加载分为两个部分:atombios和microcode。Atombios主要做模式设置和GPU最原始的初始化工作,由于CPU中的BIOS做了相应的工作,因此在GPU的驱动中没有加载atombios。Microcode是指命令控制器的微码。

CP&ring buffer

CP是面向图形控制的可编程的专用计算引擎,主要处理环形缓冲器和间接线性缓冲的命令流,对CP而言接受驱动程序的命令流有两种方式:推模式;拉模式。推模式是指驱动程序通过PCI总线直接操作GPU寄存器。

在拉模式下,驱动程序在系统内存中为命令包申请一块缓冲区,GPU会根据这些命令包执行屏幕绘图操作。这种命令缓冲区按照环形方式进行管理,是CPU和GPU共享的一片系统主存,CPU负责写入命令包,GPU负责读取和解析命令包。

PM4命令包

ATI显卡可以运行在PM4模式,在这种模式下,不需要直接向寄存器中写数据执行绘图操作,而是在系统内存中准备PM4格式的命令包,让硬件执行绘图命令。

CPU与GPU的fence同步机制

对于环形缓冲的操作,需要确保CPU和GPU的事件同步,这是通过fence机制来实现的。

三、显卡中BIOS初始化

同其它挂载在PCI总线上的芯片有所不同,显示芯片在上电之后往往需要经过一系列的由程序控制的初始化,才能正常的运行。对于X86平台,这一过程是在上电自检过程中由系统BIOS发现显卡之后去执行显卡BIOS中的代码来完成的,而基于Powerpc的Macintosh系列的桌面系统则是通过Open Firmware来达到相同的目的。而对于本设计的目标系统因为缺少BIOS和Open Firmware的支持,需要直接通过引导程序uboot来完成这一初始化过程。

大多数图形芯片生产厂家对其芯片的初始化过程严格保密,只向用户提供二进制形式的显卡BIOS来执行相关的操作。目标系统中的显卡就在其BIOS中固化了基于X86指令集的二进制初始化代码,从而造成基于Powerpc处理器的目标系统无法直接执行。

为了让PowerPC能够执行显卡中的BIOS固化的程序,采用x86emu来模拟一个X86的模拟器,通过X86的模拟器来执行BIOS固化的代码。

A) X86的模拟器

模拟器主要模拟的是X86的硬件寄存器、X86的操作码(指令集)、以及X86的执行流程(包括寻址、执行指令)。

X86的硬件寄存器是采用结构体X86EMU_sysEnv来实现的,这个结构体将X86的所有的寄存器都模拟了,包括段寄存器、指令寄存器等。

X86的操作码,这个主要是模拟了X86的操作指令,操作指令通过x86emu_optab操作表实现。这个操作表将X86的所有操作指令进行了模拟,使得X86的所有指令能够得到相应的执行,保证了指令的正确执行。

模拟X86的执行流程,X86的真正执行流程的函数是X86EMU_exec。通过这个函数实现X86执行流程的模拟,这个函数还模拟了CPU先执行中断,之后再是取指令执行。

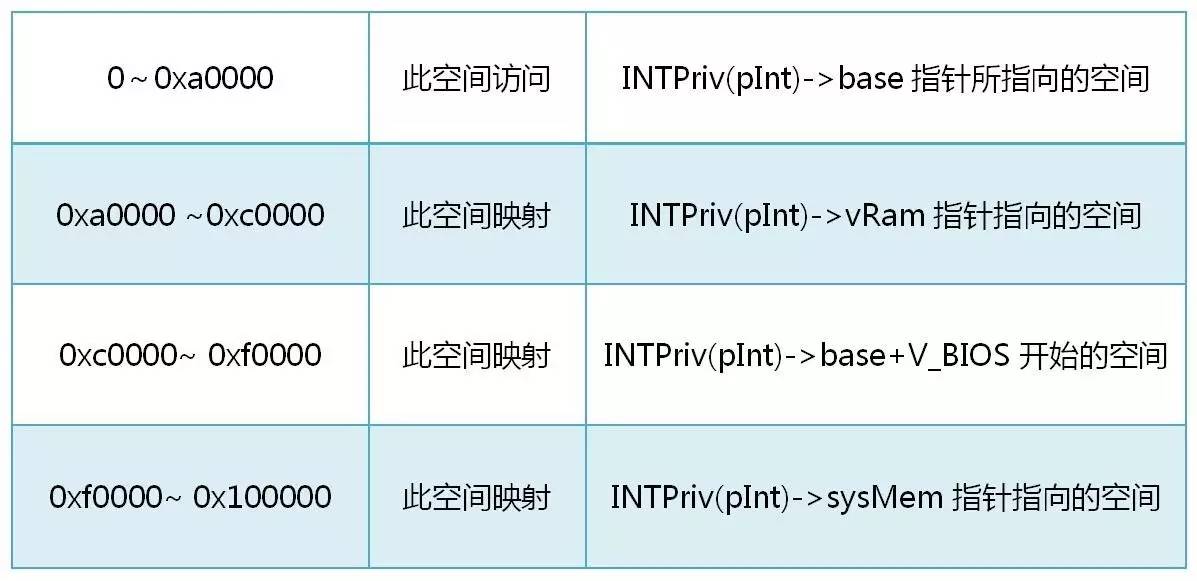

x86emu中寻址空间空间默认是0~100000大小,映射关系如下:

B) 显卡BIOS执行

正如上面提到的显卡的BIOS中初始化代码是放在显卡的ROM空间中的,X86架构的CPU通过主板的BIOS来执行显卡中的BIOS程序,而本方案中则采用的是通过引导程序Uboot来执行显卡中的BIOS程序。

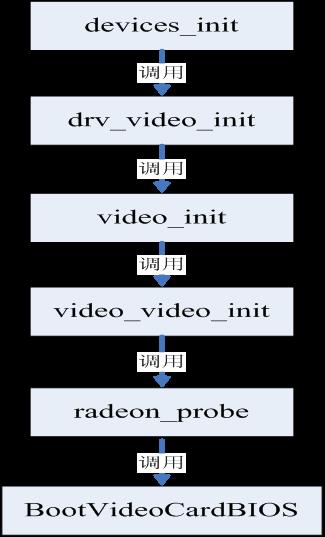

Uboot对显卡BIOS的执行调用流程具体如下:

uboot对显卡初始化调用关系图

BootVideoCardBIOS这个函数会先将显卡中的程序复制到内存中然后通过X86模拟器来执行这段程序。显卡中的BIOS的代码最后被影射到0xc0000~ 0xf0000段。执行BIOS代码的函数是BE_callRealMode(0xC000, 0x0003, ®s, &sregs)。

四、Linux 内核显卡驱动

Uboot对显卡初始化之后,就将显卡交给内核,Linux通过drm进行显卡GPU的驱动。

DRM是直接渲染管理器(Direct Rendering Manager)的简称,给予DRI客户端直接访问硬件的内核模块,实现上面的内存管理。DRM主要实现内存管理、输出管理、frame buffer管理、命令注册、fence同步机制、DMA服务等。

内核中对于显卡相关的结构体介绍:

drm_driver:这个结构体是DRM的驱动,这个结构体主要实现了显卡芯片的驱动和上层应用的接口,上层应用都是通过这个接口最终控制显卡的。这个结构体中有ioctls变量,这个变量定义了所有的用户层操作显卡的ioctl命令,用户层可以通过这个接口来操作显卡。同时这个函数有一个显卡初始化挂钩函数load,驱动程序通过这个挂钩函数最后初始化显卡,这个函数最后会调用radeon_asic结构体中的init函数,从而实现芯片驱动的初始化。

drm_device:这个结构体是代表了一个完整的显卡设备,包含了显卡所有的信息。和drm_driver是相对应的,是设备和驱动之间的关系。

radeon_device:这个结构体代表了radeon系列的显卡,是radeon显卡操作的主要结构体。

radeon_asic:这个radeon系列的芯片驱动程序,这个对应着设备的芯片驱动程序,它抽象了所有radeon芯片的操作,最后通过挂钩函数来实现真正的操作。挂钩函数的第一个参数基本上是一个radeon_device结构体的实例。可以简单的理解为radeon_device何radeon_asic之间的关系为设备和驱动之间的关系。

内核对显卡的初始化(r100_init函数)流程:

GPU启动流程和测试

以上是关于中兴新支点嵌入式操作系统为飞思卡尔硬件方案带来可视化图形界面体验的主要内容,如果未能解决你的问题,请参考以下文章

痞子衡嵌入式:飞思卡尔i.MX RTyyyy系列MCU硬件那些事(2.2)- 在串行NOR Flash XIP调试原理