英特尔第二代10nm处理器架构大改!L2缓存翻5倍,发力移动端

Posted 芯东西

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了英特尔第二代10nm处理器架构大改!L2缓存翻5倍,发力移动端相关的知识,希望对你有一定的参考价值。

芯东西(ID:aichip001)编 | 云鹏

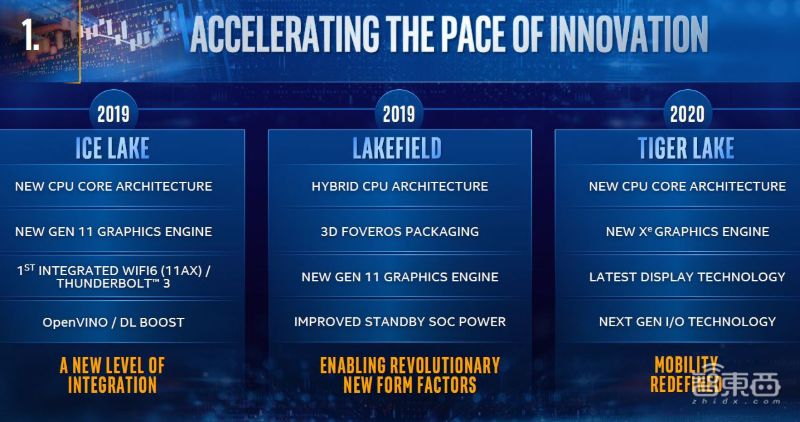

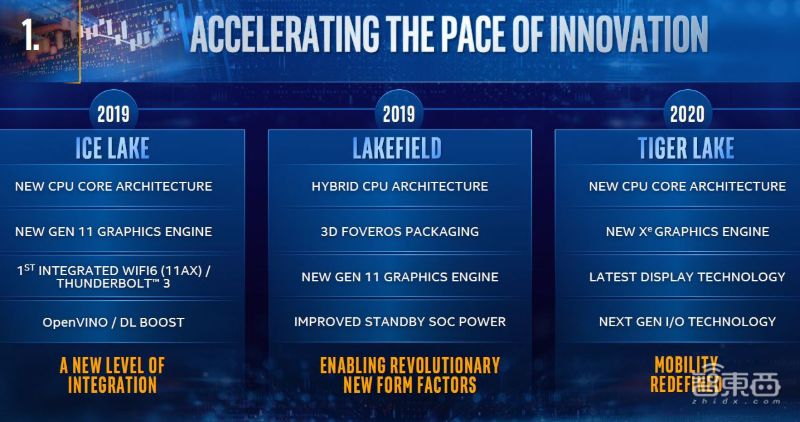

芯东西12月2日消息,据外媒报道,英特尔Tiger Lake处理器架构将对缓存结构进行调整,L2高速缓存增加400%,达到5MB;L3高速缓存大小增加50%,达到12MB;L1指令缓存(Instruction cache)的大小提高到48KB。

Tiger Lake为英特尔第二代10nm处理器,于今年5月推出,预计将主要用于移动端。根据目前英特尔产能情况,Tiger Lake距离完全投产还有一段时间。以下是对Wccftech报道的原文编译。

01

Tiger Lake 优化缓存结构提高移动端CPU效率

英特尔早在发布Skylake架构时就在HEDT系列中重新平衡(rebalance)了CPU的缓存结构。根据Geekbench的说法,即将到来的10nm Tiger Lake移动端CPU可能也会进行类似的缓存重新平衡。

假设英特尔在发布HEDT Skylake-X CPU之前采取了类似的措施,那么英特尔可能会在Tiger Lake上延续这种做法。在处理Skylake-X时,英特尔减少了L3缓存的数量,而增加了低延迟的L2缓存。

不过对于Tiger Lake-Y,英特尔可能会在L1、L2、L3的每个缓存中都进行改进。以前,移动端和桌面端CPU共享相同的缓存结构,但是通过重新设计缓存,英特尔可以提高移动端CPU的效率。

根据Geekbench报告,目前所讨论的系统正在运行的CPU为Tiger-Y-Y ,具有四个内核和八个线程。该CPU的缓存有明显调整,每个内核具有1.25MB的大型L2缓存,从而使L2缓存总数达到了5MB。L2高速缓存的数量比之前提高了400%。随着L2高速缓存的显着增加,L3高速缓存大小增加50%,达到12MB。

英特尔将L1指令缓存的大小提高到48KB,L1数据缓存(Data cache)保持在32KB。测试的CPU样本可以克服现有Skylake-X CPU所需的权衡(trade-off);L2高速缓存的增加并不以L3高速缓存的减少为代价,因此整体性能得以提高。

Tiger Lake有望做出的其他改进包括引入PCIe 4.0(该功能目前仅适用于AMD的X570和TRX40平台)以及拥有多达96个EU的Xe核显。

02

Tiger Lake全面投产还有距离

预计Tiger Lake CPU系列将在2020年至2021年的某个时间投放市场,不过10nm制程在全面生产(full-scale production)之前着实还有一段路要走,并不轻松。

Tiger Lake将成为Intel第一代10nm Ice Lake的继任者,并将作为英特尔第三代10nm处理器(10nm++)过程架构优化模型(Process-Architecture-Optimization model)中的一个优化过度版本。

03

结语:英特尔发力移动端CPU架构寻找突破

CPU的缓存,尤其是L1、L2缓存,它的大小及速率都会影响CPU与其他硬件之间的数据传输。此次英特尔显著改善L2缓存,将会对明年到来的Tiger Lake架构处理器性能有一定提升。

在消费级PC市场,英特尔受到AMD空前的压力,从入门级到HEDT平台,性能上被全线碾压,只能通过降价提高性价比,增加竞争力。而一直制霸的数据中心处理器领域也遭到新入场者的频频挑战。

对于英特尔来说,移动端处理器是发力的另一个方向,但也要做好充分准备,因为这条赛道上更有如苹果、高通、华为、联发科等劲敌在等候,英特尔的前路依旧艰难。

以上是关于英特尔第二代10nm处理器架构大改!L2缓存翻5倍,发力移动端的主要内容,如果未能解决你的问题,请参考以下文章

英特尔12代酷睿架构,十二代酷睿架构

第二代智能 英特尔®酷睿™ i7

Atom升级Tremont架构 或采用10nm工艺

AMD展示64核EYPC处理器性能:比Intel至强8280快一倍以上

[转帖]Intel新一代Xeon完整曝光

处理器第二代酷睿i72600和至强x3430哪个好?