综述适用于聚类算法的2-D处理器阵列体系结构研究概述

Posted 芯青年mp

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了综述适用于聚类算法的2-D处理器阵列体系结构研究概述相关的知识,希望对你有一定的参考价值。

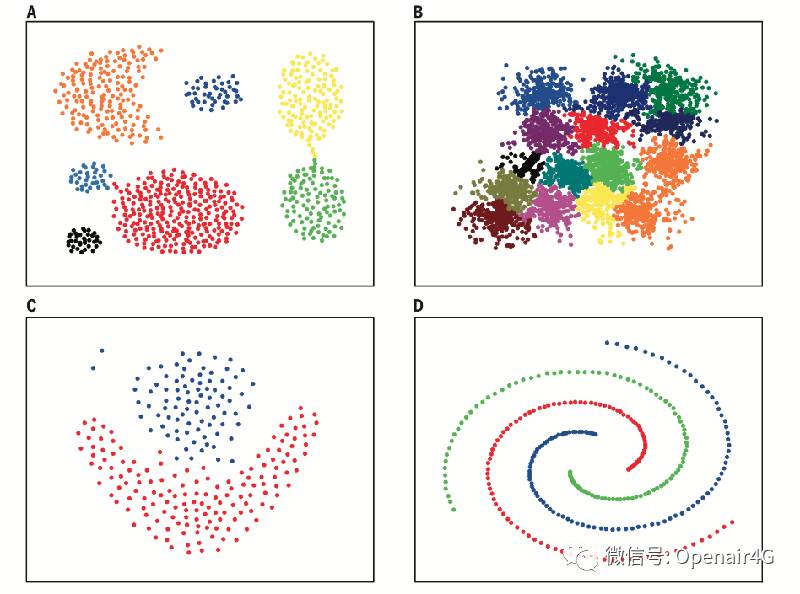

聚类就是按照某个特定标准(如距离准则)把一个数据集分割成不同的类或簇,使得同一个簇内的数据对象的相似性尽可能大,同时不在同一个簇中的数据对象的差异性也尽可能地大。即聚类后同一类的数据尽可能聚集到一起,不同数据尽量分离。

聚类技术的蓬勃发展,得益于包括数据挖掘、统计学、机器学习、空间数据库技术、生物学以及市场营销等的广泛应用。各种聚类方法也被不断提出和改进,而不同的方法适合于不同类型的数据,因此对各种聚类方法、聚类效果的比较成为值得研究的课题。

常用的聚类算法包括k-means聚类算法、凝聚型层次聚类算法、神经网络聚类算法之SOM以及模糊聚类的FCM算法。然而聚类算法本身并不在本篇综述的讨论范围之内,这篇综述只讨论适用于聚类算法的处理器架构的研究现状。特别是随着集成电路技术的发展,对于机器学习等计算密集型内核算法来说,用专用硬件实现成为了可能。

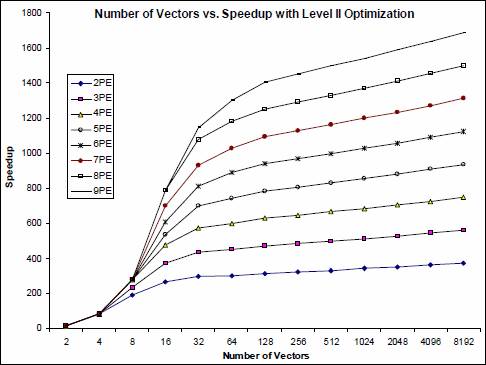

No.1 《Parallel Computation of Similarity Measures Using an FPGA-Based Processor Array》

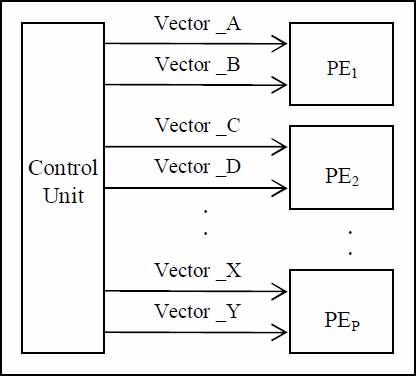

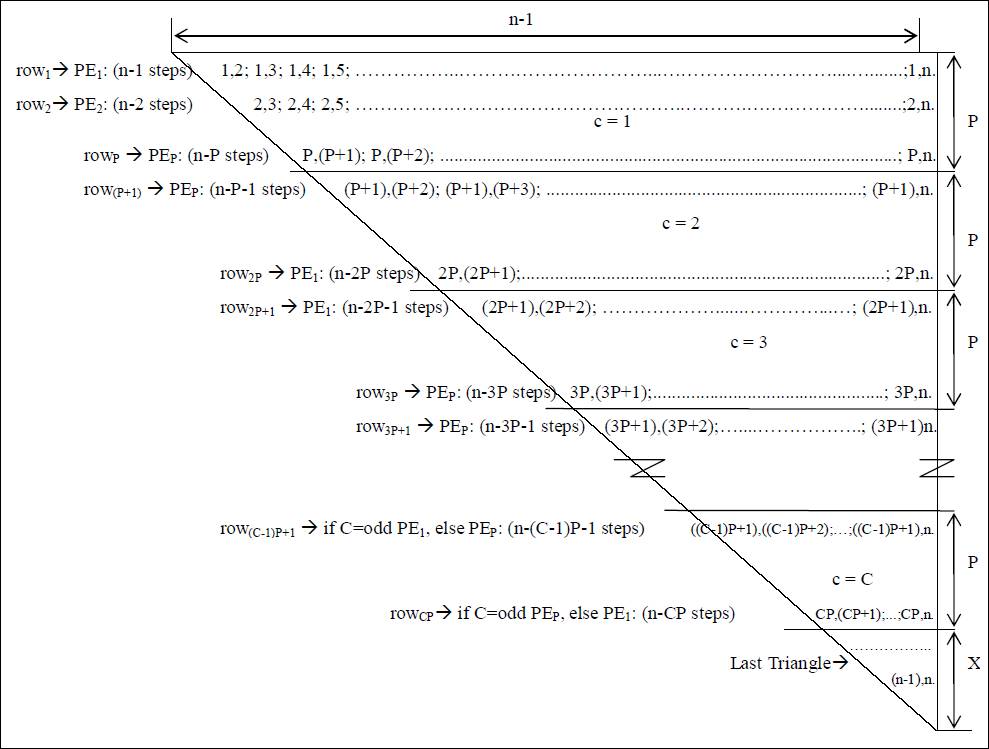

这篇论文专注于基于FPGA的处理器阵列的设计,用于计算相似度矩阵,这是一种常用的数据结构,用于表示一组特征向量之间的相似性,每个矩阵元素表示计算的两个相似度度量向量,同时文中开发了一种将计算有效地分配给处理元件阵列的算法。

(处理器阵列架构)

(处理子任务调度算法)

(性能对比)

No.2 《VLSI design of clustering analyser using systolic arrays》

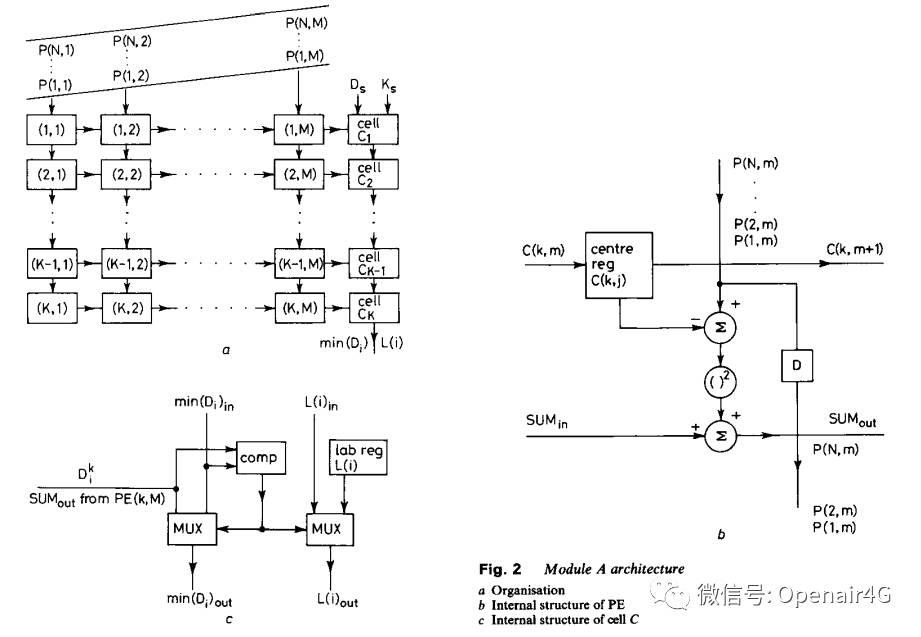

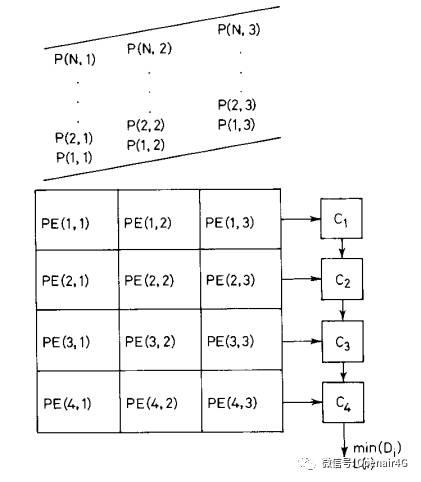

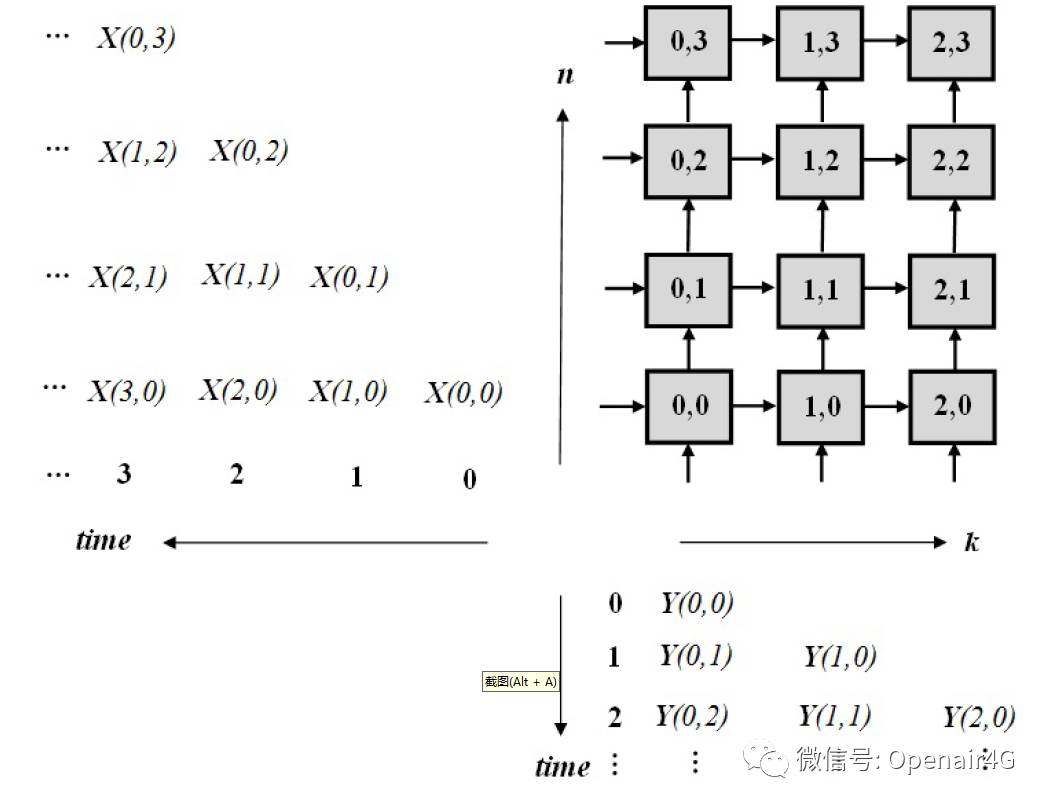

所提出的VLSI架构利用二维收缩阵列,其使用高度并行和流水线处理。 该架构大大减少了以前架构所需的大量处理元件。 此外,相同的架构可以用于具有可变数量的输入模式的应用。 此外,与以前的架构不同,这些模式以串行格式应用于输入,这可以节省大量引脚数,因此,所提出的架构对VLSI实现非常有吸引力。 使用所提出的架构,聚类分析仪的VLSI电路的复杂度可以大大降低。

(2-D处理器阵列架构)

(具体实现示例:3x4)

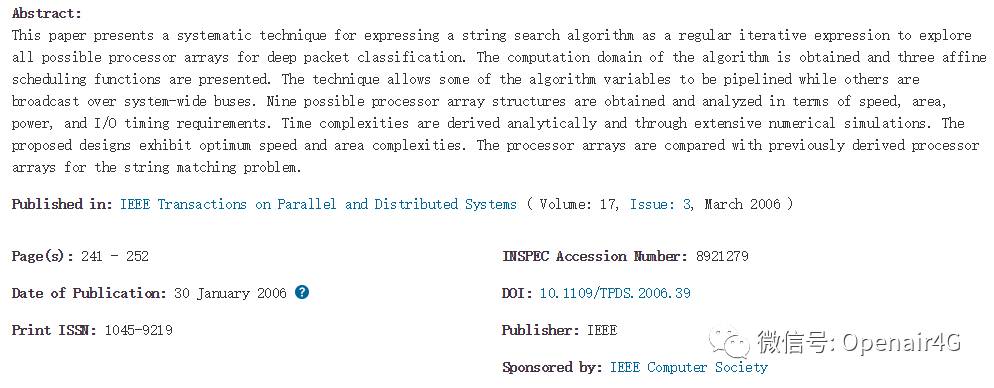

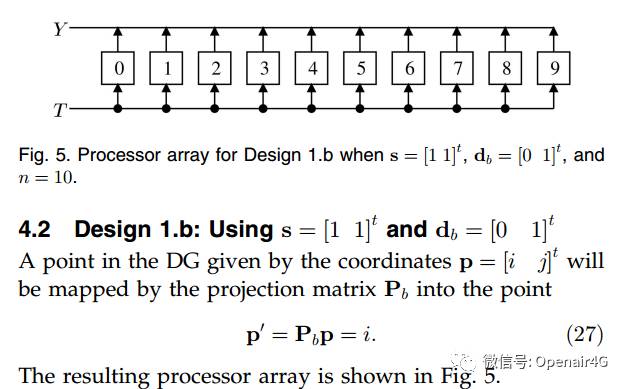

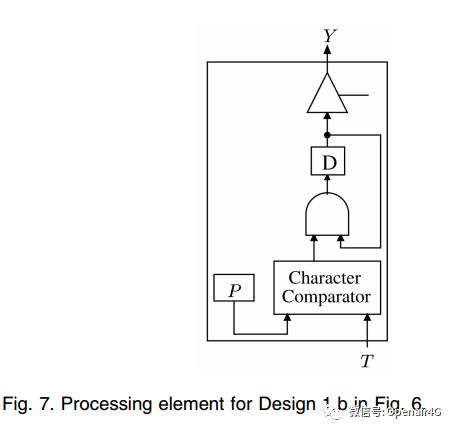

No.3 《Processor array architectures for deep packet classification》

这篇文章提出了一种将字符串搜索算法表示为常规迭代表达式的算法,用以对处理器阵列的体系结构进行设计空间探索。 通过获得算法的计算域,并给出三个仿射调度函数,允许一些算法变量进行流水线操作,而其他算法变量则在系统总线上广播。文章在速度,面积,功率和I/O时序要求方面进行设计空间探索,可以获得并分析九种可能的处理器阵列结构。

(处理器架构)

(PE设计)

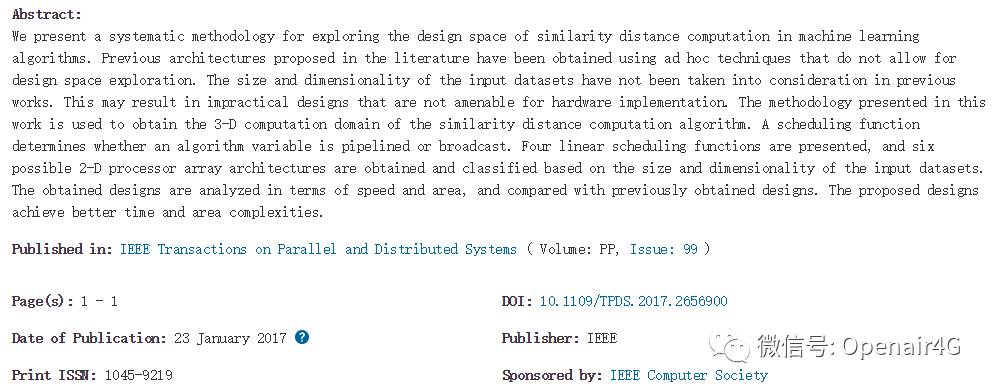

No.4 《Design Space Exploration of 2-D Processor Array Architectures for Similarity Distance Computation》

本文提出了一种系统的方法来探索机器学习中相似距离计算的设计空间算法。以前的作品没有考虑到输入数据集的大小和维度,这个可能导致不适合硬件实现的不切实际的设计。使用本工作中提出的方法获得相似距离计算算法的3-D计算域。调度功能确定是否算法变量是流水线或广播的。提出了四种线性调度功能,以及六种可能的2-D处理器阵列基于输入数据集的大小和维度获得和分类结构。

(处理器架构)

(PE设计)

本篇文章只是引导性地给出了4篇处理器阵列架构设计,感兴趣的朋友可以在IEEE上面搜索相关文献进行研究。

推荐阅读:

以上是关于综述适用于聚类算法的2-D处理器阵列体系结构研究概述的主要内容,如果未能解决你的问题,请参考以下文章