013 PCIe体系结构的组成部件

Posted linfordxu

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了013 PCIe体系结构的组成部件相关的知识,希望对你有一定的参考价值。

一、PCIe体系结构的组成部件

PCIe总线作为处理器系统的局部总线,其作用与PCI总线类似,主要目的是为了连接处理器系统中的外部设备,当然PCIe总线也可以连接其他处理器系统。在不同的处理器系统中,PCIe体系结构的实现方法略有不同。但是在大多数处理器系统中,都使用了RC、Switch和PCIe-to-PCI桥这些基本模块连接PCIe和PCI设备。在PCIe总线中,基于PCIe总线的设备,也被称为EP(Endpoint)。

1、基于PCIe架构的处理器系统

在不同的处理器系统中,PCIe体系结构的实现方式不尽相同。PCIe体系结构以Intel的x86处理器为蓝本实现,已被深深地烙下x86处理器的印记。在PCIe总线规范中,有许多内容是x86处理器独有的,也仅在x86处理器的Chipset中存在。在PCIe总线规范中,一些最新的功能也在Intel的Chipset中率先实现。本节将以一个虚拟的处理器系统A和PowerPC处理器为例简要介绍RC的实现,并简单归纳RC的通用实现机制。

1.1、处理器系统A

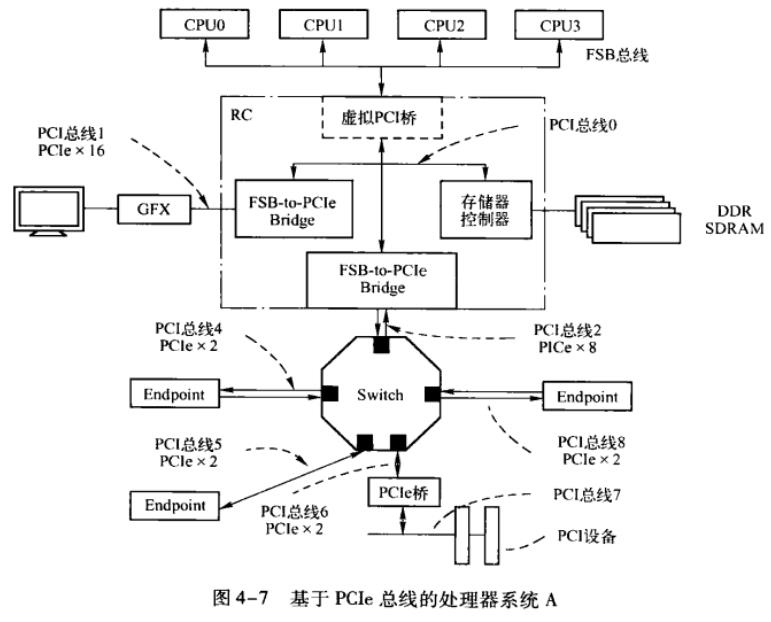

在有些处理器系统中,没有直接提供PCI总线,此时需要使用PCIe桥,将PCIe链路转换为PCI总线之后,才能连接PCI设备。在PCIe体系结构中,也存在PCI总线号的概念,其编号方式与PCI总线兼容。一个基于PCIe架构的处理器系统A如图所示。

在上图的结构中,处理器系统首先使用一个虚拟的PCI桥分离处理器系统的存储器域与PCI总线域。FSB总线下的所有外部设备都属于PCI总线域。与这个虚拟PCI桥直接相连的总线为PCI总线0。这种架构与Intel的x86处理器系统较为类似。

在这种结构中,RC由两个FSB-to-PCIe桥和存储器控制器组成。值得注意的是在图4 7中,虚拟PCI桥的作用只是分离存储器域与PCI总线域,但是并不会改变信号的电气特性。RC与处理器通过FSB连接,而从电气特性上看,PCI总线0与FSB兼容,因此在PCI总线0上挂接的是FSB-to-PCIe桥,而不是PCI-to-PCIe桥。

在PCI总线0上有一个存储器控制器和两个FSB-to-PCIe桥。这两个FSB-to-PCIe桥分别推出一个×16和×8的PCIe链路,其中×16的PCIe链路连接显卡控制器(GFX),其编号为PCI总线1;×8的PCIe链路连接一个Switch进行PCIe链路扩展。而存储器控制器作为PCI总线0的一个Agent设备,连接DDR插槽或者颗粒。

此外在这个PCI总线上还可能连接了一些使用“PCI配置空间”管理的设备,这些设备的访问方法与PCI总线兼容,在x86处理器的Chipset中集成了一些内嵌的设备。这些内嵌的设备使用均使用“PCI配置空间”进行管理,包括存储器控制器。

PCIe总线使用端到端的连接方式,因此只有使用Switch才能对PCIe链路进行扩展,而每扩展一条PCIe链路将产生一个新的PCI总线号。如图4 7所示,Switch可以将1个×8的PCIe端口扩展为4个×2的PCIe端口,其中每一个PCIe端口都可以挂接EP。除此之外PCIe总线还可以使用PCIe桥,将PCIe总线转换为PCI总线或者PCI-X总线,之后挂接PCI/PCI-X设备。多数x86处理器系统使用这种结构连接PCIe或者PCI设备。

在PCIe总线规范中并没有明确提及PCIe主桥,而使用RC概括除了处理器之外的所有与PCIe总线相关的内容。在PCIe体系结构中,RC是一个很模糊也很混乱的概念。Intel使用PCI总线的概念管理所有外部设备,包括与这些外部设备相关的寄存器,因此在RC中包含一些实际上与PCIe总线无关的寄存器。使用这种方式有利于系统软件使用相同的平台管理所有外部设备,也利于平台软件的一致性,但是仍有其不足之处。

1.2、PowerPC处理器

PowerPC处理器挂接外部设备使用的拓扑结构与x86处理器不同。在PowerPC处理器中,虽然也含有PCI/PCIe总线,但是仍然有许多外部设备并不是连接在PCI总线上的。在PowerPC处理器中,PCI/PCIe总线并没有在x86处理器中的地位。在PowerPC处理器中,还含有许多内部设备,如TSEC(Three Speed Ethenet Controller)和一些内部集成的快速设备,与SoC平台总线直接相连,而不与PCI/PCIe总线相连。在PowerPC处理器中,PCI/PCIe总线控制器连接在SoC平台总线的下方。

Freescale即将发布的P4080处理器,采用的互连结构与之前的PowerPC处理器有较大的不同。P4080处理器是Freescale第一颗基于E500 mc内核的处理器。E500 mc内核与之前的E500 V2和V1相比,从指令流水线结构、内存管理和中断处理上说并没有本质的不同。E500mc内核内置了一个128KB大小的L2 Cache,该Cache连接在BSB总线上;而E500 V1/V2内核中并不含有L2 Cache,而仅含有L1 Cache而且与FSB直接相连。在E500mc内核中,还引入了虚拟化的概念。在P4080处理器中,一些快速外部设备,如DDR控制器、以太网控制器和PCI/PCIe总线接口控制器也是直接或者间接地连接到CoreNet中,在P4080处理器,L3 Cache也是连接到CoreNet中。P4080处理器的拓扑结构如图4 8所示。

目前Freescale并没有公开P4080处理器的L1、L2和L3 Cache如何进行Cache共享一致性。多数采用CoreNet架构互连的处理器系统使用目录表法进行Cache共享一致性,如Intel的Nehelem EX处理器。P4080处理器并不是一个追求峰值运算的SMP处理器系统,而针对Data Plane的应用,因此P4080处理器可能并没有使用基于目录表的Cache一致性协议。在基于全互连网络的处理器系统中如果使用“类总线监听法”进行Cache共享一致性,将不利于多个CPU共享同一个存储器系统,在Cache一致性的处理过程中容易形成瓶颈。

如图4 8所示,P4080处理器的设计重点并不是E500mc内核,而是CoreNet。CoreNet内部由全互连网络组成,其中任意两个端口间的通信并不会影响其他端口间的通信。与MPC8548处理器相同,P4080处理器也使用OceaN[1]结构连接PCIe与RapidIO接口。

在P4080处理器中不存在RC的概念,而仅存在PCIe总线控制器,当然也可以认为在P4080处理器中,PCIe总线控制器即为RC。P4080处理器内部含有3个PCIe总线控制器,如果该处理器需要连接更多的PCIe设备时,需要使用Switch扩展PCIe链路。

在P4080处理器中,所有外部设备与处理器内核都连接在CoreNet中,而不使用传统的SoC平台总线[2]进行连接,从而在有效提高了处理器与外部设备间通信带宽的同时,极大降低了访问延时。此外P4080处理器系统使用PAMU(Peripheral Access Management Unit)分隔外设地址空间与CoreNet地址空间。在这种结构下,10GE/1GE接口使用的地址空间与PCI总线空间独立。

P4080处理器使用的PAMU是对MPC8548处理器ATMU的进一步升级。使用这种结构时,外部设备使用的地址空间、PCI总线域地址空间和存储器域地址空间的划分更加明晰。在P4080处理器中,存储器控制器和存储器都属于一个地址空间,即存储器域地址空间。此外这种结构还使用OCeaN连接SRIO和PCIe总线控制器,使得在OCeaN中的PCIe端口之间可以直接通信,而不需要通过CoreNet,从而减轻了CoreNet的负载。

从内核互连和外部设备互连的结构上看,这种结构具有较大的优势。但是采用这种结构需要使用占用芯片更多的资源,CoreNet的设计也十分复杂。而最具挑战的问题是,在这种结构之下,Cache共享一致性模型的设计与实现。在Boxboro EX处理器系统中,可以使用QPI将多个处理器系统进行点到点连接,也可以组成一个全互连的处理器系统。这种结构与P4080处理器使用的结构类似,但是Boxboro EX处理器系统包含的CPU更多。

1.3、基于PCIe总线的通用处理器结构

在不同的处理器系统中,RC的实现有较大差异。PCIe总线规范并没有规定RC的实现细则。在有些处理器系统中,RC相当于PCIe主桥,也有的处理器系统也将PCIe主桥称为PCIe总线控制器。而在x86处理器系统中,RC除了包含PCIe总线控制器之外,还包含一些其他组成部件,因此RC并不等同于PCIe总线控制器。

如果一个RC中可以提供多个PCIe端口,这种RC也被称为多端口RC。如MPC8572处理器的RC可以直接提供3条PCIe链路,因此可以直接连接3个EP。如果MPC8572处理器需要连接更多EP时,需要使用Switch进行链路扩展。

而在x86处理器系统中,RC并不是存在于一个芯片中,如在Montevina平台中,RC由MCH和ICH两个芯片组成。本节并不对x86和PowerPC处理器使用的PCIe总线结构做进一步讨论,而只介绍这两种结构的相同之处。一个通用的,基于PCIe总线的处理器系统如图4 9所示。

上图所示的结构将PCIe总线端口、存储器控制器等一系列与外部设备有关的接口都集成在一起,并统称为RC。RC具有一个或者多个PCIe端口,可以连接各类PCIe设备。PCIe设备包括EP(如网卡、显卡等设备)、Switch和PCIe桥。PCIe总线采用端到端的连接方式,每一个PCIe端口只能连接一个EP,当然PCIe端口也可以连接Switch进行链路扩展。通过Switch扩展出的PCIe链路可以继续挂接EP或者其他Switch。

2、RC的组成结构

RC是PCIe体系结构的一个重要组成部件,也是一个较为混乱的概念。RC的提出与x86处理器系统密切相关。事实上,只有x86处理器才存在PCIe总线规范定义的“标准RC”,而在多数处理器系统,并不含有在PCIe总线规范中涉及的,与RC相关的全部概念。

不同处理器系统的RC设计并不相同,在图4 7中的处理器系统中,RC包括存储器控制器、两个FSB-to-PCIe桥。而在图4 8中的PowerPC处理器系统中,RC的概念并不明晰。在 PowerPC处理器中并不存在真正意义上的RC,而仅包含PCIe总线控制器。

在x86处理器系统中,RC内部集成了一些PCI设备、RCRB(RC Register Block)和Event Collector等组成部件。其中RCRB由一系列“管理存储器系统”的寄存器组成,而仅存在于x86处理器中;而Event Collector用来处理来自PCIe设备的错误消息报文和PME消息报文。RCRB寄存器组属于PCI总线域地址空间,x86处理器访问RCRB的方法与访问PCI设备的配置寄存器相同。在有些x86处理器系统中,RCRB在PCI总线0的设备0中。

RCRB是x86处理器所独有的,PowerPC处理器也含有一组“管理存储器系统”的寄存器,这组寄存器与RCRB所实现的功能类似。但是在PowerPC处理器中,该组寄存器以CCSRBAR寄存器为基地址,处理器采用存储器映像方式访问这组寄存器。

如果将RC中的RCRB、内置的PCI设备和Event Collector去除,该RC的主要功能与PCI总线中的HOST主桥类似,其主要作用是完成存储器域到PCI总线域的地址转换。但是随着虚拟化技术的引入,尤其是引入MR-IOV技术之后,RC的实现变得异常复杂。

但是RC与HOST主桥并不相同,RC除了完成地址空间的转换之外,还需要完成物理信号的转换。在PowerPC处理器的RC中,来自OCeaN或者FSB的信号协议与PCIe总线信号使用的电气特性并不兼容,使用的总线事务也并不相同,因此必须进行信号协议和总线事务的转换。

在P4080处理器中,RC的下游端口可以挂接Switch扩展更多的PCIe端口,也可以只挂接一个EP。在P4080处理器的RC中,设置了一组Inbound和Outbound寄存器组,用于存储器域与PCI总线域之间地址空间的转换;而P4080处理器的RC还可以使用Outbound寄存器组将PCI设备的配置空间直接映射到存储器域中。PowerPC处理器在处理PCI/PCIe接口时,都使用这组Inbound和Outbound寄存器组。

在P4080处理器中,RC可以使用PEX_CONFIG_ADDR与PEX_CONFIG_DATA寄存器对 EP进行配置读写,这两个寄存器与MPC8548处理器HOST主桥的PCI_CONFIG_ADDR和PCI_CONFIG_DATA寄存器类似,本章不再详细介绍这组寄存器。而x86处理器的RC设计与PowerPC处理器有较大的不同,实际上和大多数处理器系统都不相同。x86处理器赋予了RC新的含义,PCIe总线规范中涉及的RC也以x86处理器为例进行说明,而且一些在PCIe总线规范中出现的最新功能也在Intel的x86处理器系统中率先实现。在x86处理器系统中的RC实现也比其他处理器系统复杂得多。深入理解x86处理器系统的RC对于理解PCIe体系结构非常重要。

3、Switch

本篇在上一节中简单介绍了在PCIe总线中,如何使用Switch进行链路扩展,本节主要介绍Switch的内部结构。从系统软件的角度上看,每一个PCIe链路都占用一个PCI总线号,但是一条PCIe链路只能连接一个PCI设备,Switch、EP或者PCIe桥片。PCIe总线使用端到端的连接方式,一条PCIe链路只能连接一个设备。

一个PCIe链路需要挂接多个EP时,需要使用Switch进行链路扩展。一个标准Switch具有一个上游端口和多个下游端口。上游端口与RC或者其他Switch的下游端口相连,而下游端口可以与EP、PCIe-to-PCI-X/PCI桥或者下游Switch的上游端口相连。

PCIe总线规范还支持一种特殊的连接方式,即Crosslink连接方式。使用这种方式时,Switch的下游端口可以与其他Switch的下游端口直接连接,上游端口也可以其他Switch的上游端口直接连接。在PCIe总线规范中,Crosslink连接方式是可选的,并不要求PCIe设备一定支持这种连接方式。

在PCIe体系结构中,Switch的设计难度仅次于RC,Switch也是PCIe体系结构的核心所在。而从系统软件的角度上看,Switch内部由多个PCI-to-PCI桥组成,其中每一个上游和下游端口都对应一个虚拟PCI桥。在一个Switch中有多个端口,在其内部就有多少个虚拟PCI桥,就有多少个PCI桥配置空间。值得注意的是,在Switch内部还具有一条虚拟的PCI总线,用于连接各个虚拟PCI桥,系统软件在初始化Switch时,需要为这条虚拟PCI总线编号。Switch的组成结构如图4 10所示。

Switch需要处理PCIe总线传输过程中的QoS问题。PCIe总线的QoS要求PCIe总线区别对待优先权不同的数据报文,而且无论PCIe总线的某一个链路多么拥塞,优先级高的报文,如等时报文(Isochronous Packet)都可以获得额定的数据带宽。而且PCIe总线需要保证优先级较高的报文优先到达。PCIe总线采用虚拟多通路VC技术,并在这些数据报文设定一个TC(Traffic Class)标签,该标签由3位组成,将数据报文根据优先权分为8类,这8类数据报文可以根据需要选择不同的VC进行传递。

在PCIe总线中,每一条数据链路上最多可以支持8个独立的VC。每个VC可以设置独立的缓冲,用来接收和发送数据报文。在PCIe体系结构中,TC和VC紧密相连,TC与VC之间的关系是“多对一”。

TC可以由软件设置,系统软件可以选择某类TC由哪个VC进行传递。其中一个VC可以传递TC不相同的数据报文,而TC相同的数据报文在指定一个VC传递之后,不能再使用其他VC。在许多处理器系统中,Switch和RC仅支持一个VC,而x86处理器系统和PLX的Switch中可以支持两个VC。

下文将以一个简单的例子说明如何使用TC标签和多个VC,以保证数据传送的服务质量。我们将PCIe总线的端到端数据传递过程模拟为使用汽车将一批货物从A点运送到B点。如果我们不考虑服务质量,可以采用一辆汽车运送所有这些货物,经过多次往返就可以将所有货物从A点运到B点。但是这样做会耽误一些需要在指定时间内到达B点的货物。有些货物,如一些急救物资、EMS等其他优先级别较高的货物,必须要及时地从A点运送到B点。这些急救物资的运送应该有别于其他普通物资的运送。

为此我们首先将不同种类的货物进行分类,将急救物资定义为TC3类货物,EMS定义为TC2类货物,平信定义为TC1类货物,一般包裹定义为TC0类货物,我们最多可以提供8种TC类标签进行货物分类。

之后我们使用8辆汽车,分别是VC0~7运送这些货物,其中VC7的速度最快,而VC0的速度最慢。当发生堵车事件时,VC7优先行驶,VC0最后行驶。然后我们使用VC3运送急救物资,VC2运送EMS,VC1运送平信,VC0运送包裹,当然使用VC0同时运送平信和包裹也是可以的,但是平信或者包裹不能使用一种以上的汽车运送,如平信如果使用了VC1运输,就不能使用VC0。因为TC与VC的对应关系是“多对一”的关系。

采用这种分类运输的方法,我们可以做到在A点到B点带宽有限的情况下,仍然可以保证急救物资和EMS可以及时到达B点,从而提高了服务质量。

PCIe总线除了解决数据传送的QoS问题之外,还进一步考虑如何在链路传递过程中,使用流量控制机制防止拥塞。在PCIe体系结构中,Switch处于核心地位。PCIe总线使用Switch进行链路扩展,在Switch中,每一个端口对应一个虚拟PCI桥。深入理解PCI桥是理解Switch软件组成结构的基础。目前PCIe总线提出了MRA-Switch的概念,这种Switch与传统Switch有较大的区别。

4、VC和端口仲裁

在Switch中存在多个端口,其中来自不同Ingress端口的报文可以发向同一个Egress端口,因此Switch必须要解决端口仲裁和路由选径的问题。所谓端口仲裁指来自不同Ingress端口的报文到达同一个Egress端口的报文通过顺序,端口仲裁机制如图4 11所示。

在一个Switch中设有仲裁器,该仲裁器规定了数据报文通过Switch的规则。在PCIe总线中存在两种仲裁机制,分别是基于VC和基于端口的仲裁机制。端口仲裁机制主要针对RC和Switch,当多个Ingress端口需要向同一个Egress端口发送数据报文时需要进行端口仲裁。具体地讲,在PCIe体系结构中有三个端口,需要进行端口仲裁。

• Switch的Egress端口。当EP A和EP B同时访问EP C,D或者DDR-SDRAM时,需要通过Switch的Egress端口C。此时Switch需要进行端口仲裁确定是EP A的数据报文还是EP B的数据报文优先通过Egress端口C。

• 多端口RC的Egress端口。当RC的端口1和端口3同时访问Endpoint C时,RC的端口2需要进行端口仲裁,决定来自RC哪个端口的数据可以率先通过。

• RC通往主存储器的端口。当RC的端口1、端口2和端口3同时访问DDR控制器时,这些数据报文将通过RC的Egress端口4,此时需要进行端口仲裁。

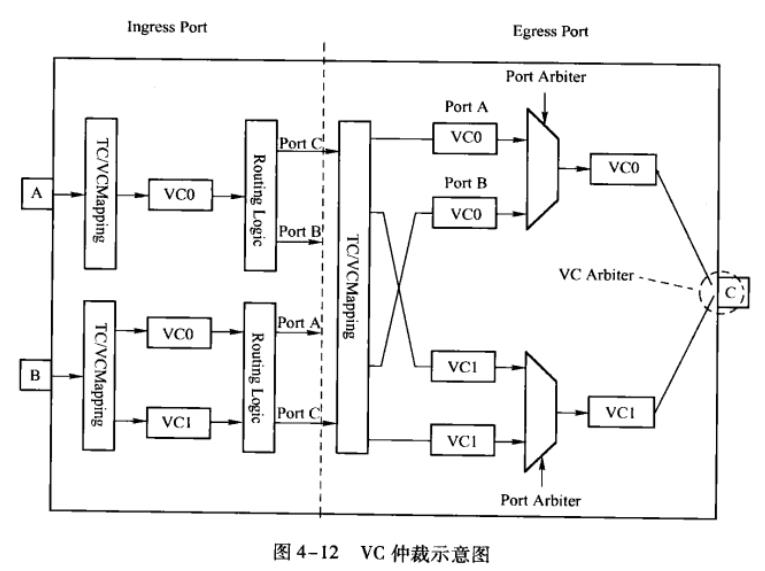

在PCIe体系结构中,链路的端口仲裁需要根据每一个VC独立设置,而且可以使用不同的算法进行端口仲裁。下文以图4 11中,Switch的两个Ingress端口A和B向Egress端口C发送数据报文为例,简要说明端口仲裁和VC仲裁的使用方法,其过程如图4 12所示。

基于VC的仲裁是指发向同一个端口的数据报文,根据使用的VC而进行仲裁的方式。如上图所示,当来自端口B和端口A数据报文(分别使用VC0和VC1通路)在到达端口C之前,需要首先进行端口仲裁后,才能进行VC仲裁。PCIe总线规定了3种VC仲裁方式, 分别为Strict Priority,RR(Round Robin)和WRR(Weighted Round Robin)算法。

当使用Strict Priority仲裁方式时,发向VC7的数据报文具有最高的优先级,而发向VC0的数据报文优先级最低。PCIe总线允许对Switch或者RC的部分VC采用Strict Priority方式进行仲裁,而对其他VC采用RR和WRR算法,如VC7~4采用Strict Priority方式,而采用其他方式处理VC3~0。

使用RR方式时,所有VC具有相同的优先级,所有VC轮流使用PCIe链路。WRR方式与RR算法类似,但是可以对每一个VC进行加权处理,采用这种方式可以适当提高VC7的优先权,而将VC0的优先权适当降低。

我们假定Ingress端口A和Ingress B向Egress端口C进行数据传递时,使用两个VC通路,分别是VC0和VC1。其中标签为TC0~3的数据报文使用VC0传送,而标签为TC4~7数据报文使用VC1传送。

而数据报文在离开Egress端口C时,需要首先进行端口仲裁,之后再通过VC仲裁,决定哪个报文优先传送。数据报文从Ingress A/B端口发送到Egress C端口时,将按照以下步骤进行处理。

(1) 首先到达Ingress A/B端口的数据报文,将根据该端口的TC/VC映射表[8]决定使用该端口的哪个VC通道。如图4 12所示,假设发向端口A的数据报文使用TC0~TC3,而发向端口B的数据报文使用TC0~TC7,这些数据报文在端口A中仅使用了VC0通道,而在端口B中使用了VC0和VC1两个通道。

(2) 数据报文在端口中传递时,将通过路由部件(Routing Logic),将报文发送到合适的端口。如图4 12所示,端口C可以接收来自端口A或者B的数据报文。

(3) 当数据报文到达端口C时,首先需要经过TC/VC映射表,确定在端口C中使用哪个VC通路接收不同类型的数据报文。

(4) 对于端口C,其VC0通道可能会被来自端口A的数据报文使用,也可能会被来自端口B的数据报文使用。因此在PCIe的Switch中必须设置一个端口仲裁器,决定来自不同数据端口的数据报文如何使用VC通路。

(5) 数据报文通过端口仲裁后,获得VC通路的使用权之后,还需要经过Switch中的VC仲裁器,将数据报文发送到实际的物理链路中。

PCIe总线规定,系统设计者可以使用以下三种方式进行端口仲裁。

(1) Hardware-fixed仲裁策略。如在系统设计时,采用固化的RR仲裁方法。这种方法的硬件实现原理较为简单,此时系统软件不能对端口仲裁器进行配置。

(2) WRR仲裁策略,即加权的RR仲裁策略。

(3) Time-Based WRR仲裁策略,基于时间片的WRR仲裁策略,PCIe总线可以将一个时间段分为若干个时间片(Phase),每个端口占用其中的一个时间片,并根据端口使用这些时间片的多少对端口进行加权的一种方法。使用WRR和Time-Based WRR仲裁策略,可以在某种程度上提高PCIe总线的QoS。

PCIe设备的Capability寄存器规定了端口仲裁使用的算法。有些PCIe设备并没有提供多种端口仲裁算法,可能也并不含有Capability寄存器。此时该PCIe设备使用Hardware-fixed仲裁策略。

5、PCIe-to-PCI/PCI-X桥片

本节将PCIe-to-PCI/PCI-X桥片简称为PCIe桥片。该桥片有两个作用。

• 将PCIe总线转换为PCI总线,以连接PCI设备。在一个没有提供PCI总线接口的处理器中,需要使用这类桥片连接PCI总线的外设。许多PowerPC处理器在提供PCIe总线的同时,也提供了PCI总线,因此PCIe-to-PCI桥片对基于PowerPC处理器系统并不是必须的。

• 将PCI总线转换为PCIe总线(这也被称为Reverse Bridge),连接PCIe设备。一些低端的处理器并没有提供PCIe总线,此时需要使用PCIe桥将PCI总线转换为PCIe总线,才能与其他PCIe设备互连。这种用法初看比较奇怪,但是在实际应用中,确实有使用这一功能的可能。本节主要讲解PCIe桥的第一个作用。

PCIe桥的一端与PCIe总线相连,而另一端可以与一条或者多条PCI总线连接。其中可以连接多个PCI总线的PCIe桥也被称为多端口PCIe桥。

PCIe总线规范提供了两种多端口PCIe桥片的扩展方法。多端口PCIe桥片指具有一个上游端口和多个下游端口的桥片。其中上游端口连接PCIe链路,而下游端口推出PCI总线,连接PCI设备。

目前虽然PCIe总线非常普及,但是仍然有许多基于PCI总线的设计,这些基于PCI总线的设计可以通过PCIe桥,方便地接入到PCIe体系结构中。目前有多家半导体厂商可以提供PCIe桥片,如PLX、NXP、Tundra和Intel。就功能的完善和性能而言,Intel的PCIe桥无疑是最佳选择,而PLX和Tundra的PCIe桥在嵌入式系统中得到了广泛的应用。

二、PCIe设备的扩展配置空间

本书在上一节讲述了PCI设备使用的基本配置空间。这个基本配置空间共由64个字节组成,其地址范围为0x00~0x3F,这64个字节是所有PCI设备必须支持的。事实上,许多PCI设备也仅支持这64个配置寄存器。

此外PCI/PCI-X和PCIe设备还扩展了0x40~0xFF这段配置空间,在这段空间主要存放一些与MSI或者MSI-X中断机制和电源管理相关的Capability结构。其中所有能够提交中断请求的PCIe设备,必须支持MSI或者MSI-X Capability结构。

PCIe设备还支持0x100~0xFFF这段扩展配置空间。PCIe设备使用的扩展配置空间最大为4KB,在PCIe总线的扩展配置空间中,存放PCIe设备所独有的一些Capability结构,而PCI设备不能使用这段空间。

在x86处理器中,使用CONFIG_ADDRESS寄存器与CONFIG_DATA寄存器访问PCIe配置空间的0x00~0xFF,而使用ECAM方式访问0x000~0xFFF这段空间;而在PowerPC处理器中,可以使用CFG_ADDR和CFG_DATA寄存器访问0x000~0xFFF。

PCI-X和PCIe总线规范要求其设备必须支持Capabilities结构。在PCI总线的基本配置空间中,包含一个Capabilities Pointer寄存器,该寄存器存放Capabilities结构链表的头指针。在一个PCIe设备中,可能含有多个Capability结构,这些寄存器组成一个链表,其结构如图4 14所示。

其中每一个Capability结构都有唯一的ID号,每一个Capability寄存器都有一个指针,这个指针指向下一个Capability结构,从而组成一个单向链表结构,这个链表的最后一个Capability结构的指针为0。

一个PCIe设备可以包含多个Capability结构,包括与电源管理相关、与PCIe总线相关的结构、与中断请求相关的Capability结构、PCIe Capability结构和PCIe扩展的Capability结构。

以上是关于013 PCIe体系结构的组成部件的主要内容,如果未能解决你的问题,请参考以下文章