FPGA的学习:流水灯的实现

Posted 石小舟

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了FPGA的学习:流水灯的实现相关的知识,希望对你有一定的参考价值。

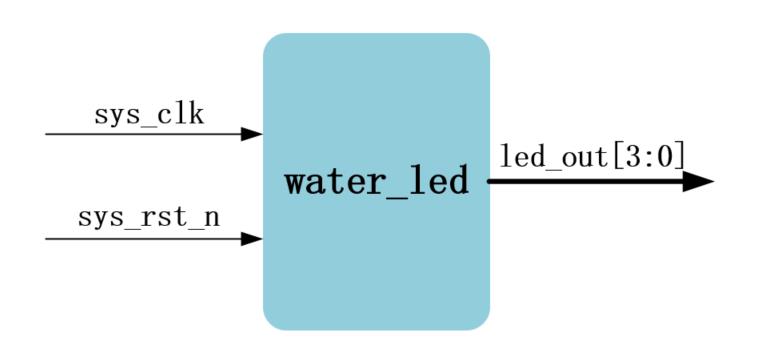

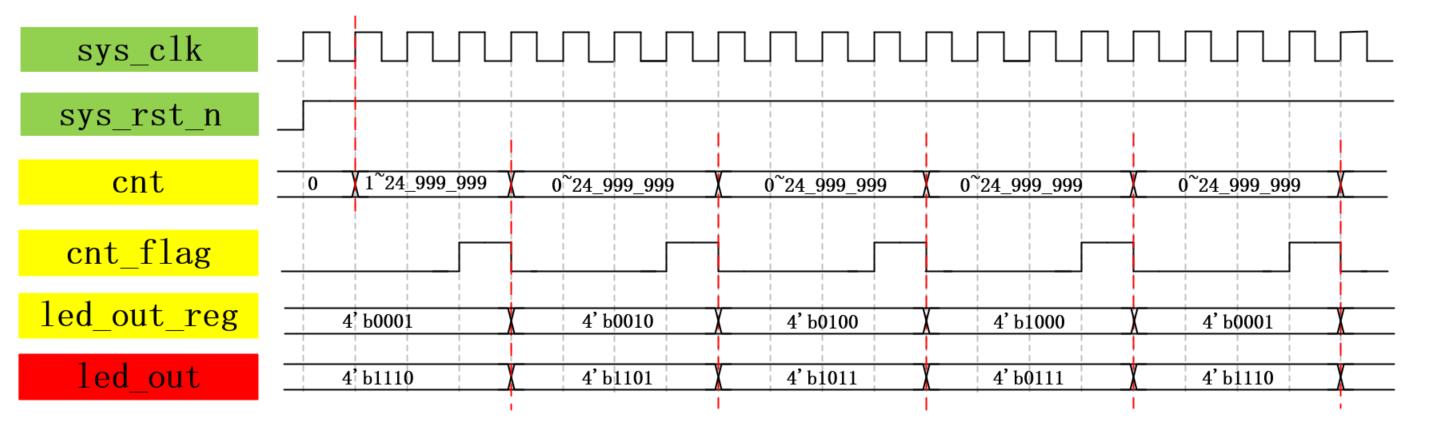

首先来看流水灯的系统框图和时序图。

了解了实现原理之后,照着原理来用代码实现。

`timescale 1ns/1ns

module water_led

#(

parameter CNT_MAX = 25'd24_999_999

)

(

input wire sys_clk , //系统时钟50Mh

input wire sys_rst_n , //全局复位

output wire [3:0] led_out //输出控制led灯

);

//寄存器的定义

reg [24:0] cnt ;

reg cnt_flag ;

reg [3:0] led_out_reg ;

//cnt:计数器计数500ms

always@(posedge sys_clk or negedge sys_rst_n)

if(sys_rst_n == 1'b0)

cnt <= 25'b0;

else if(cnt == CNT_MAX)

cnt <= 25'b0;

else

cnt <= cnt + 1'b1;

//cnt_flag:计数器计数满500ms标志信号

always@(posedge sys_clk or negedge sys_rst_n)

if(sys_rst_n == 1'b0)

cnt_flag <= 1'b0;

else if(cnt == CNT_MAX - 1)

cnt_flag <= 1'b1;

else

cnt_flag <= 1'b0;

//led_out_reg:led循环流水

always@(posedge sys_clk or negedge sys_rst_n)

if(sys_rst_n == 1'b0)

led_out_reg <= 4'b0001;

else if(led_out_reg == 4'b1000 && cnt_flag == 1'b1)

led_out_reg <= 4'b0001;

else if(cnt_flag == 1'b1)

led_out_reg <= led_out_reg << 1'b1; //左移

assign led_out = ~led_out_reg;

endmodule

接着是仿真代码的编写

`timescale 1ns/1ns

module tb_water_led();

wire [3:0] led_out ;

reg sys_clk ;

reg sys_rst_n ;

//初始化系统时钟、全局复位

initial begin

sys_clk = 1'b1;

sys_rst_n <= 1'b0;

#20

sys_rst_n <= 1'b1;

end

//sys_clk:模拟系统时钟,每10ns电平翻转一次,周期为20ns,频率为50Mhz

always #10 sys_clk = ~sys_clk;

water_led

#(

.CNT_MAX (25'd24)

)

water_led_inst

(

.sys_clk (sys_clk ), //input sys_clk

.sys_rst_n (sys_rst_n ), //input sys_rst_n

.led_out (led_out ) //output [3:0] led_out

);

endmodule

流水灯的功能实现。

以上是关于FPGA的学习:流水灯的实现的主要内容,如果未能解决你的问题,请参考以下文章