主存储器组织

Posted Ston.V

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了主存储器组织相关的知识,希望对你有一定的参考价值。

图片及主要内容源自mooc讲义

1.存储器基本概念

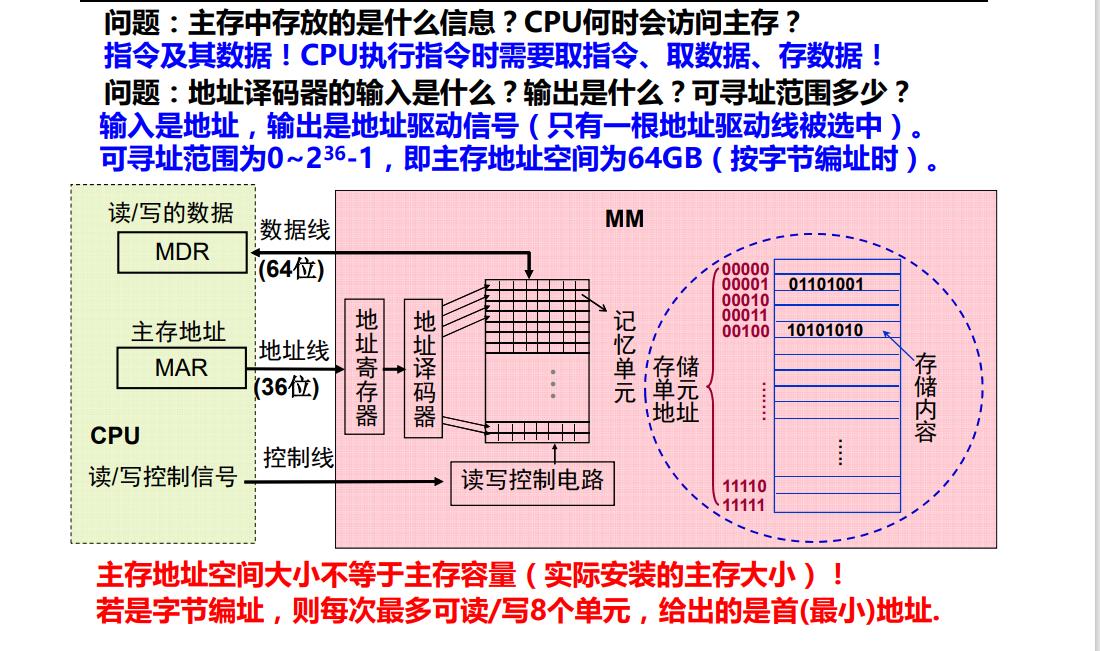

1.1 主存的结构

通过CPU的不同周期来分别读取地址和数据,有时访问地址可能会进行时分复用(一遍是行地址,一遍是列地址)

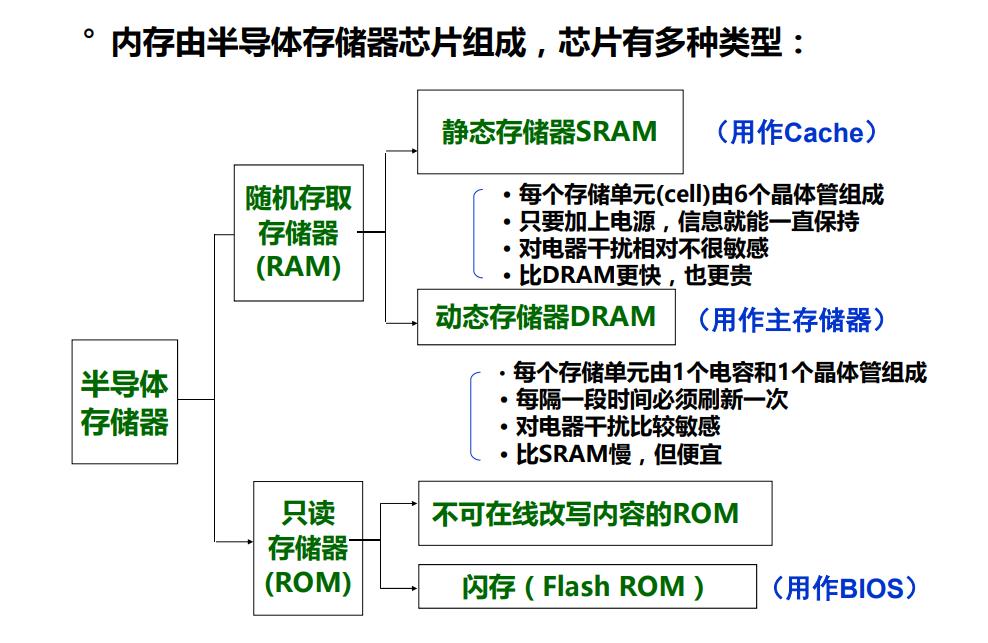

1.2 分类

2.主存的读写

2.1 芯片结构

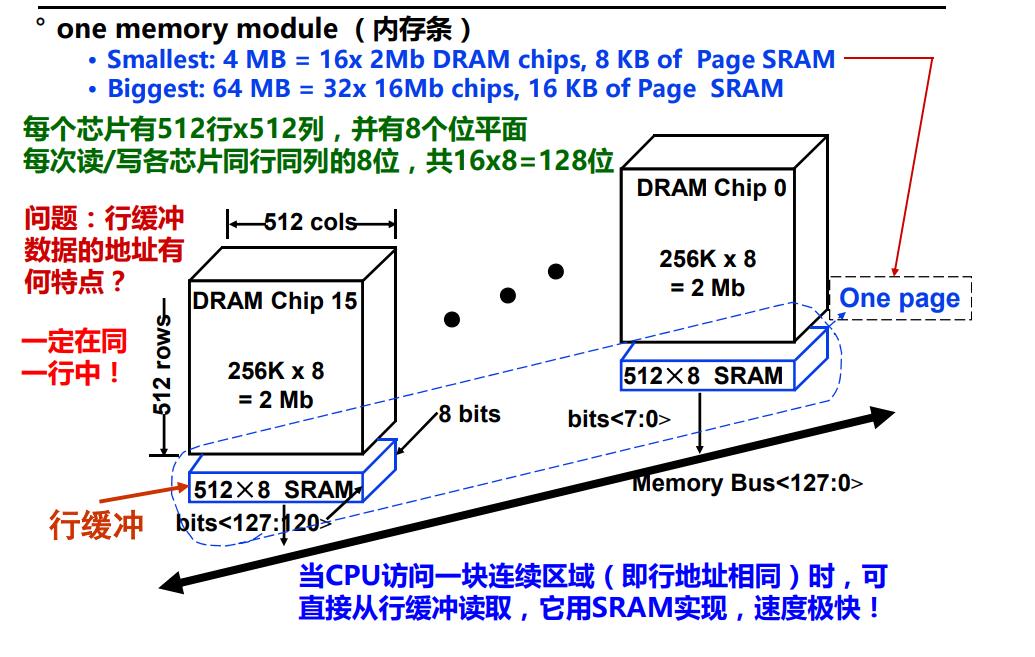

每个芯片有八个位平面,因此每次在一个芯片上确定一个行列地址,也就确定了一个字节的内容

2.2内存条结构

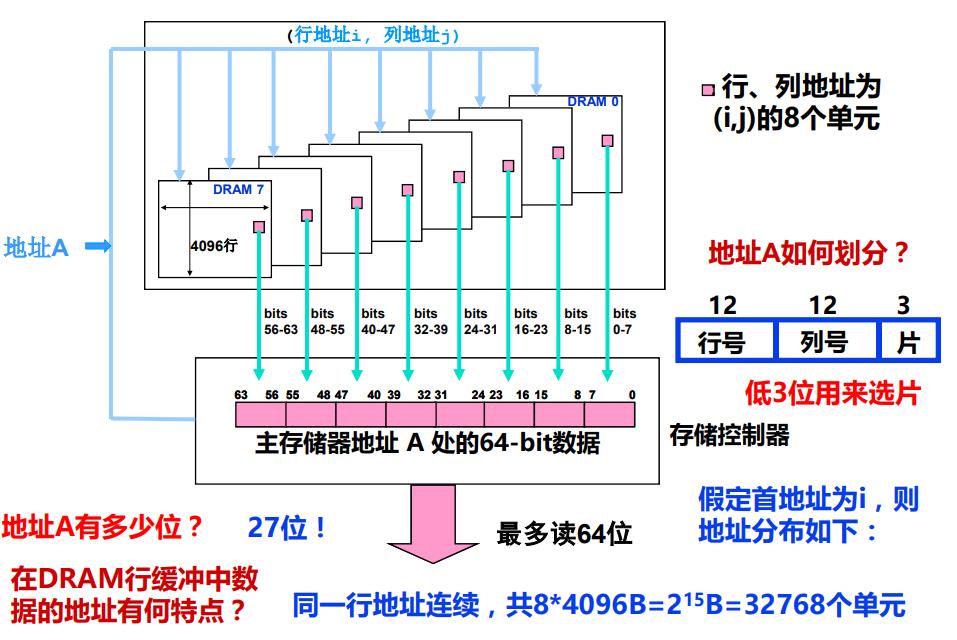

而我们的内存条一块又是由多个(这里是8个)芯片并列组成的,每次选中都实际选了8个。

假如全部选中,一次能读写8*8=64位数据;如果我们要读写的数据小于64位,那么我们需要使用片选信号来确定是哪几个芯片的数据;如果大于64位,由于数据对齐,我们读写的总是64位的倍数,也就不再使用片选信号了。

行缓冲:这里我们一行共有4096个单元,每个芯片的每个单元又有8位,内存条共有8个芯片,因此一个行缓冲的数据量为:4098B*8

2.3 交叉编址

选中一行直接是选中了8块芯片,因此在一块芯片内部是交叉编址,这样才能保证8个芯片的同行同列的地址是连续的

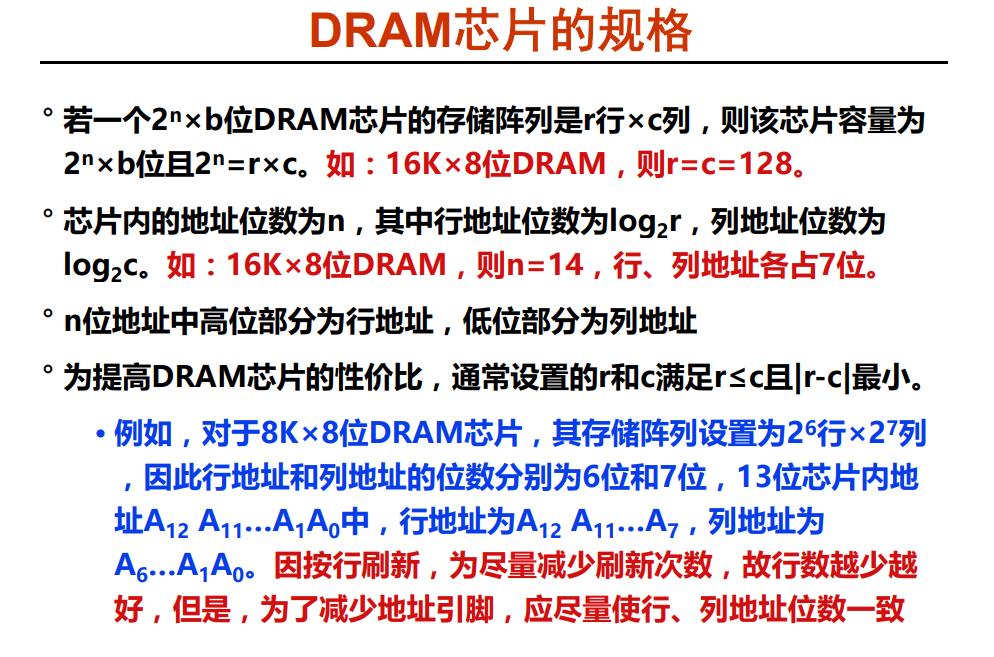

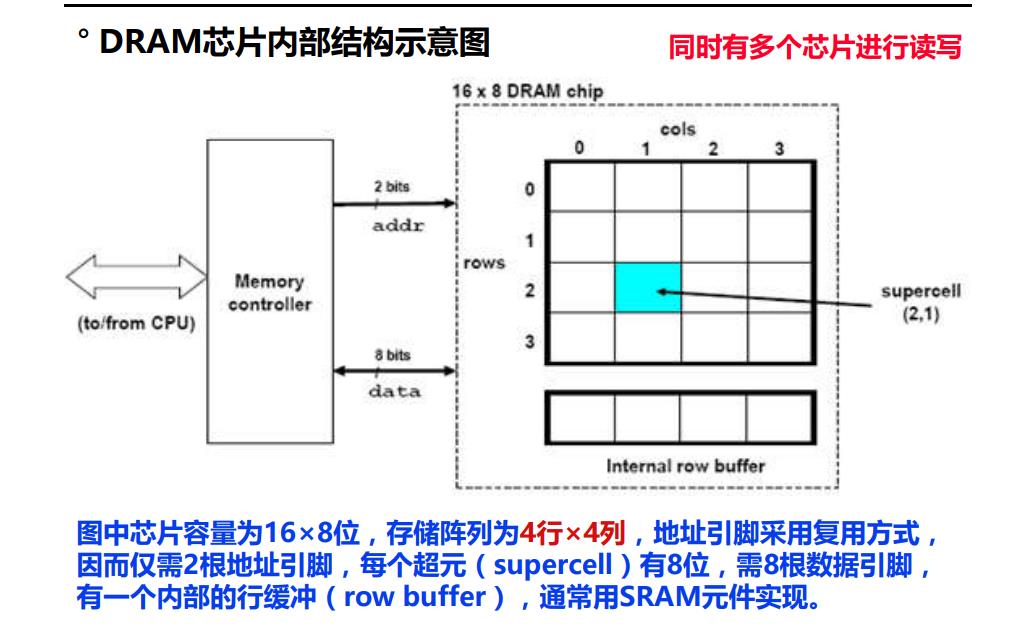

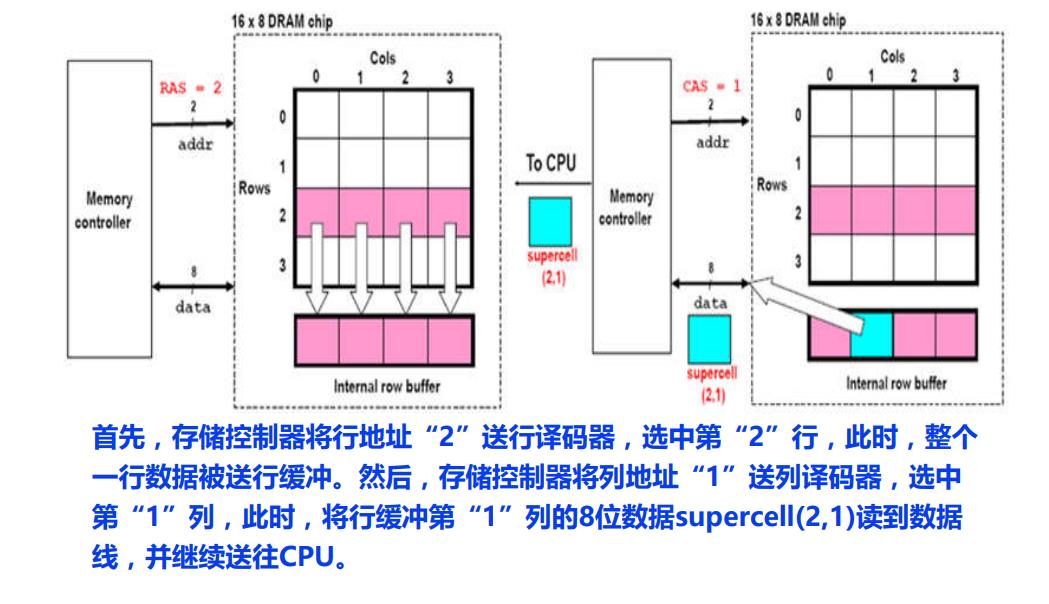

2.4 DRAM规格

2.5 DRAM读写原理

CPU与主存都是三条线连接:地址,控制,数据。总数先传送地址(分时复用)和控制信号,然后读写数据(通过总线)

以上是关于主存储器组织的主要内容,如果未能解决你的问题,请参考以下文章