再也不怕《计算机组成原理》这门课了

Posted ZSYL

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了再也不怕《计算机组成原理》这门课了相关的知识,希望对你有一定的参考价值。

学习笔记

计算机的发展

- 低电频表示0,高电平表示1

- 主板上的印刷电路,可以传递电信号即二进制数位(1bit)

- 计算机系统 = 硬件+软件

- 逻辑元件:电子管-晶体管-集成电路(许多晶体管连在一起)

- 内存:汞延迟线、磁鼓-磁芯-半导体

- 机器字长:计算机一次整数运算所能处理的二进制位数

- 冯诺依曼:五大部件组成、指令和数据可以同等地位存储于存储器、指令和数据用二进制表示、指令又操作码和地址码组成、存储程序、以运算器为中心

- CPU:运算器和控制器

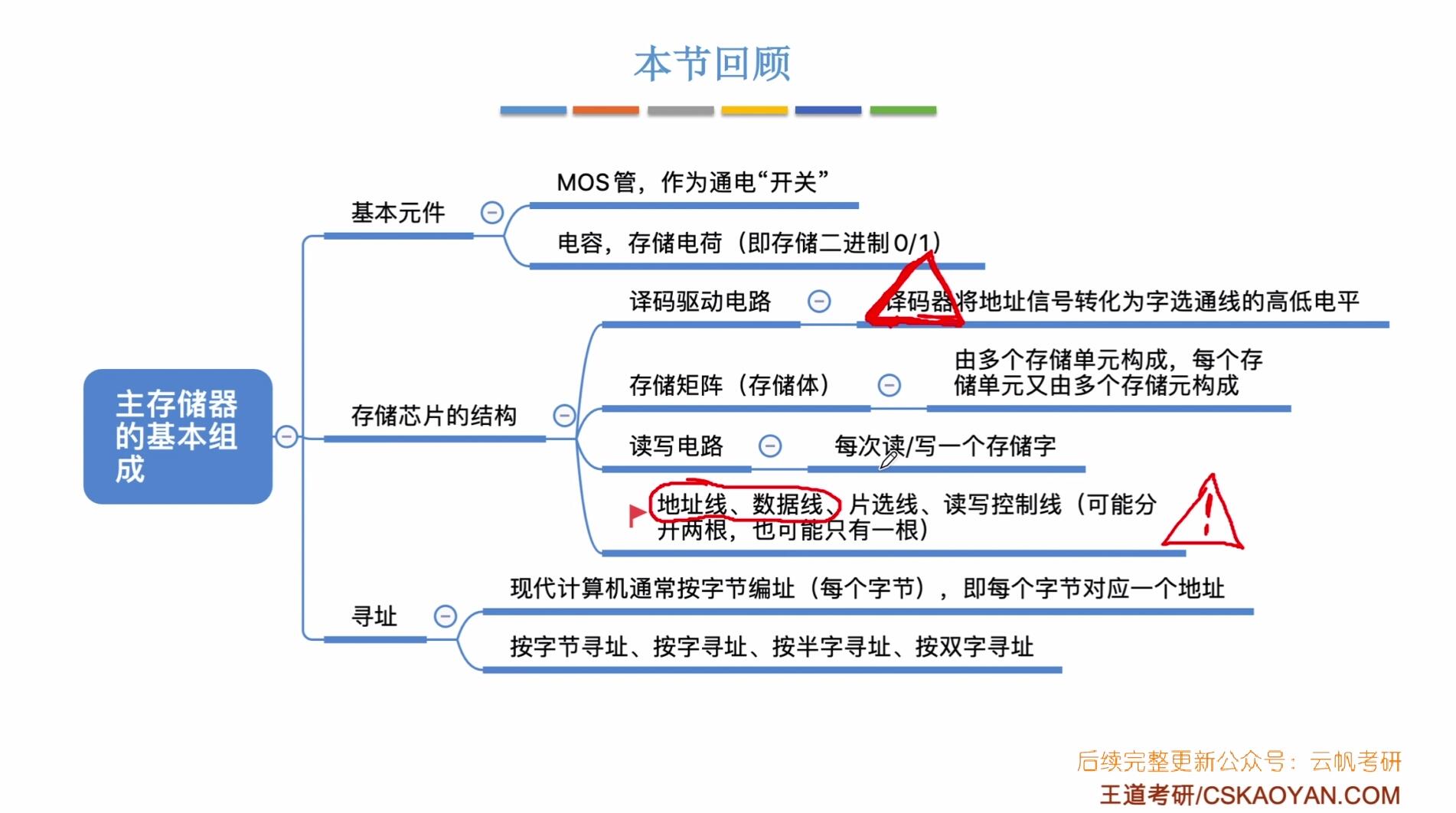

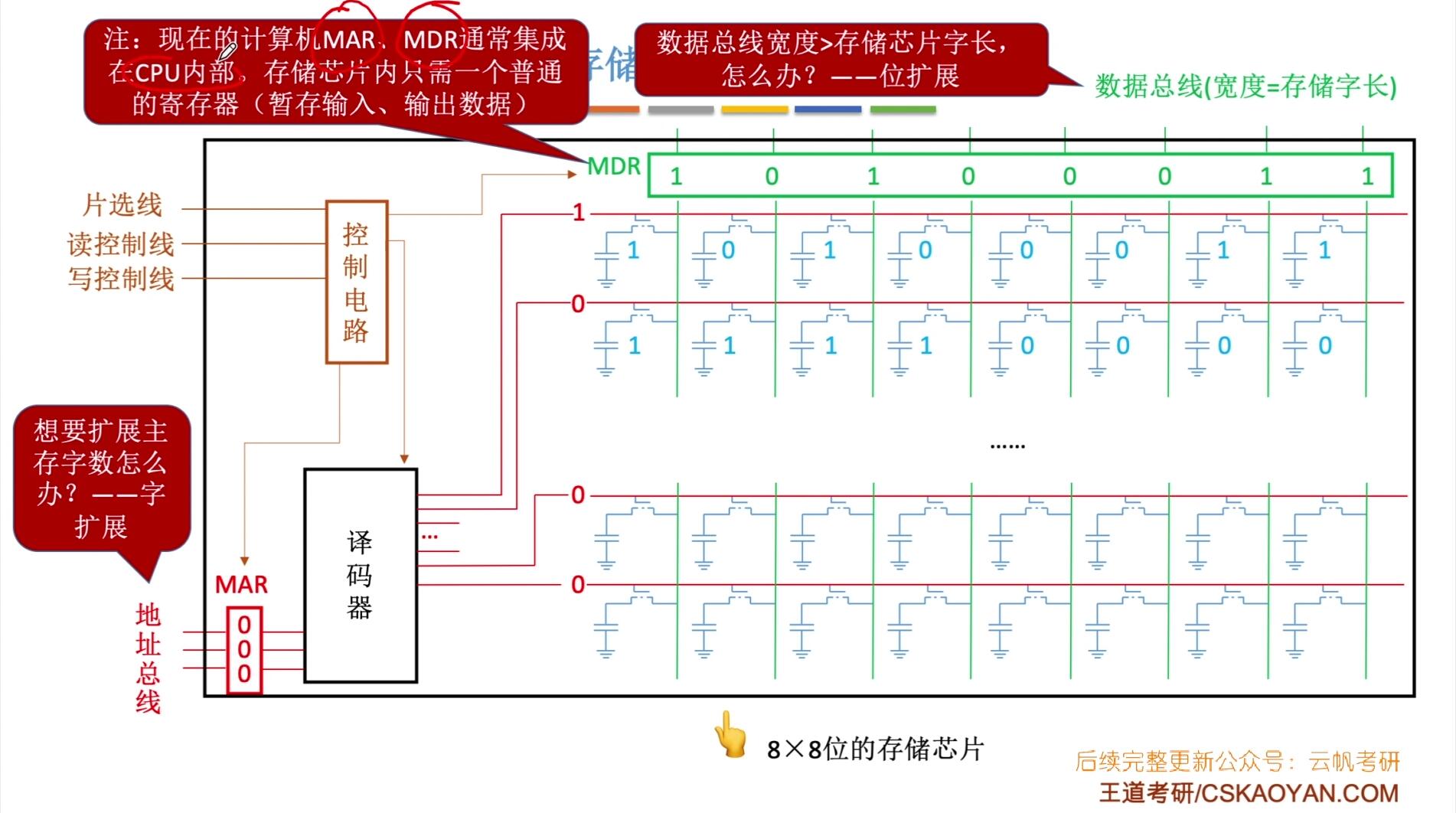

主存储器的基本组成

- MAR(Memory Address Register):存储地址寄存器

- MDR(Memory Data Register):存储数据寄存器

- 存储体:数据在存储体内按地址存

- 存储单元:每个存储单元放一串二进制代码

- 存储字:存储单元中二进制代码的组合

- 存储字长:存储单元中二进制代码的位数

- 存储元:存储二进制的电子元件,每个存储元可存1bit

- 例:MAR=4位:总共有2^4个存储单元,MDR=16位:每个存储单元可存放16bit,1个字 = 16bit

- 1byte字节 = 8bit,1B = 1byte,1b =1bit

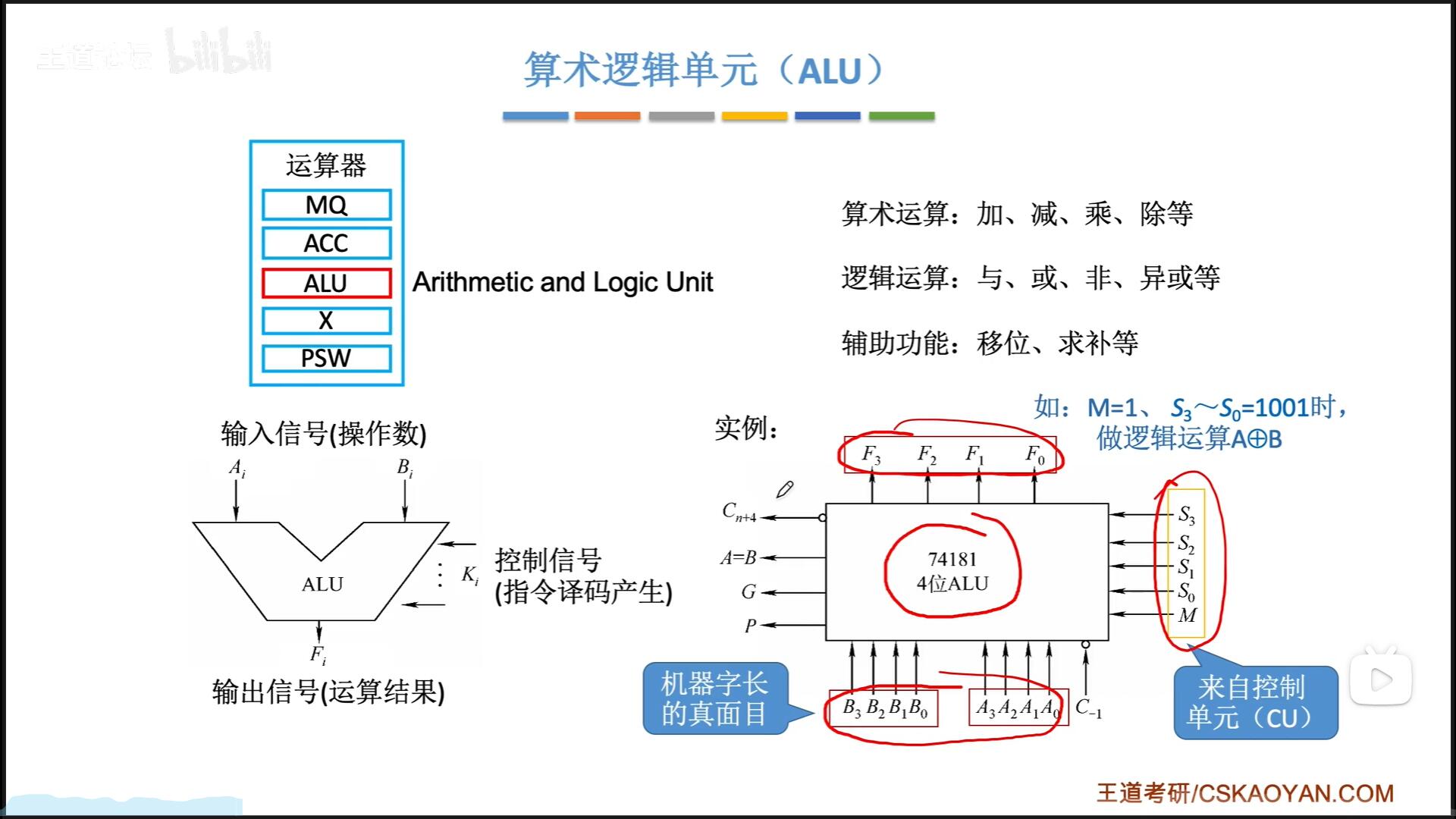

运算器的基本组成

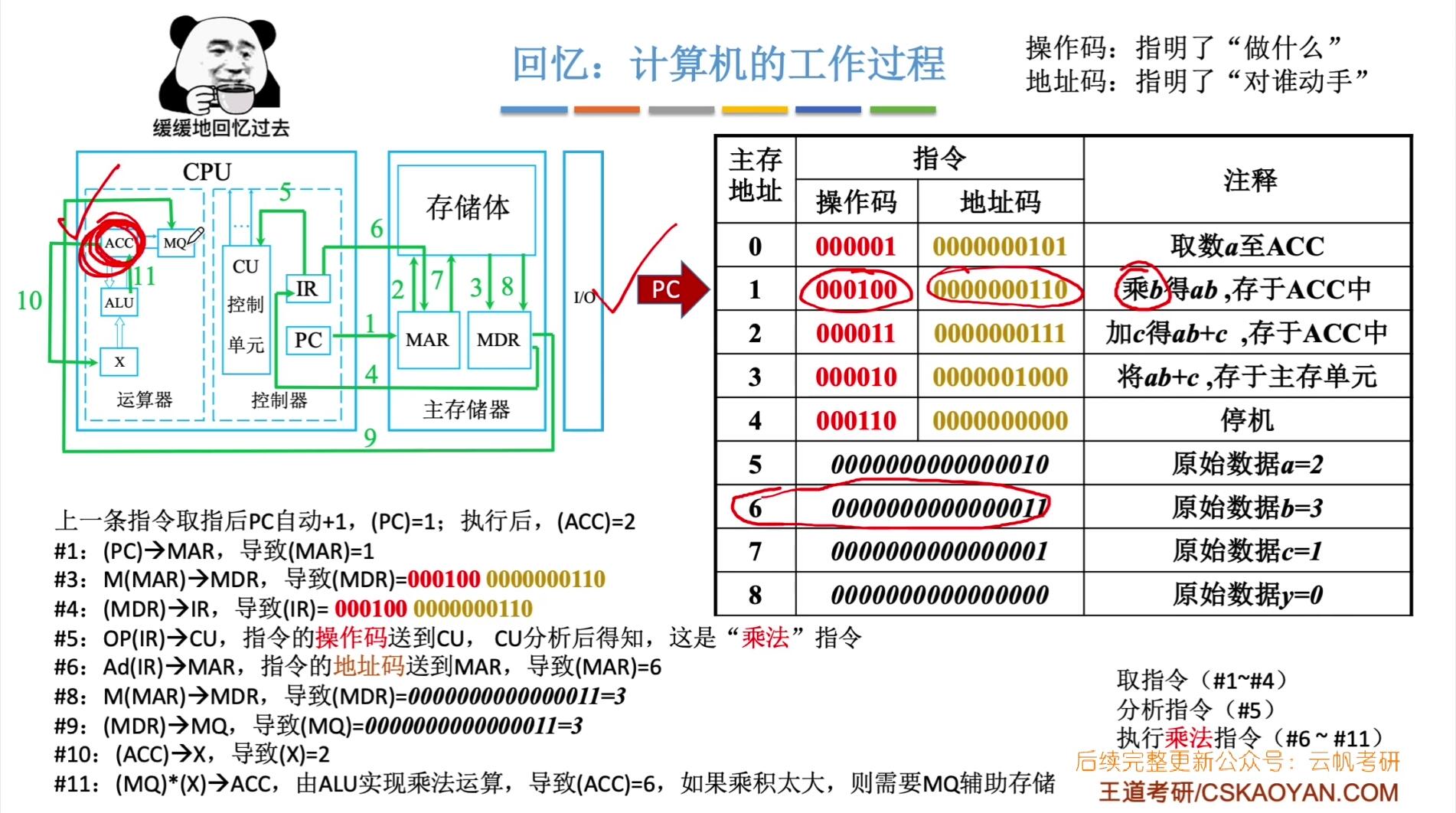

- ACC(Accumulator):累加器,用于存放操作数和运算结果。

- MQ(Multiple_Quotient Register):乘商寄存器,在乘商运算时存放操作数和运算结果。

- x:通用操作数寄存器,用于存放操作数。

- ALU(Arithmetic and logic Unit):算术逻辑单元,通过复杂的电路实现算数运算、逻辑运算。

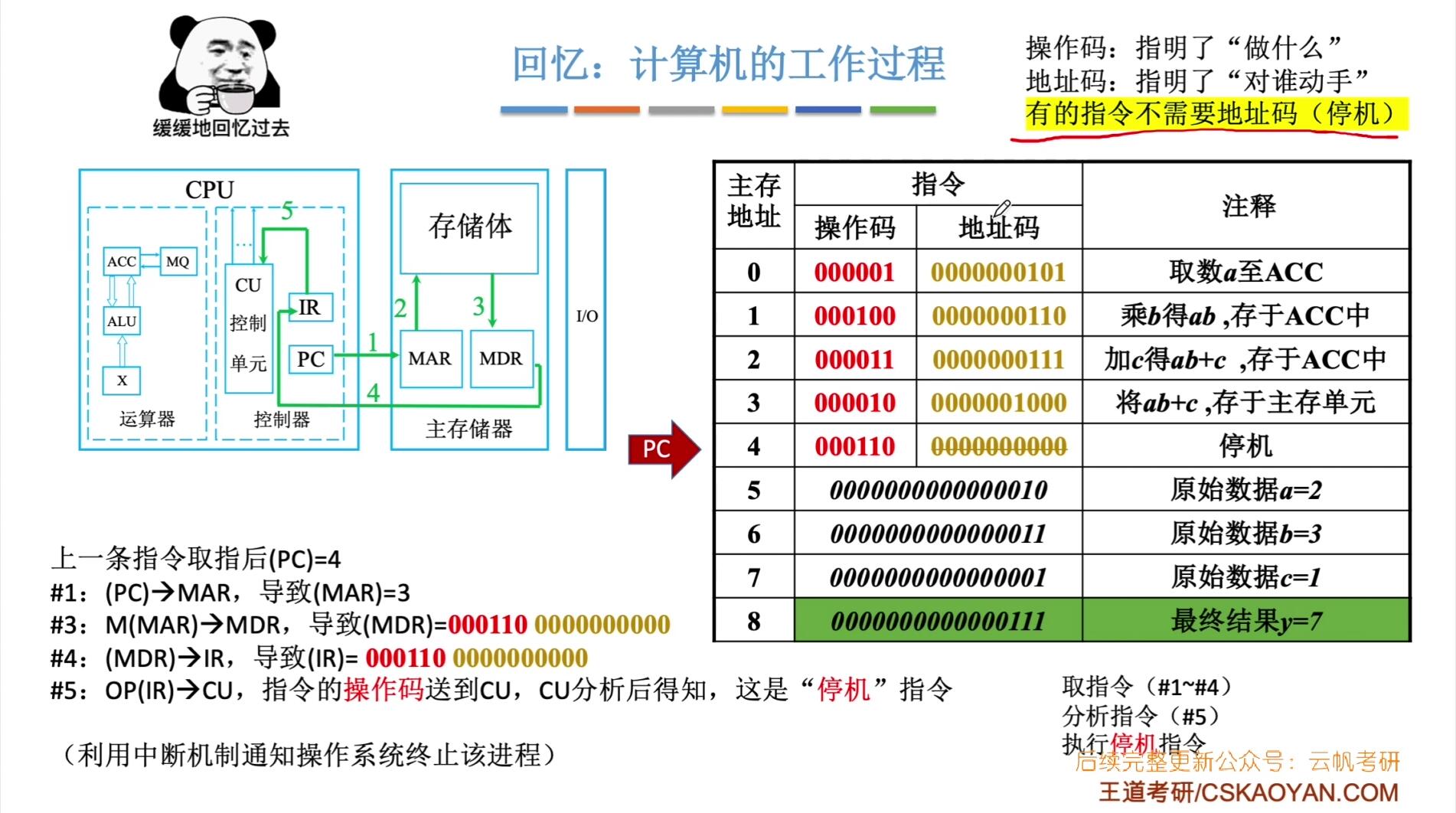

控制器的基本组成

- CU(Control Unit):控制单元,分析指令,给出控制信号。

- IR(Instruction Register):指令寄存器,存放当前执行的指令。

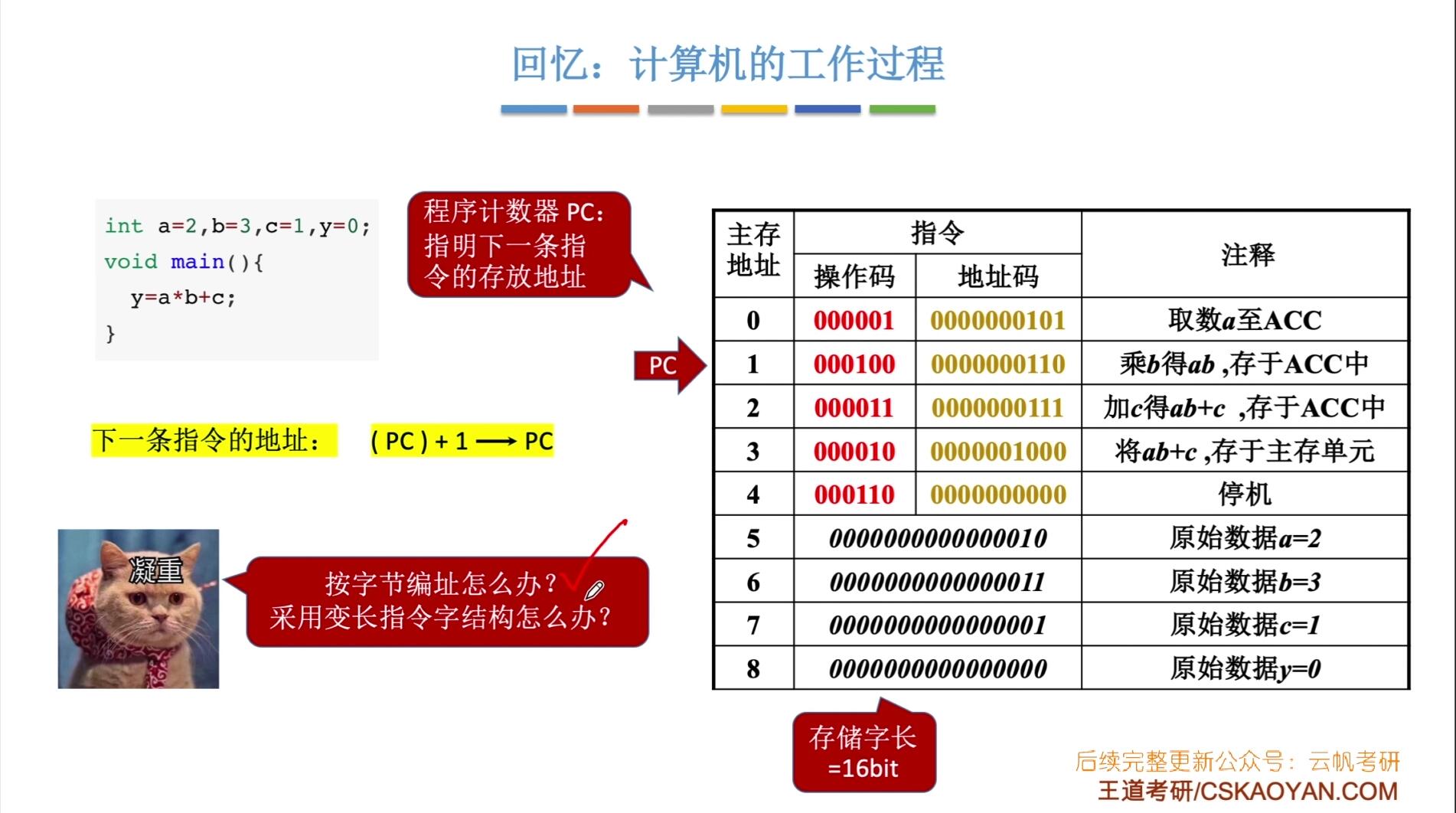

- PC(Program Counter):程序计数器,存放下一条指令的地址,自动+1。

- 若乘积太大,则需要MQ辅助存储,被乘数放在MQ中,乘数放在x(通用操作寄存器)中。

- PC-MAR-M(MAR)-MDR-IR-PC+1- IR-CU(指令寄存器)取出指令后,提取操作码,给CU(控制单元),CU分析指令的具体含义

- 十进制到2进制 整数:除基取余法,小数:乘基取整法

计算机性能指标

-

MAR位数:反映存储单元的个数

-

MDR位数:=存储字长=每个单元的大小

-

总容量:存储单元个个数×存储字长 bit

-

CPU主频:CPU内数字脉冲信号振荡的频率

-

CPU时钟周期 = 1 / CPU主频

-

CPI:执行一条指令所需的时钟周期数

-

执行一条指令的耗时 = CPI×CPU时钟周期

-

CPU执行时间(整个程序的耗时) = CPU时钟周期数 / 主频 = (指令条数*CPI)/ 主频

-

IPS:每秒执行多少条指令

-

FLOPS:每秒执行多少次浮点运算

-

数据通路带宽:数据总线一次所能并行传送信息的位数(各硬件部件通过数据总线传输数据)

-

吞吐量:系统在单位时间内处理请求的数量

-

奇校验码: 整个校验码(有效信息位和校验位)中“1”的个数为奇数。

-

偶校验码: 整个校验码(有效信息位和校验位)中“1”的个数为偶数。

-

海明码: 将信息位进行偶校验->多个校验位->多个校验位标明出错位置

-

校验码状态: 2^k .n+k位都可能出错,所以2 ^ k >= n+k+1

-

循环冗余校验码: k个信息位+R个校验位作为被除数,数据发送,接收方约定一个除数,添加校验位后需保证除法余数为0。CRC码可以进行单比特纠错

定点数的表示

- 无符号数:整个机器字长的全部二进制均为数值位,没有符号位,相当于数绝对值

- n位的无符号数的表示范围:0 ~ 2^n - 1

- 正数:原码=反码=补码

- 负数:反码:符号位不变:其他位求反,补码:反码加+1;

- 补码整数的表示范围:-2^n<=x<=2 ^ n-1(比原码多表示一个 -2 ^ n)

- 负数补码转回原码的方法相同:尾数取反,末尾+1

- 移码:补码的基础上将符号位取反。移码只能用于表示整数,补码整数的表示范围:-2^n<=x<=2 ^ n-1

- [-x]补:x的补码的符号位、数值位全部取反,末尾+1

- 补码让减法操作变成加法操作

补码的加减运算

[A+C]补 = A补+C补

[A-C]补 = A补+ -C补

对于补码来说,无论加法还是减法,最终都表示成加法

溢出判断

正数符号00,负数符号11

01:上溢出

10:下溢出

符号扩展

短数据—长数据:多出的补0

模运算的性质

带余除法:x = qm + r

-3 = -112 + 9

9 = 012 + 9

21 = 1*12 + 9

模 = 补数+原数的绝对值

8位运算自动模2的8次方

移位

- 正数的补码原码相同

右移:高位补0,低位舍弃

左移:低位补0,高位舍弃 - 负数补码的算数移位

右移:高位补1,低位舍弃

左移:低位补0,高位舍弃

原码一位乘

- 乘数符号位不参加运算

- 符号位通过异或确定

- 数值部分通过被乘数与乘数绝对值的n轮加法移位完成

逻辑右移:符号位不变,高位补 0

补码一位乘

n次加法、移位 最后再多来一次加法

补码算数右移:符号位不变,高位补符号

辅助位-MQ中最低位 = 1时,ACC+x补

辅助位-MQ中最低位 = 0时,ACC+0

辅助位-MQ中最低位 = -1时,ACC+ -x补

补码算术左移,低位补0,补码的算数右移高位补1

原码的除法运算

ACC:存放被除数、余数

MQ:乘商寄存器,在乘除时,用于存放操作数或运算结果

X:通用操作数寄存器,存放除数

恢复余数法

符号位:单独异或

数值位:取绝对值进行除法计算

需求出:除数的补码 和 -补数的补码

MQ:商1:代表ACC中 被除数+X中 -除数的补

若结果为负,则说明被除数小,则MQ最后一位会置0,加上除数的补,恢复原来值.

ALU: 进行运算,运算完放入ACC中

ACC中的数不断左移。

-

余数为负 商0,并恢复余数之后,+ -y的补,余数为正,逻辑左移(低位补0,高位舍弃)

左移n次,上商n+1次,最后一次上商余数不左移。 -

当余数为负时商0,并+除数,再左移,再-|除数|

加减交替法

当余数为负时 商0,并左移,再+|除数|

若加完之后余数为负(a),加上y的补(b),恢复余数,之后左移(a+b),(a+b)* 2 + -y的补,相当于:2*a+b

- 因此若余数为负,则可以直接商0,并让余数左移1位再加上除数。

- 若余数为正,则商1,让余数左移一位,再减去除数,得到新的余数

- 最后一步若余数为负需商0,并+y的补得到正确的余数

加减可能 n+1 / n+2次,左移只需n次

补码除法:加减交替法

求出:x补,y补,-y补

- 符号位参与元素

- 被除数/余数/除数,采用双符号位

被除数和除数

同号,则被除数减去除数

异号则被除数加上除数

余数和除数同号,商1,余数左移减去除数

余数和除数异号,商0,余数左移加上除数

重复n次

末尾商置1

最后余数*2^-4

数据存储和排列

大小端模式

大端方式:低位存高地址,高位存低地址

小端方式:低位存低地址,高位存高地址

边界对齐

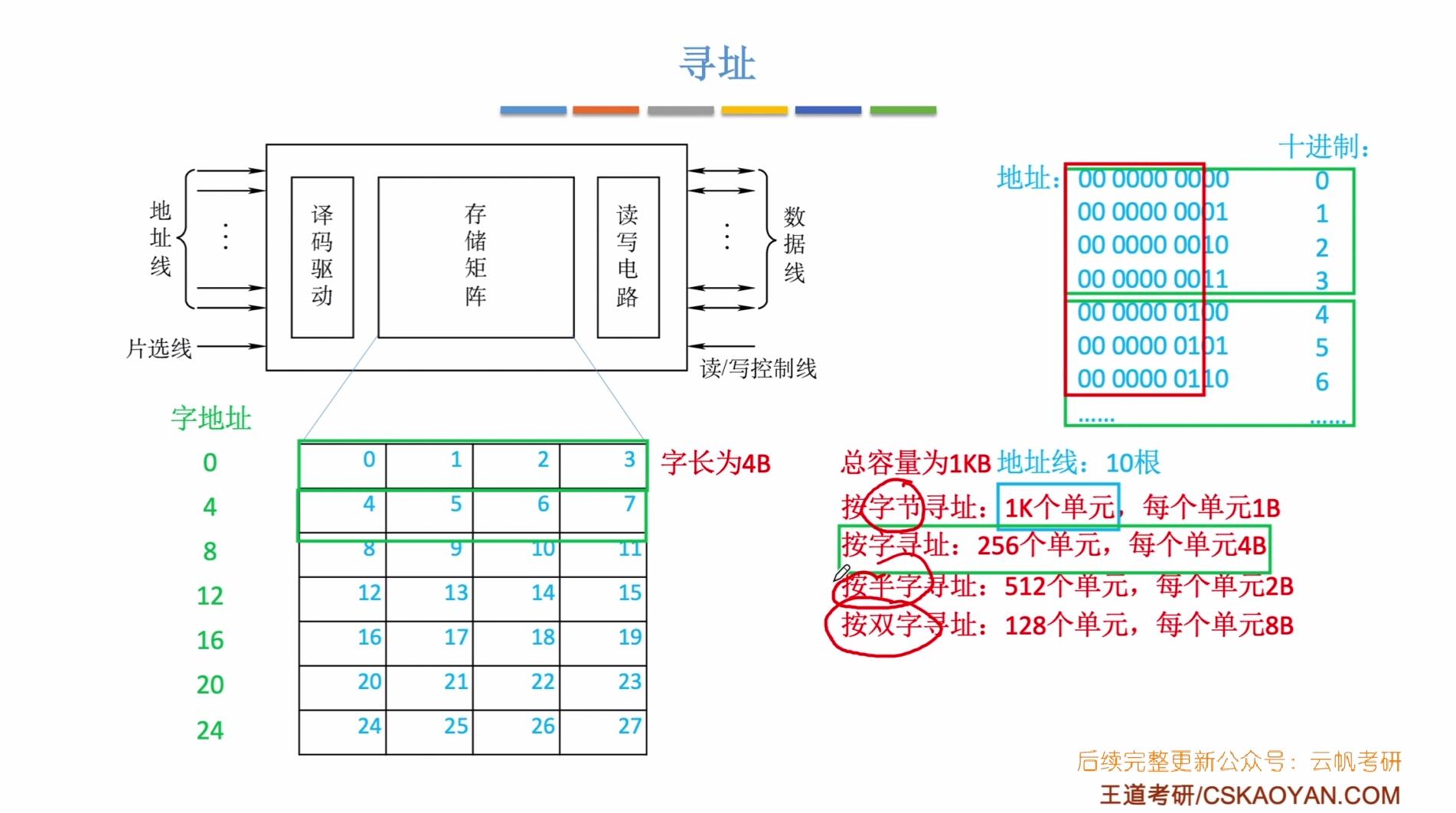

计算机按字节编址,即每个字节对应一个地址,通常也支持按字、按半字,按字节寻址。

假设存储字长32位,则一个字=32bit,半字=16bit,每次访问只能读写1个字

边界对齐方式

边界不对齐方式

浮点数的表示

阶符-阶码-尾数

阶码:反映数值的大小

尾数:反应精度

尾数右移,小数点左移,阶码增加

尾数左移,小数点右移,阶码减少

特点

-

规格化的原码尾数,最高数值一定是1

正数为0.1XXX形式,最大值是0.11111,最小值0.10000

尾数表示范围 0.5 < M < 1-2 ^ -n

负数为1.1XXX最大值:1.10000,最小值:1.11111 -

规格化的补码尾数,符号位与最高数值位一定相反

正数为0.1XXX形式,最大值是0.11111,最小值0.10000

尾数表示范围 0.5 < M < 1-2 ^ -n

负数为1.0XXX最大值:1.01111,最小值:1.00000

IEEE 754

- 移码:补码的基础上将符号位取反。移码只能用于表示整数。

- 移码=真值+偏置值

- 8位移码的偏置值:128, 2的n-1次方

- 数符+阶码(用移码表示)+尾数(原码表示)1.M

- float:数符1,阶码8位(-126-127)(阶码全1:-128,全0:-127 有特殊用处),尾数(23位),偏置值:127

- double:阶码:11位,尾数52位,数符1位,总共64位,偏置值:1023

例子:

将十进制数-0.75转换为IEEE 754的单精度浮点数格式表示

(-0.75)10 = (-0.11)2 = (-1.1)2 * 2^-1

数符 = 1

尾数= .100000…(隐含最高位1)

阶码:真值 -1,移码=真值+偏移量=-1+127=126=0111 1110(凑足8位)

–>1 0111 1110 1000000000000

IEEE 754 的单精度浮点数 C0 A0 00 00 H 的值是多少:

- 转化为二进制:

1100 0000 1010 0000 0000 0000 0000 00000 - 数符:1

- 尾数:.01000000000(隐含最高位1)–>尾数真值=(1.01)2

- 移码:10000001,若看作无符号数:129

- 单精度偏移量:127

- 真值:移码-偏移量=129-127=2=(1000 0001)-(111 1111)= (0000 0010)2 = (2)10

- 结果:(-1.01) * 2^2 = -1.25*4 = -5.0

最小绝对值,最大绝对值:

最小绝对值:尾数全为0,阶码真值最小:-126

真值:1.0*2^-126,最小 1-2 ^ N-1

最大值:尾数全为1,阶码真值最大127,整体真值为(1.111111) * 2 ^127

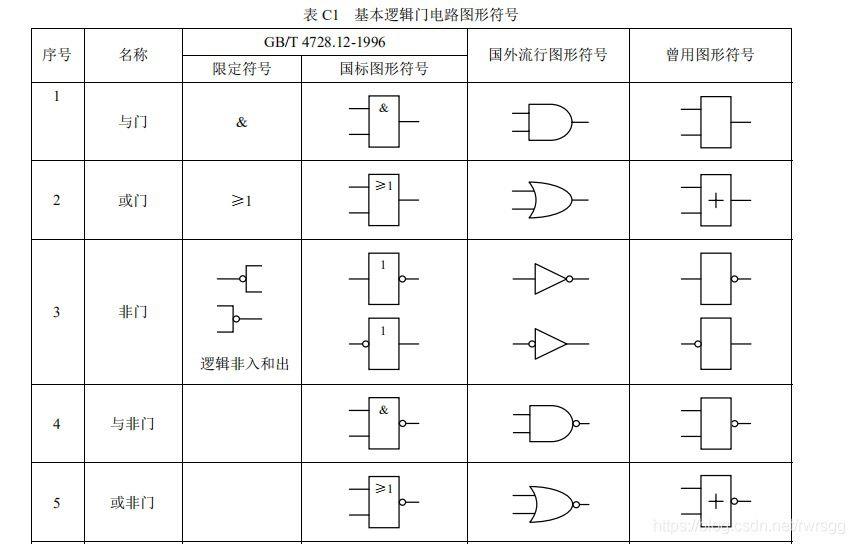

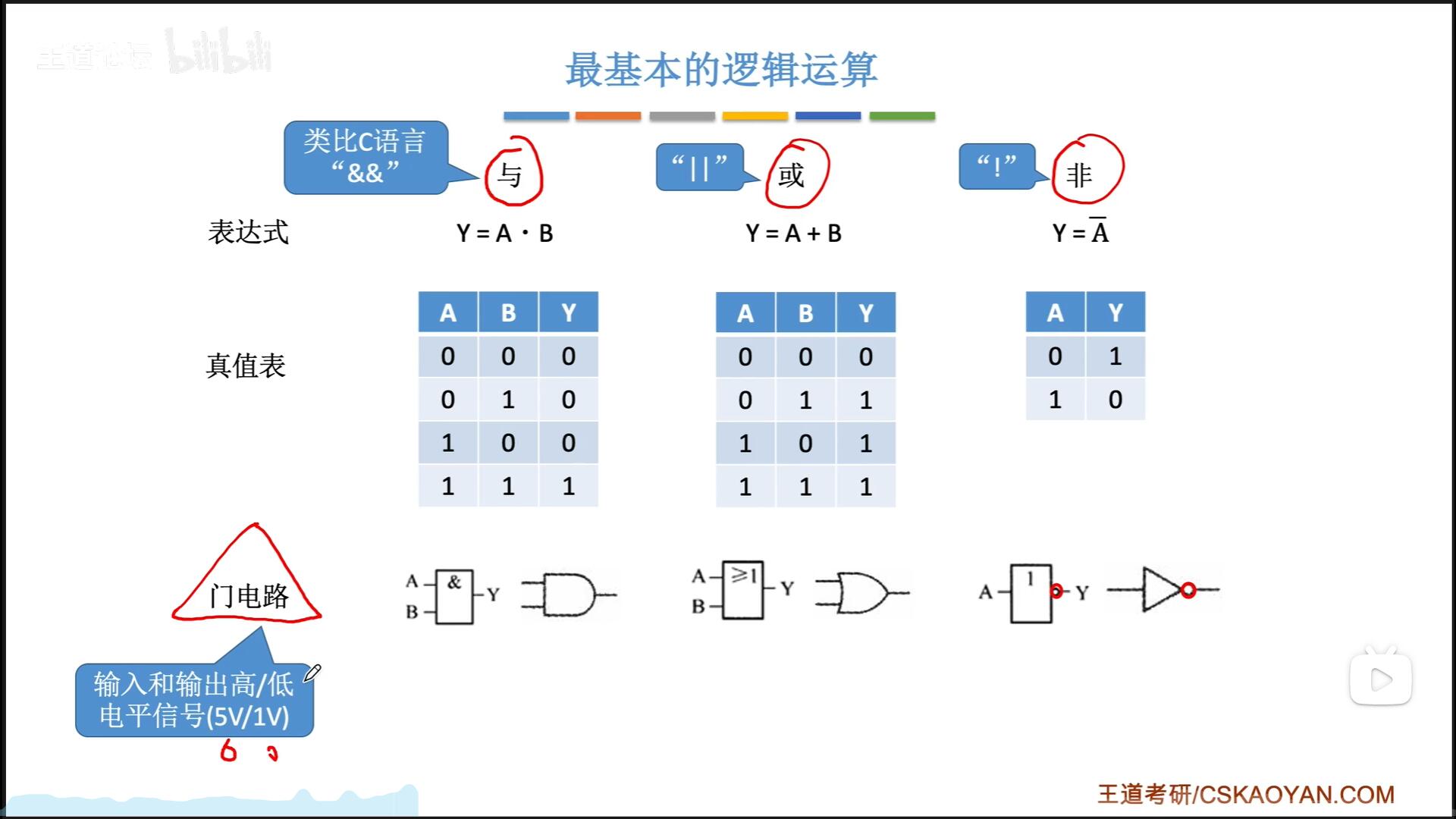

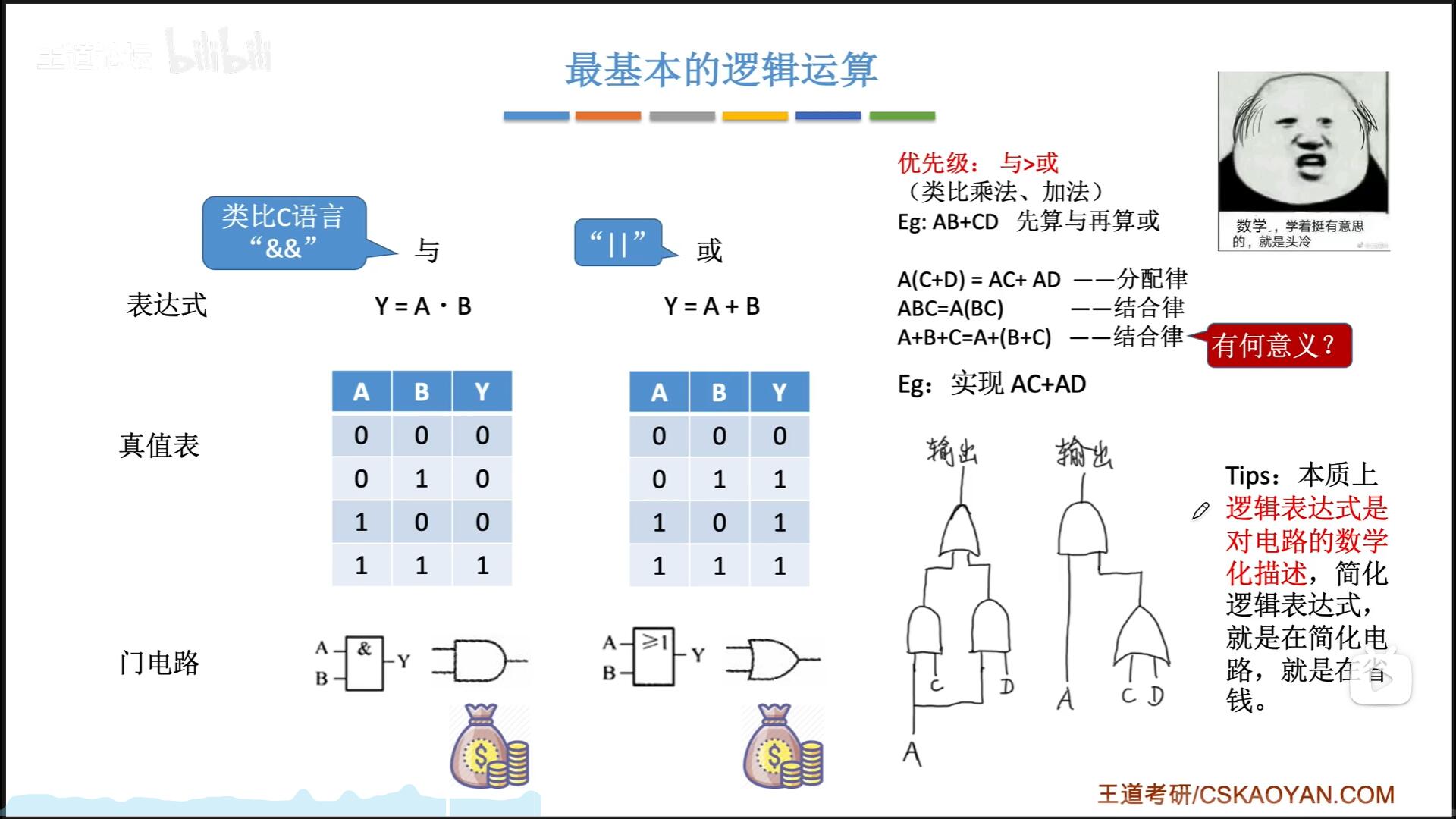

电路的基本原理

算术逻辑单元ALU

常见逻辑门电路符号表示

最基本的逻辑运算

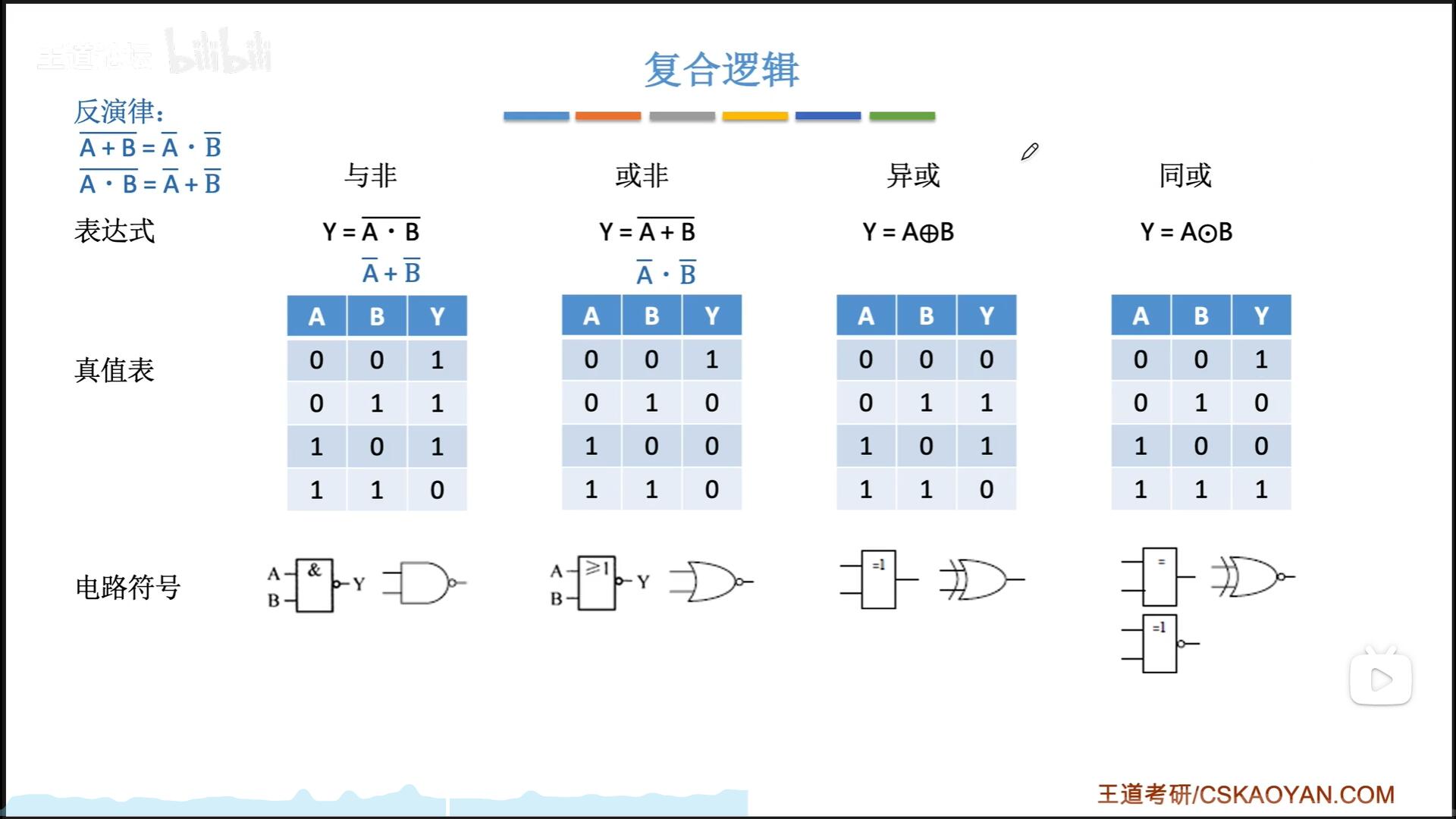

复合逻辑

同或:

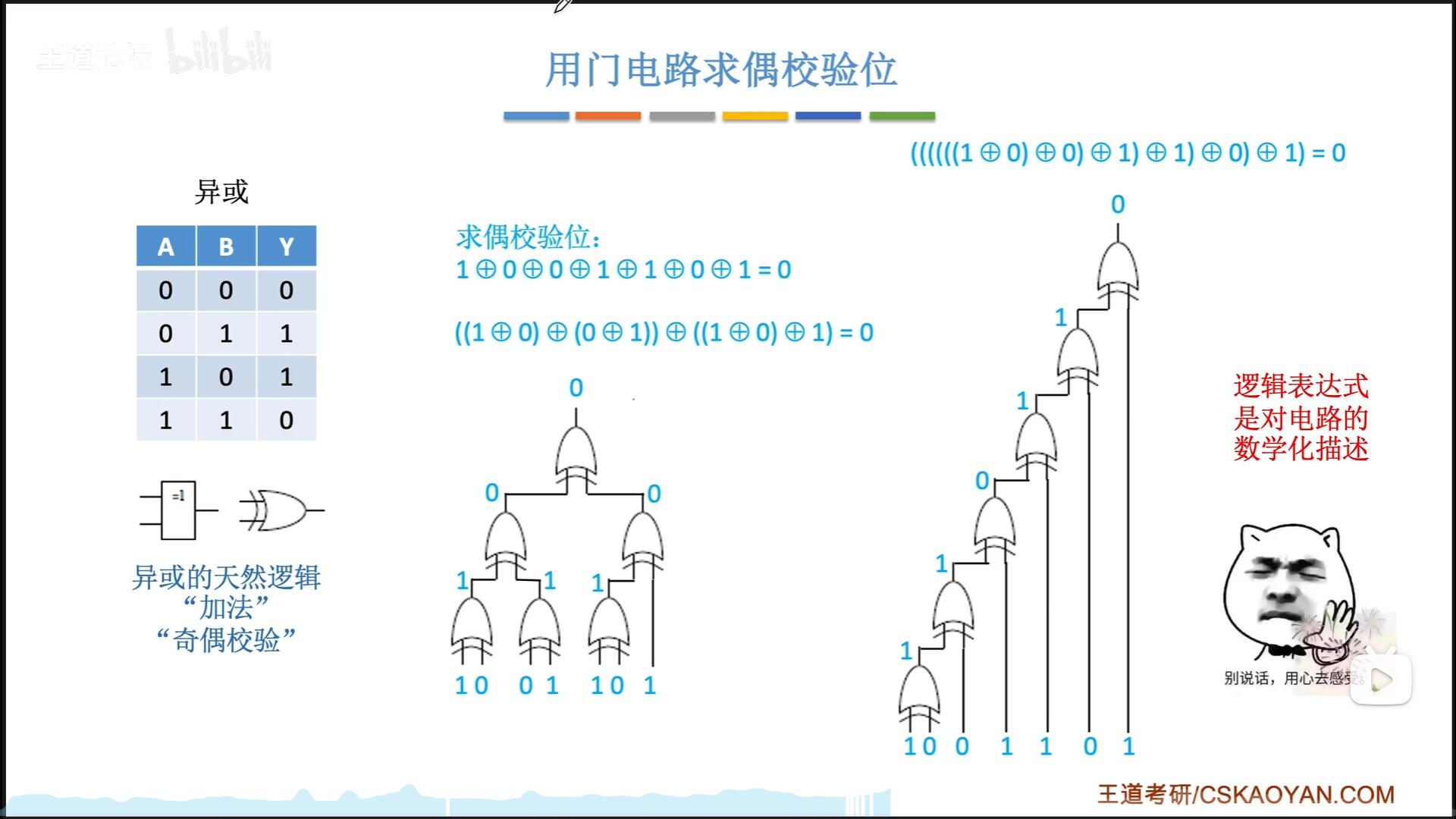

门电路求偶校验位

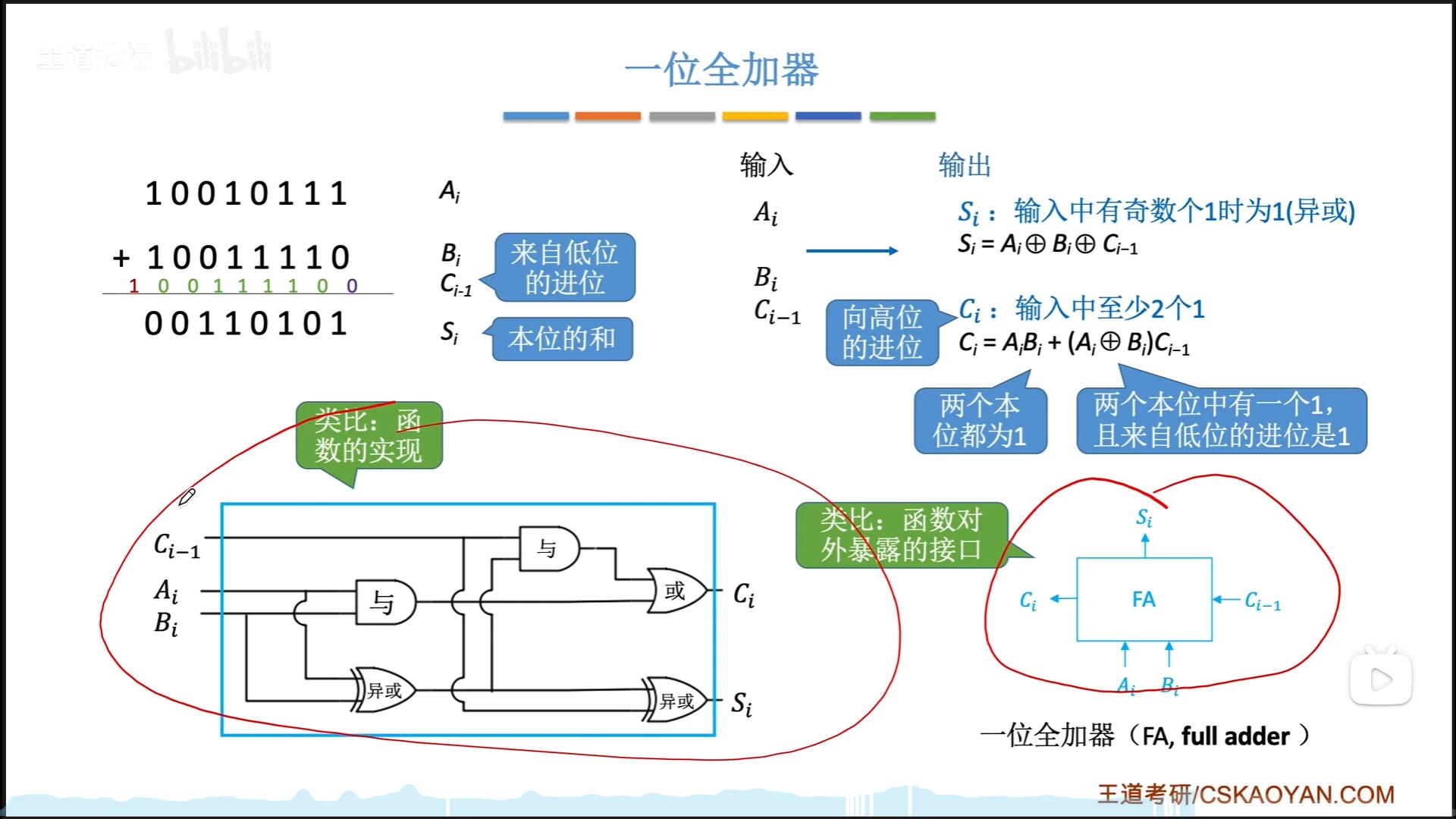

一位全加器

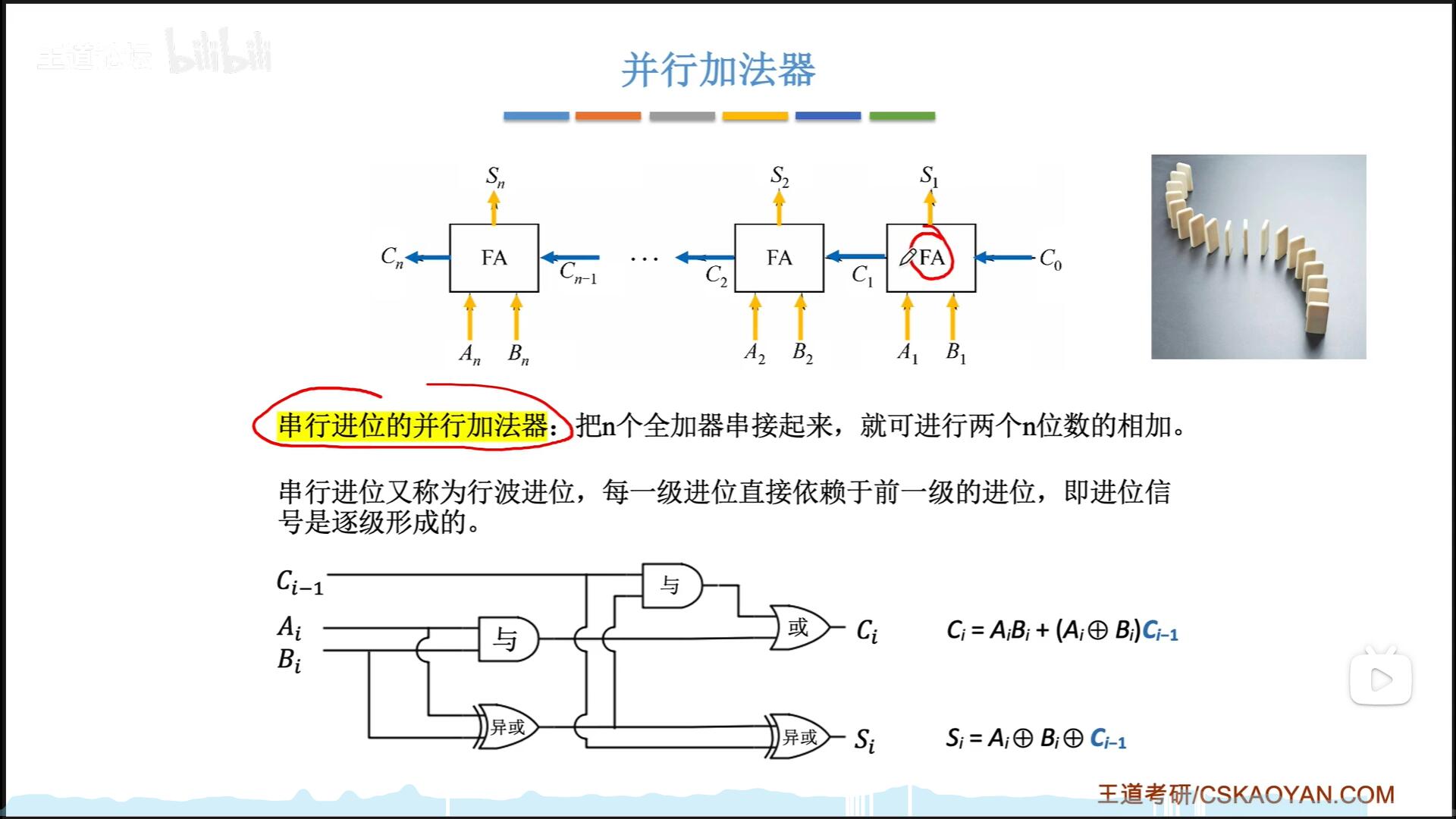

并行加法器

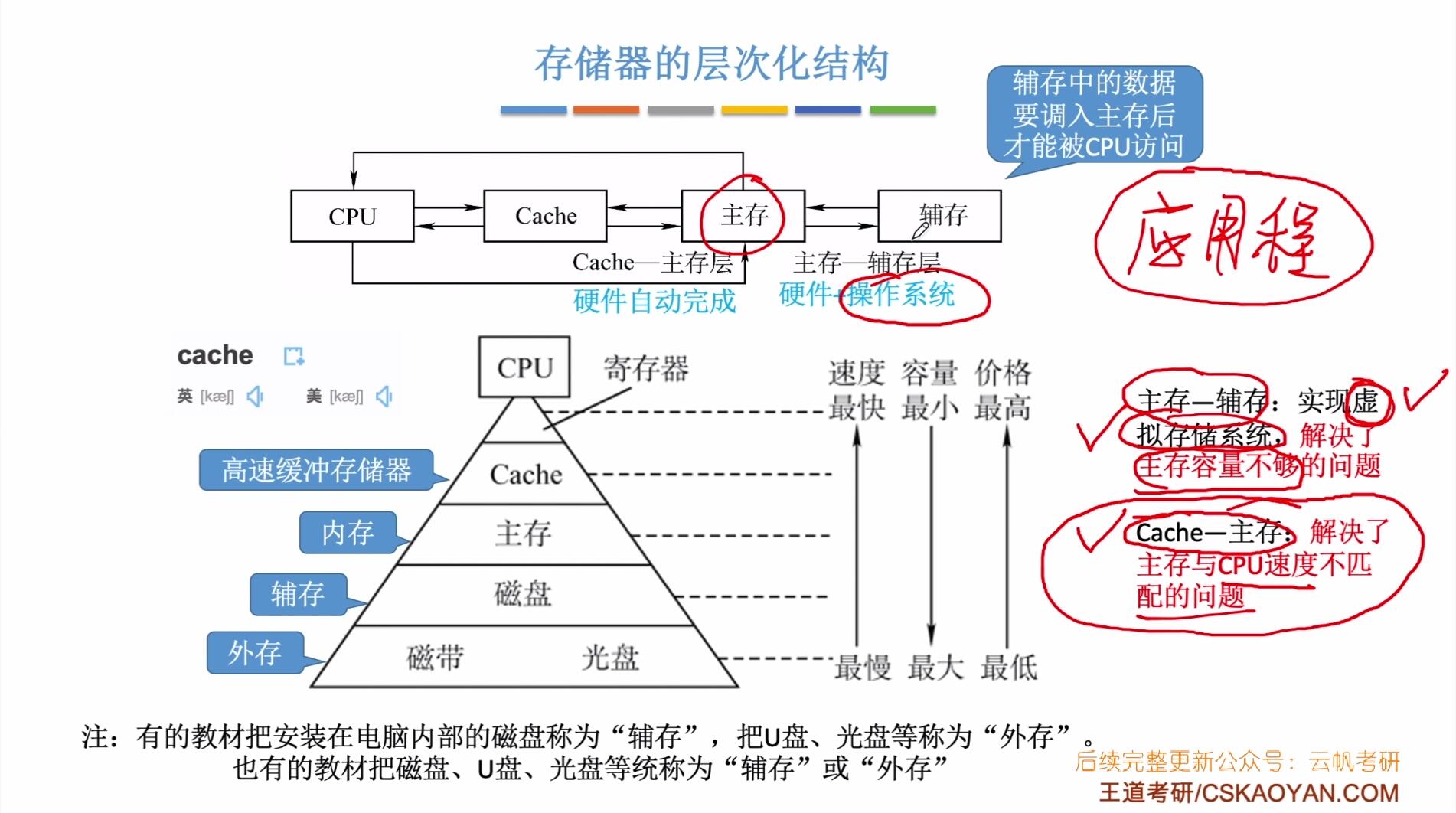

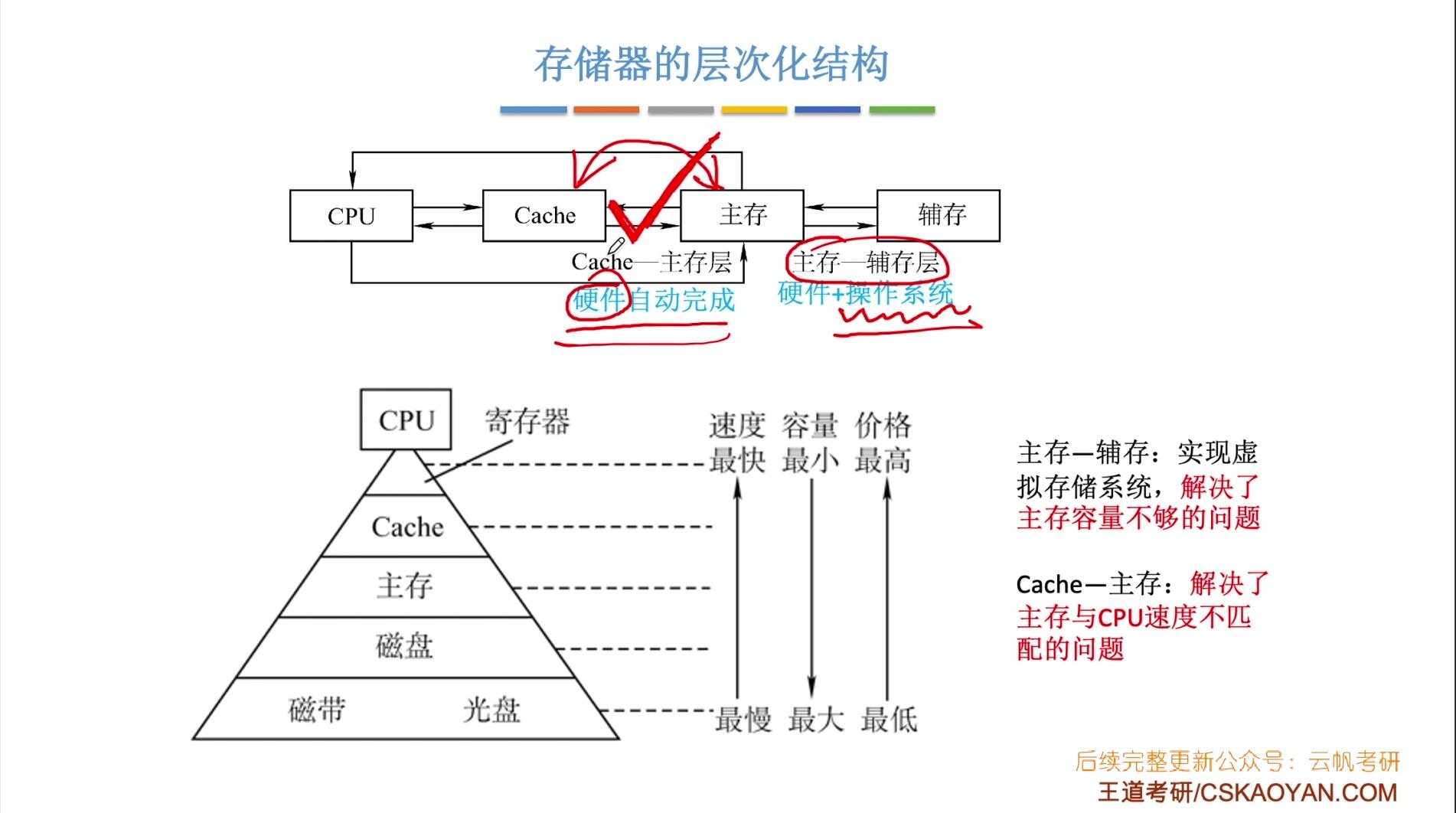

存储系统

存储系统的基本概念

存储介质:有半导体,磁性材料

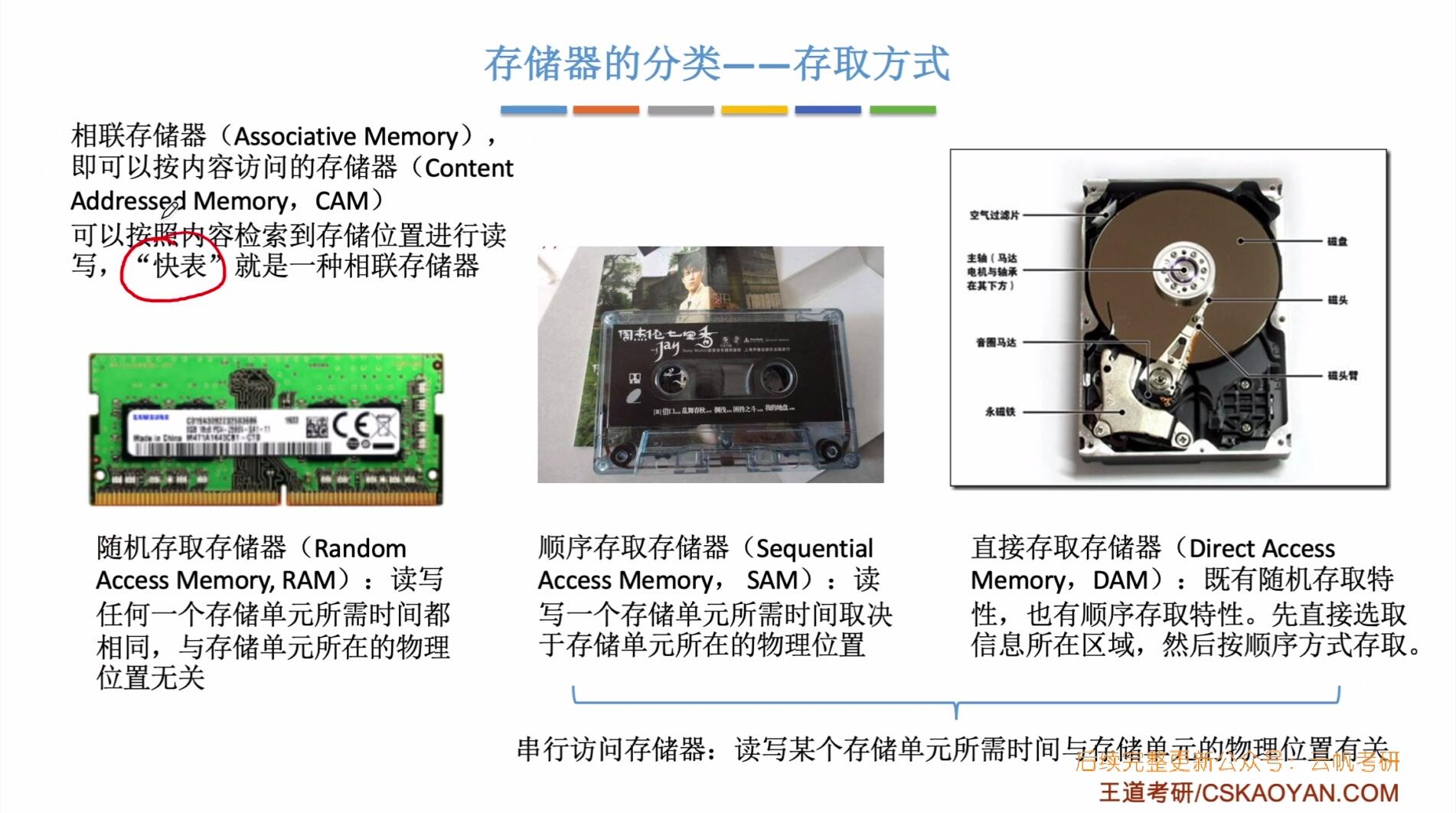

RAM:(RandomAccessMemory)随机存取存储器

SAM:顺序存取存储器

存储器的分类

存取方式

按内容与地址

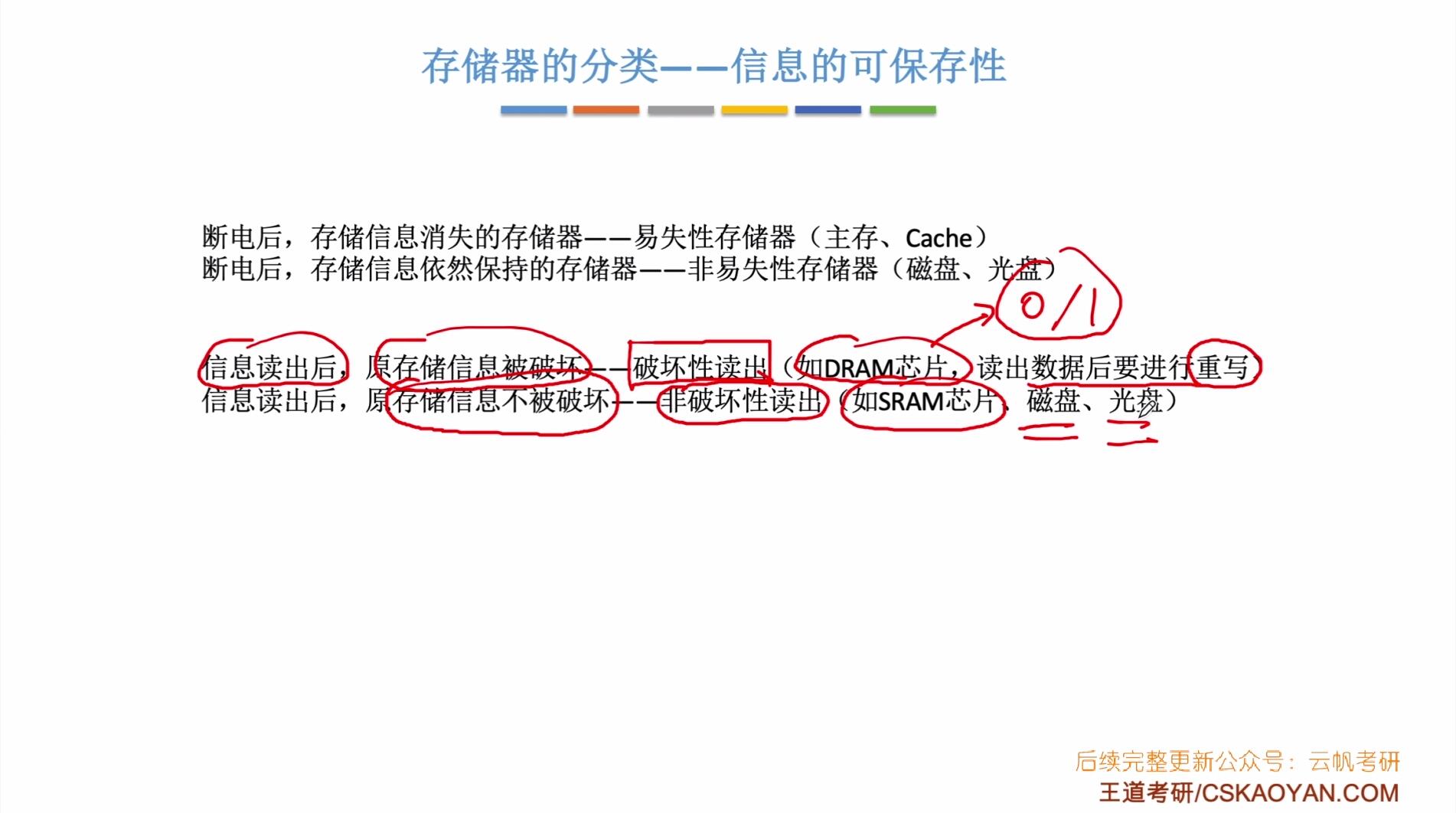

信息可保存性

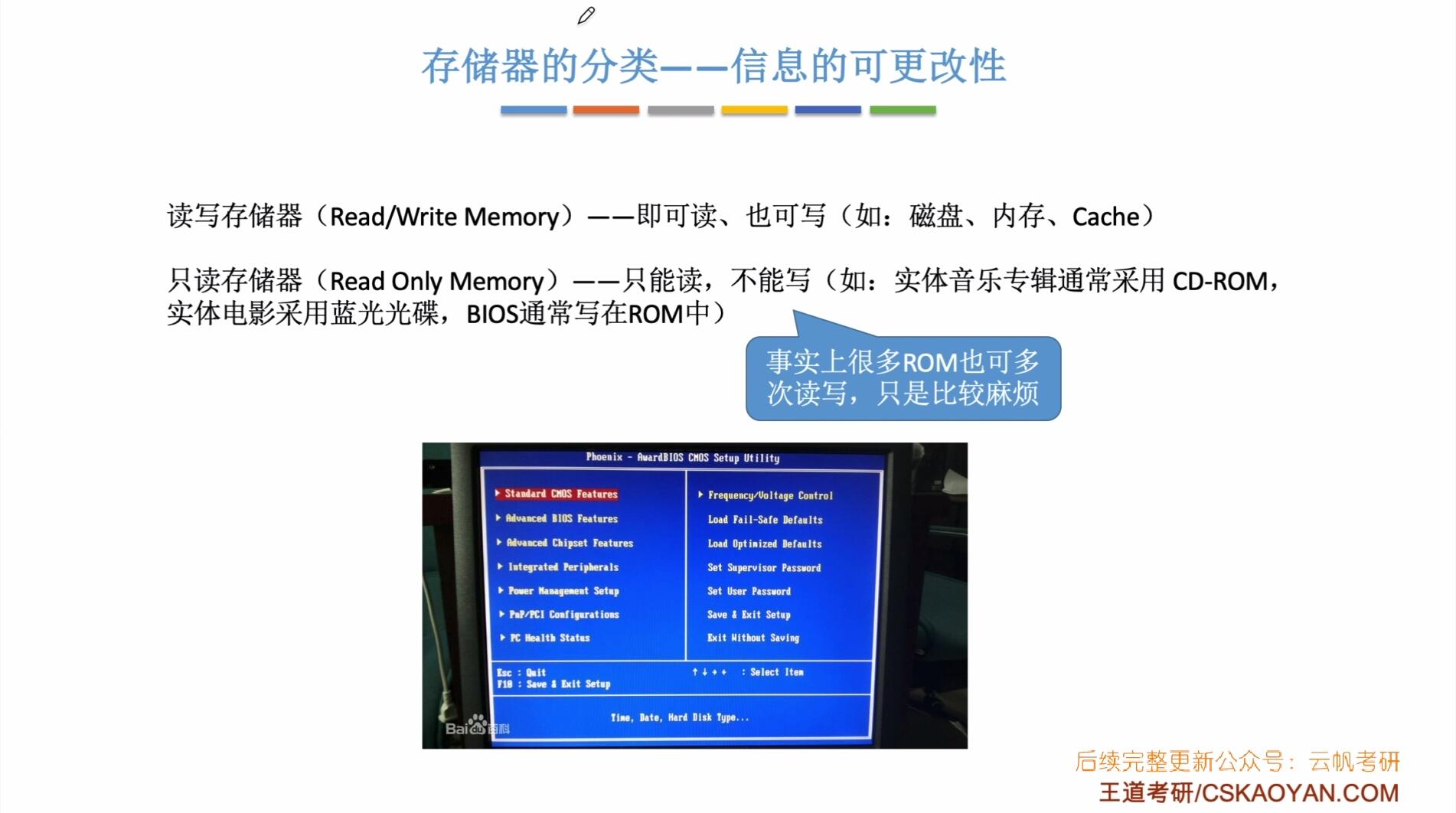

信息可更改性

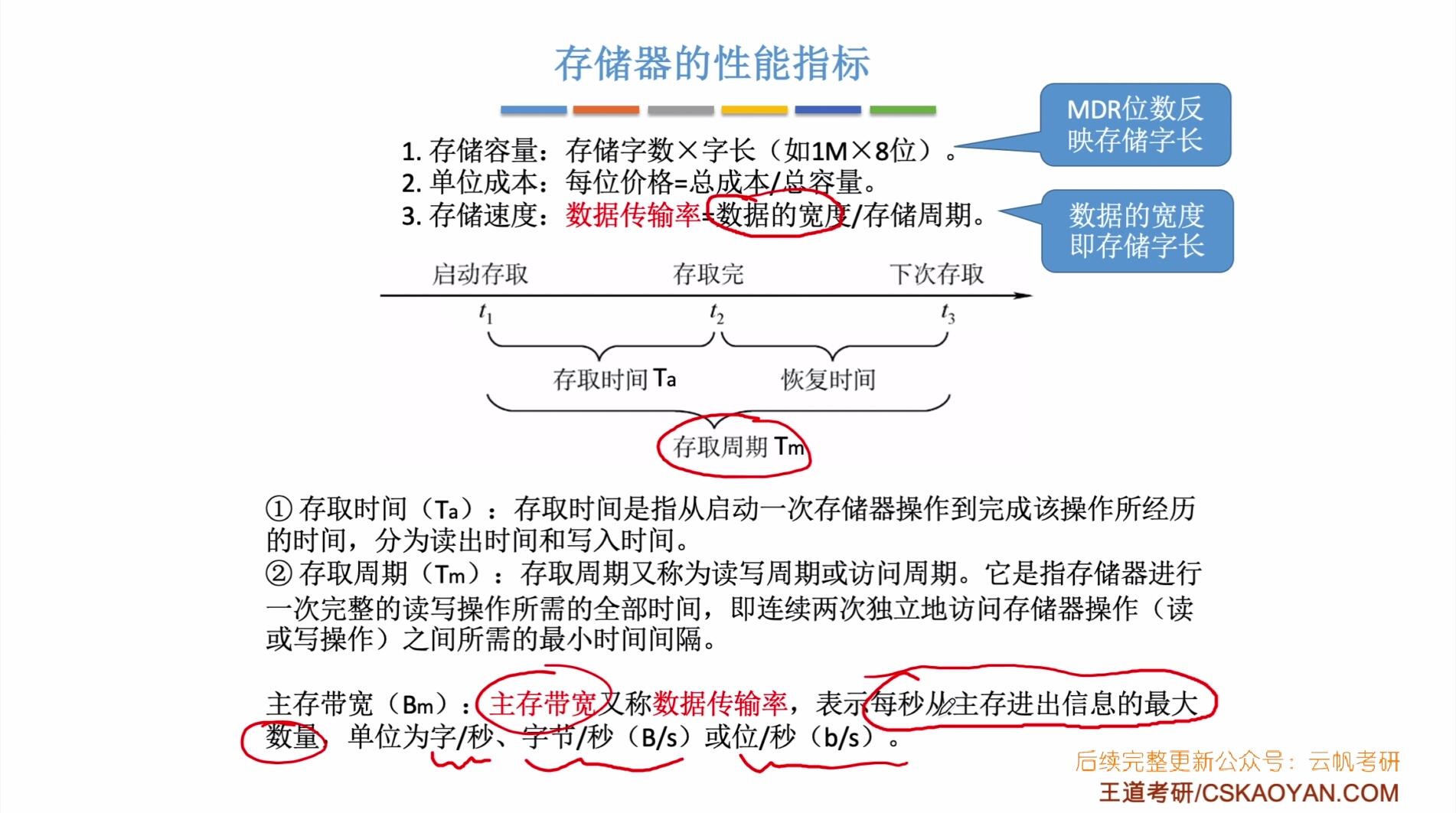

存储器性能指标

数据宽度即 存储字长即 MDR是计算机中的主存数据寄存器。它的位数就是字长

主存储器的基本组成

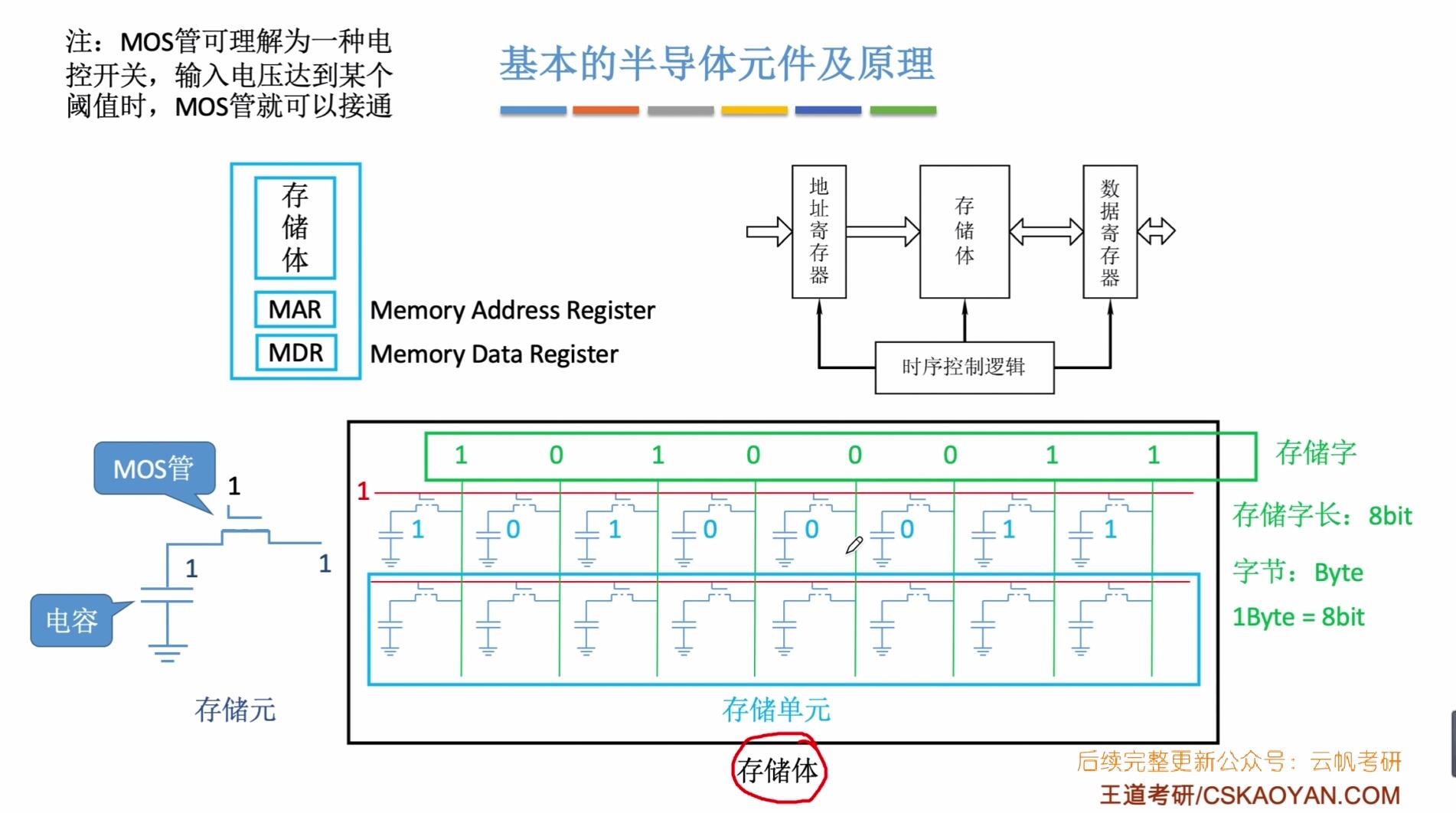

基本半导体元件及原理

MOS管电控开关,输入电压达到阈值,就接通,半导体原器件。

一个MOS管就是一位。

多个原器件组成存储单元,几个存储的位数就是存储字长。

多个存储单元构成存储体,也就是存储矩阵。

读写是一个存储字长,因为一个存储单元几个MOS管连在一起,一次读写就是所有的存储元。

存储字长与存储器有关

基本半导体元件及原理

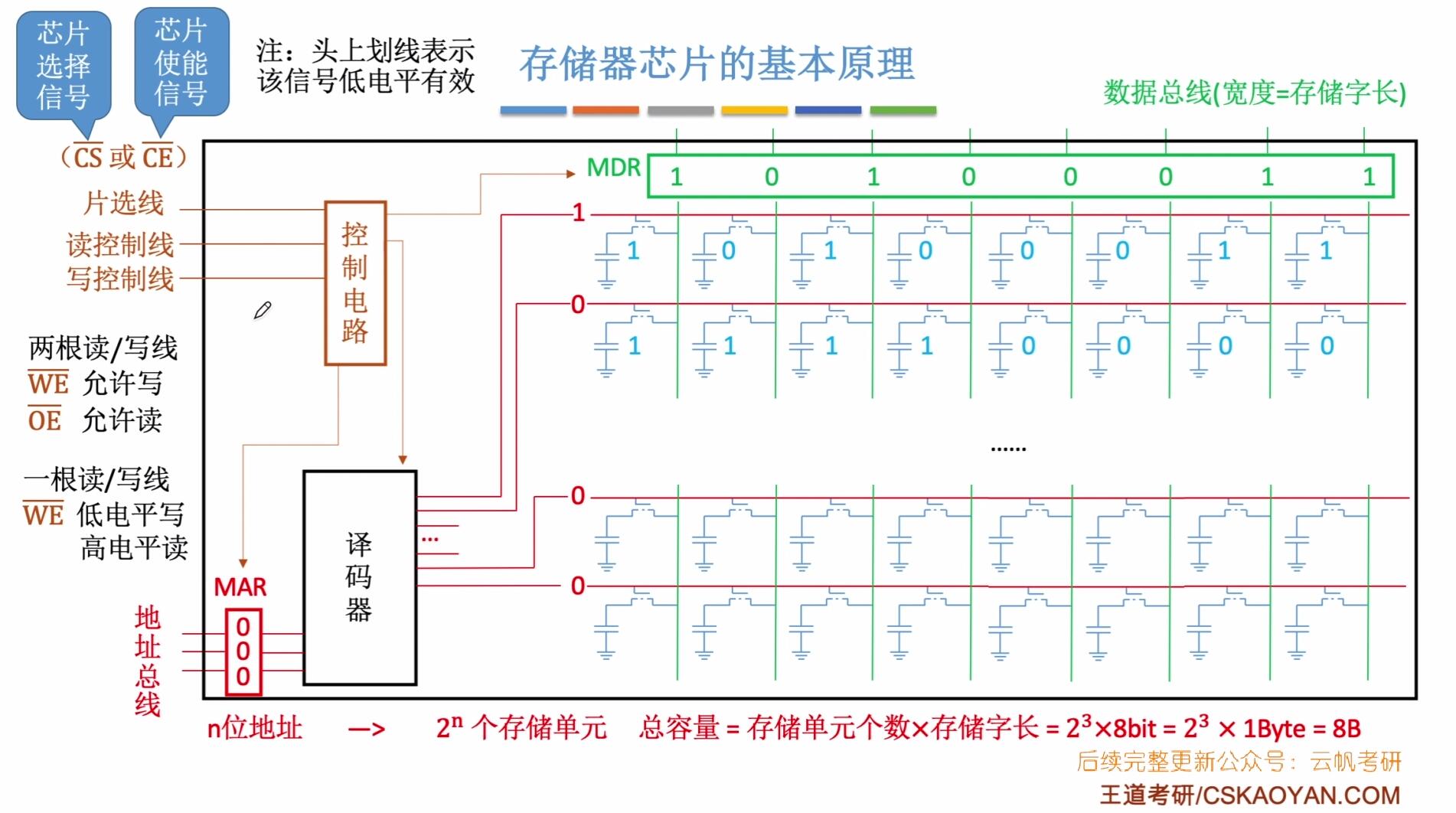

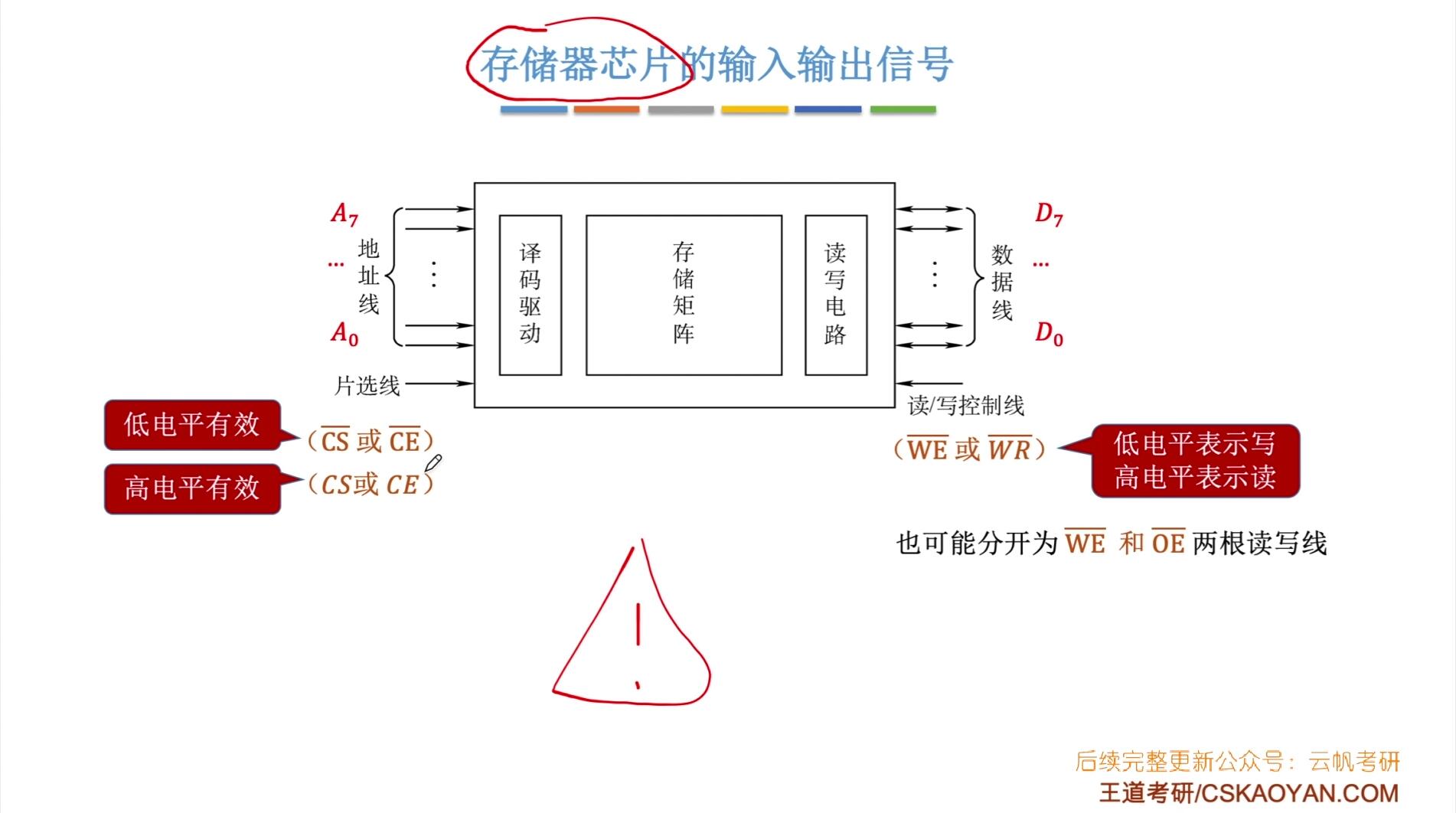

基本存储芯片的基本原理

头上划线表示该信号 低电平有效

控制电路:

片选线:

CS:芯片选择信号

CE:芯片使能信号 chip enable

读写控制线

两根读/写线

WE:允许写

OE:允许读

一根读写线

WE: 低电平 写,高电平 读

片选线:根据地址线访问指定存储单元

每根线都对应一个金属引脚

8K X 8bit:8K存储单元数量,后面是存储字长

寻址

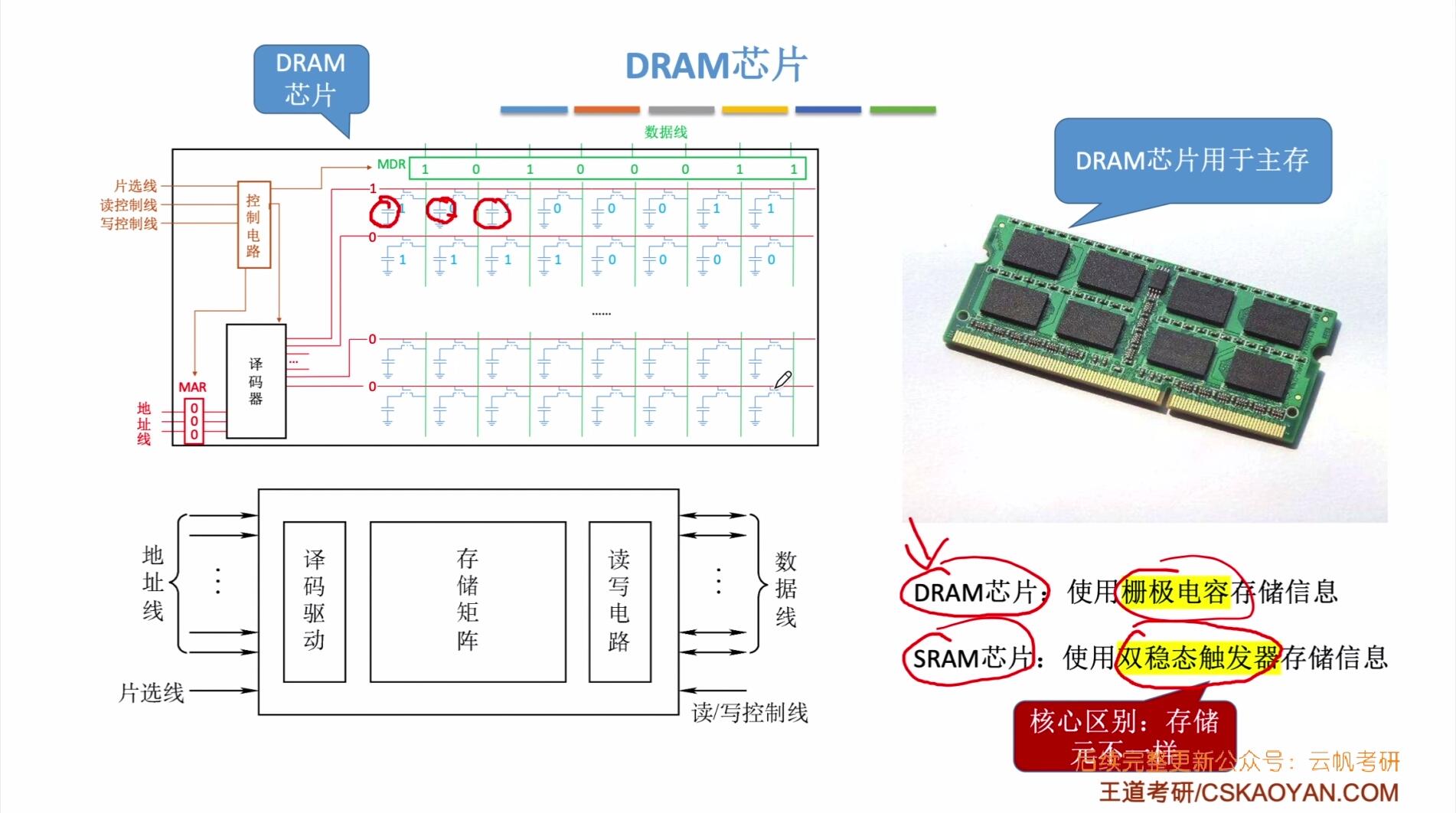

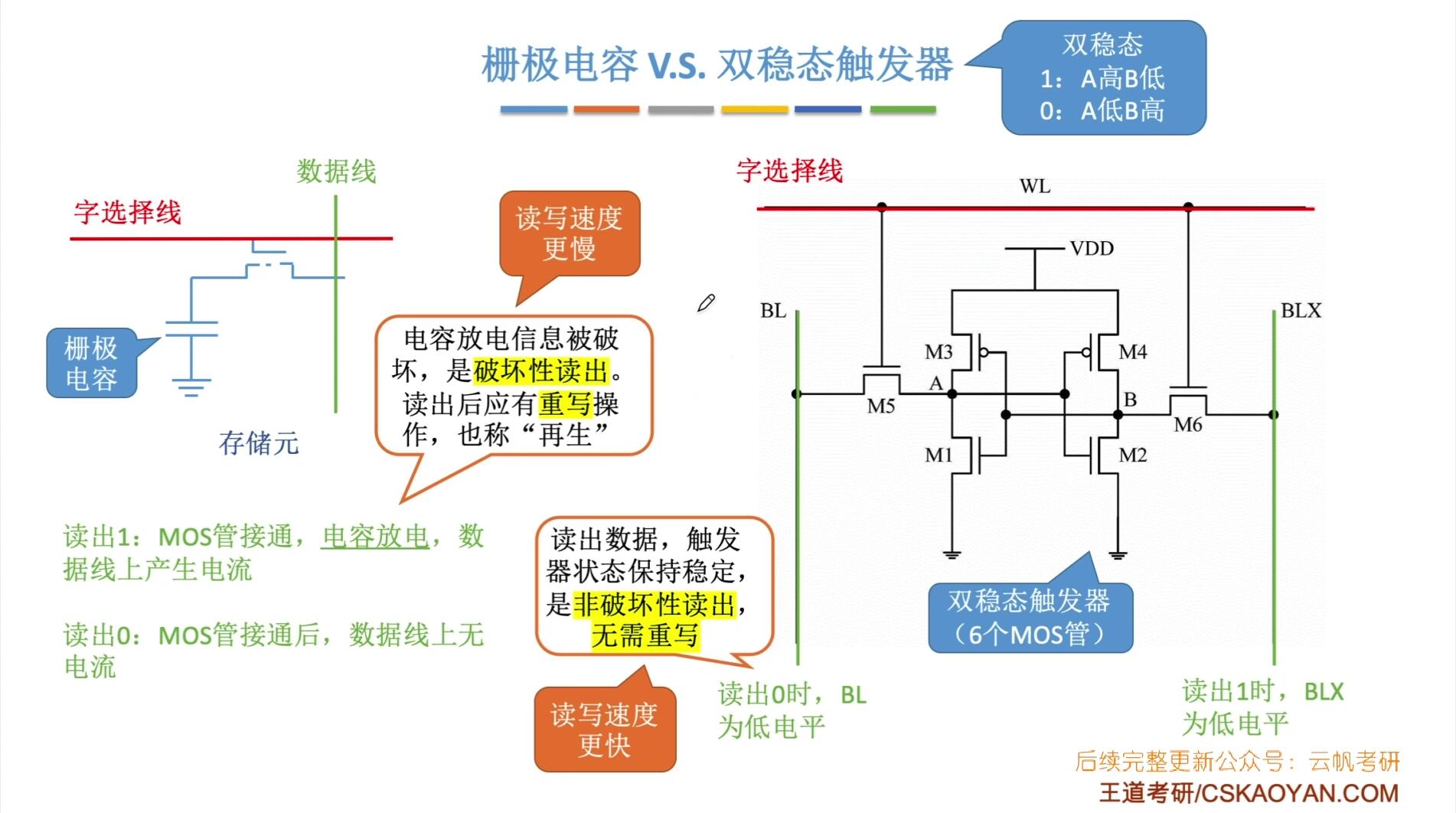

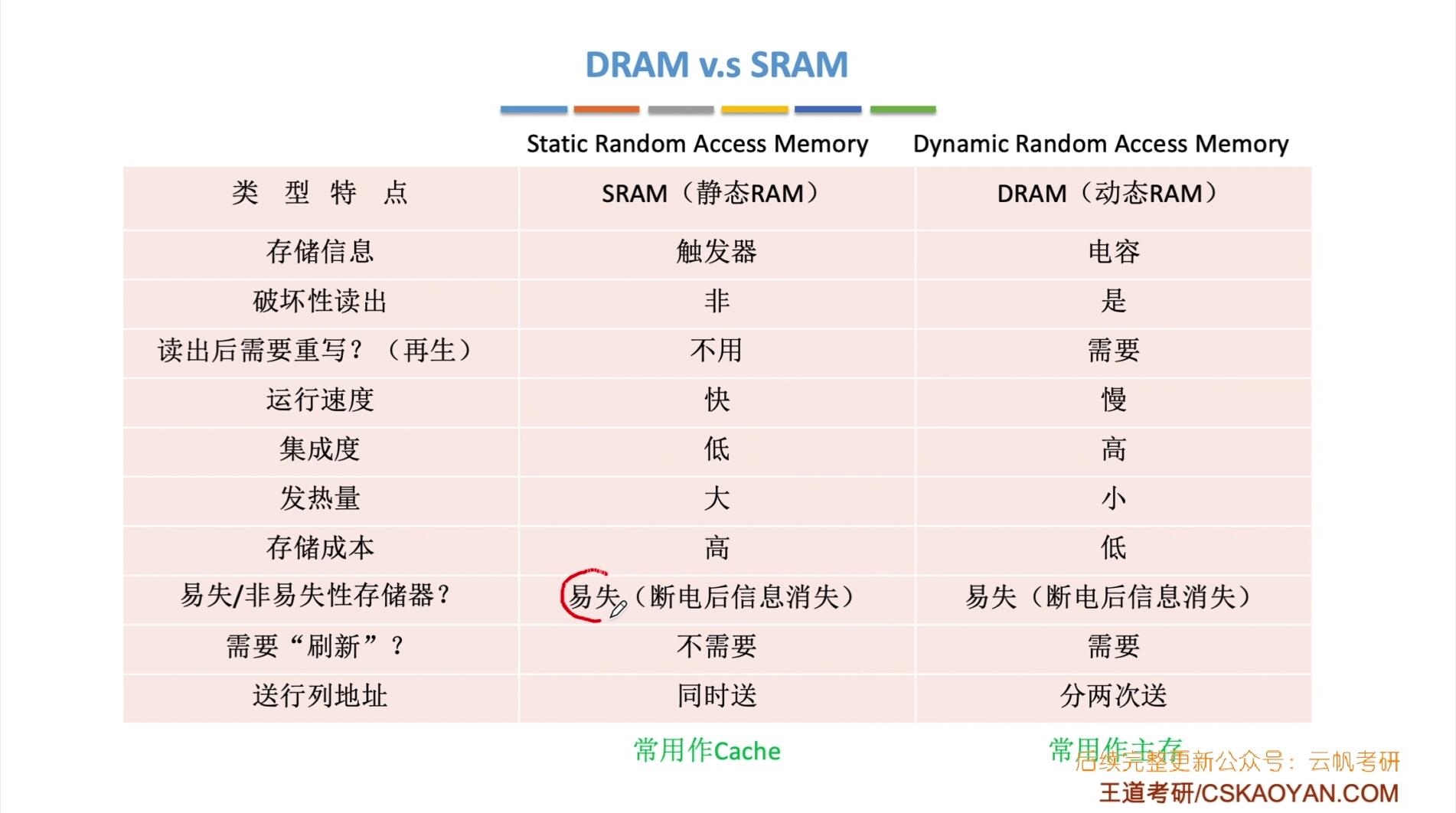

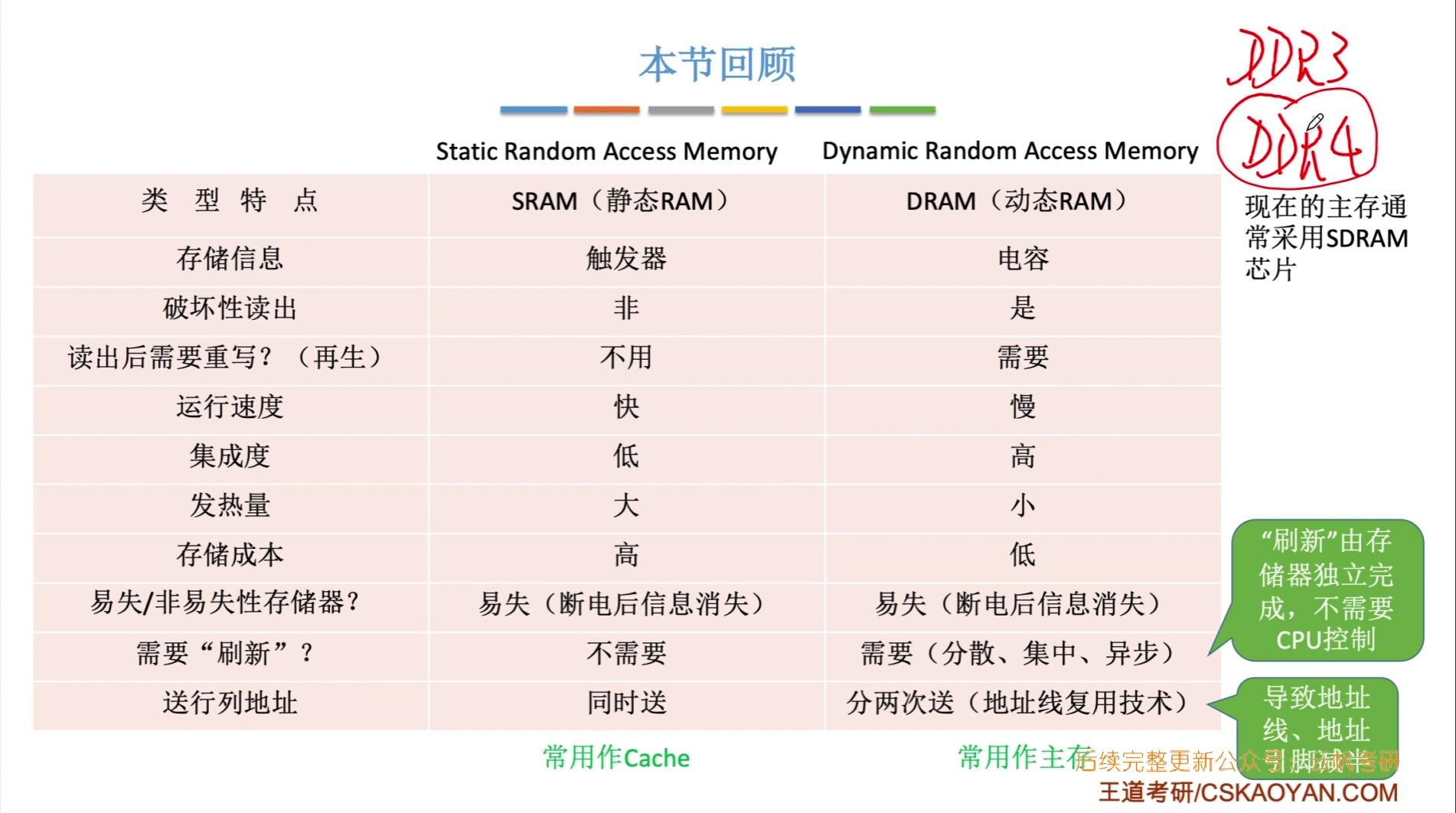

SRAM&DRAM

DRAM:电容存储信息

SRAM:双稳态触发器存储信息

栅极电容:

读出1:MOS管接通后,电容放电,数据线产生电流

读出0:MOS管接通后,数据线上 无电流

双稳态触发器:6个MOS管组成

DRAM:

1:A高B低

0:A低B高

电容放电信息被破坏,读出后应重写

二者对比

SRAM:用作cache

DRAM:用作主存

DRAM:需要刷新:电容电荷会消失

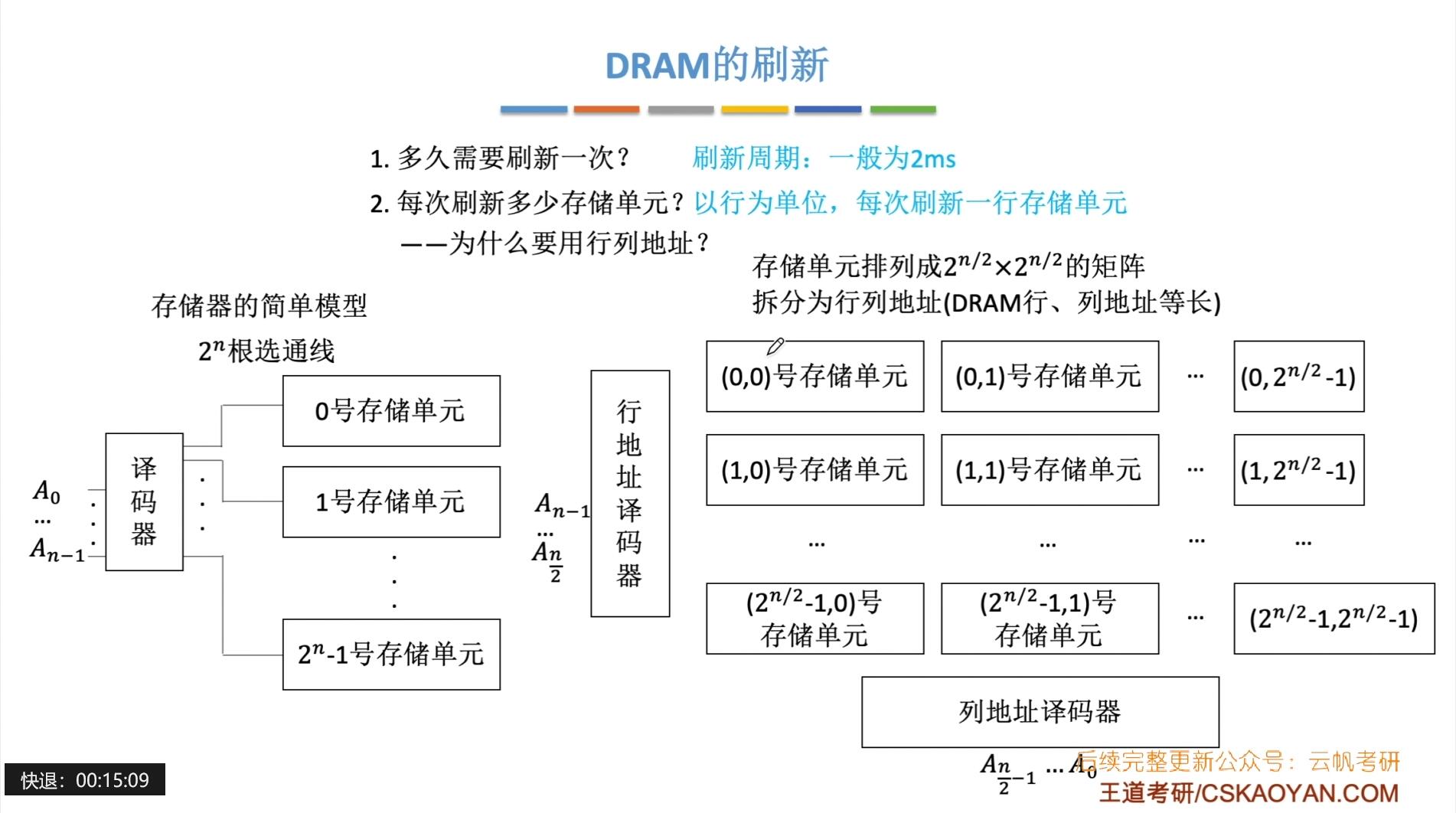

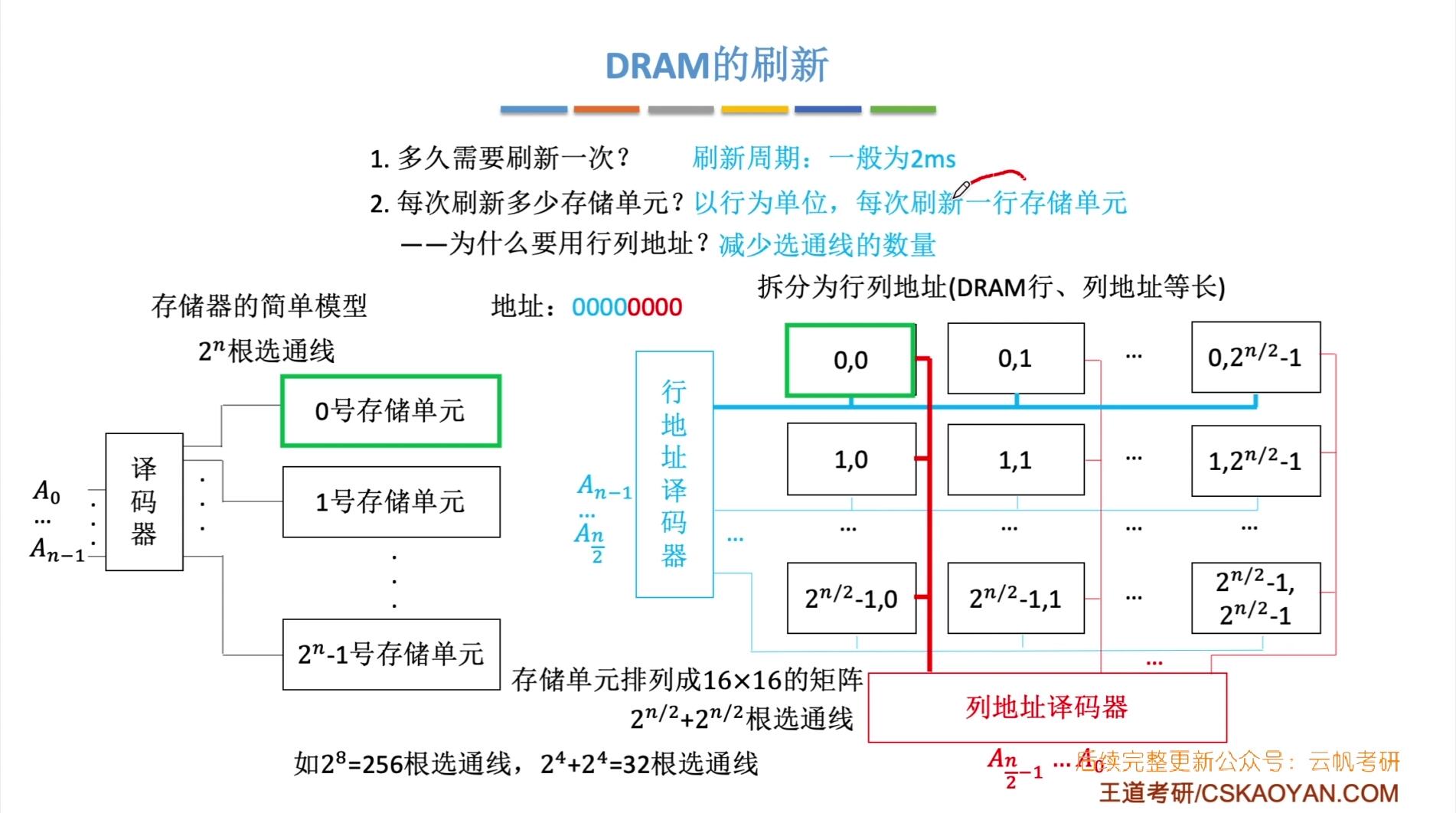

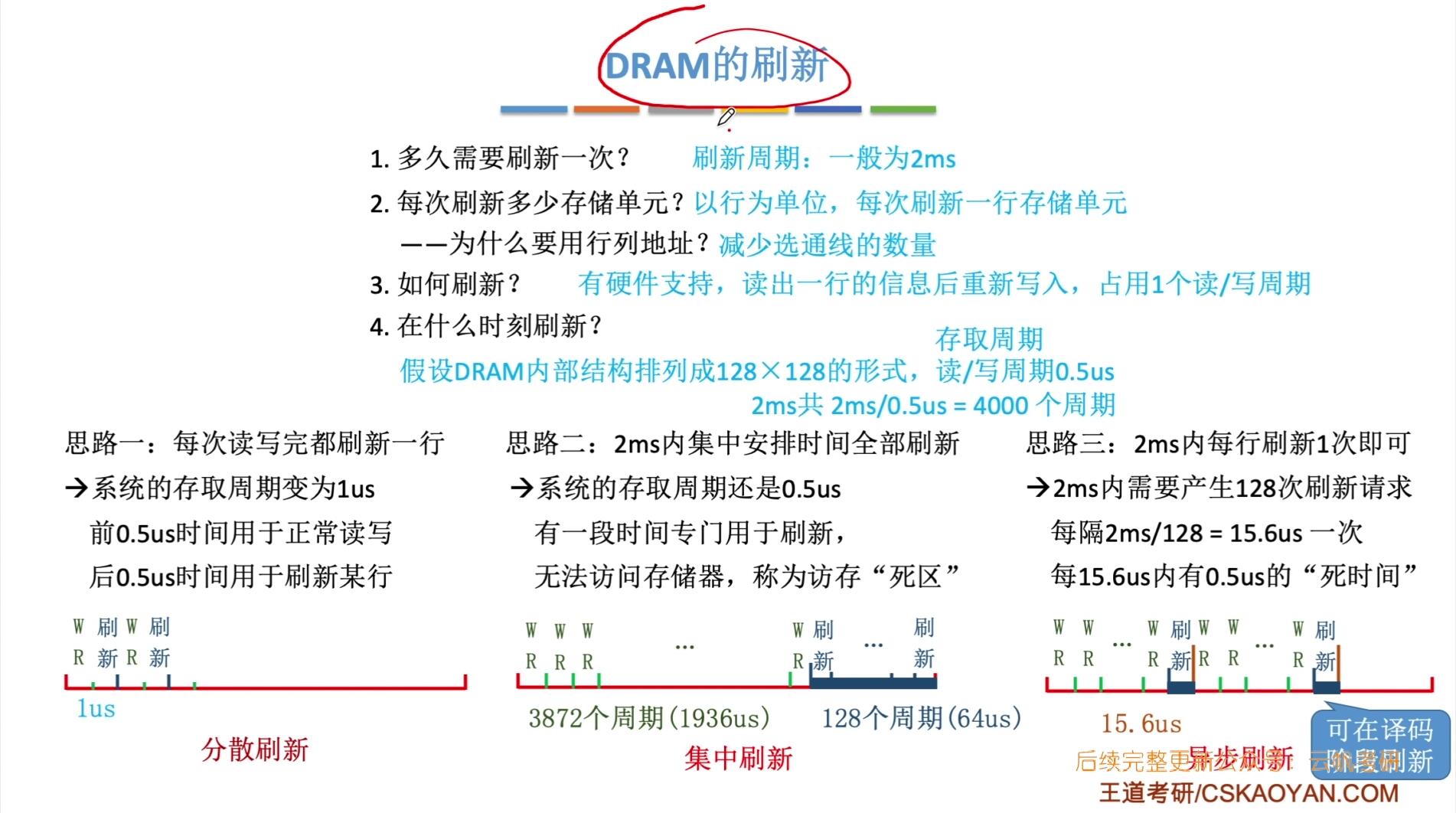

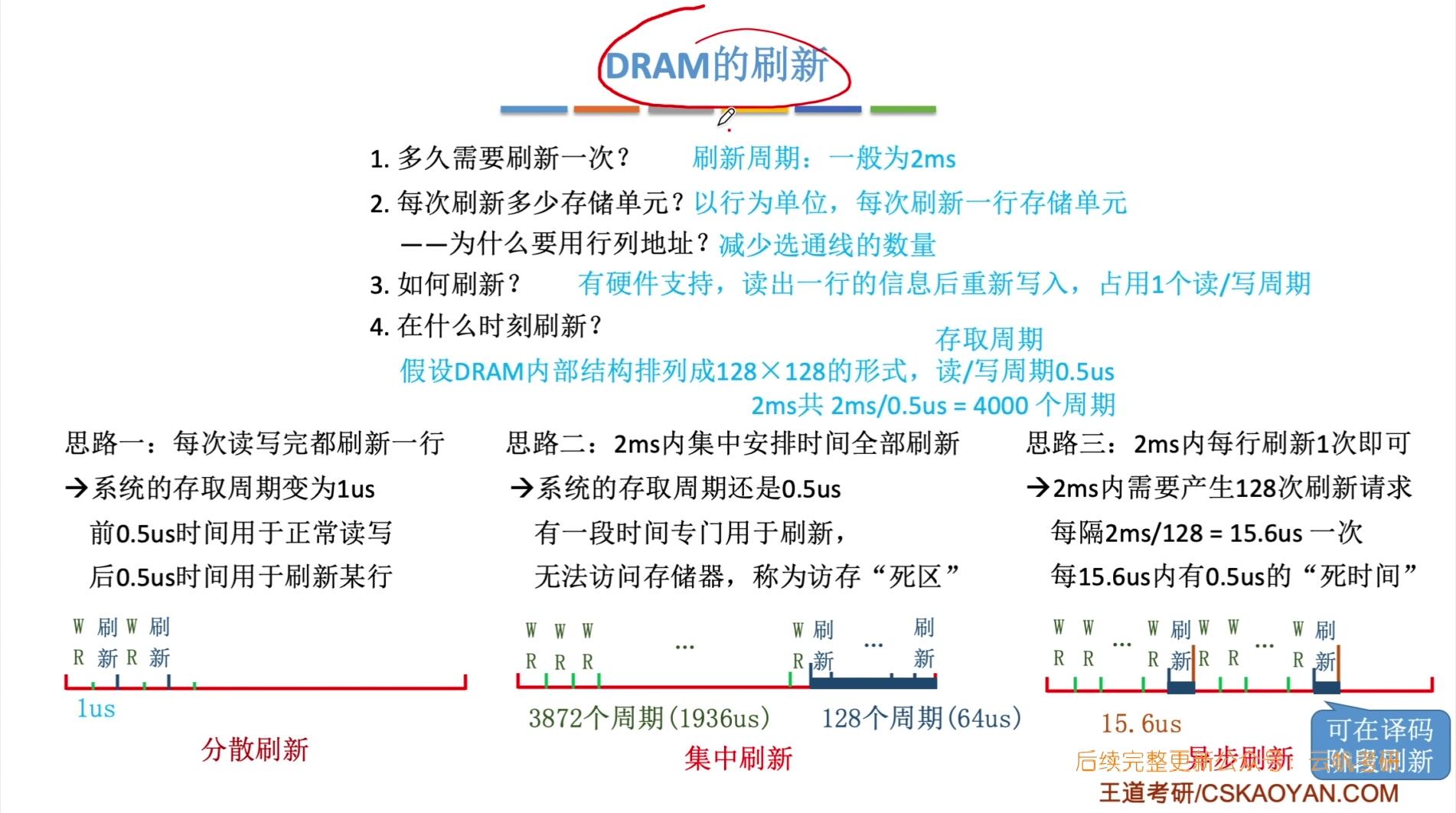

DRAM刷新

行列地址:减少选通器的数量

8根地址线:2^8 根选通线

如果采用行列地址:2^4+2 ^ 4根选通线

刷新方式

总结

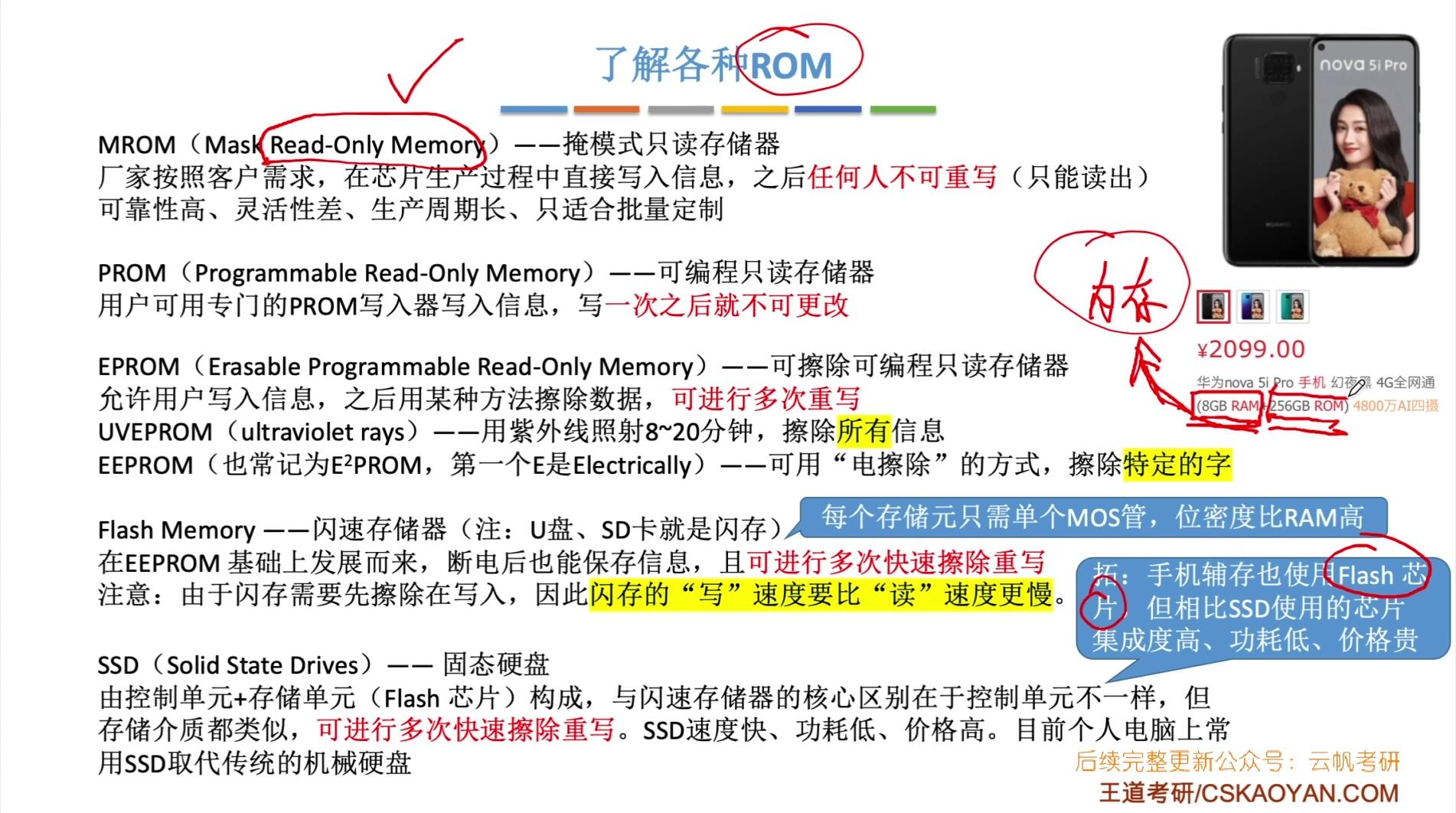

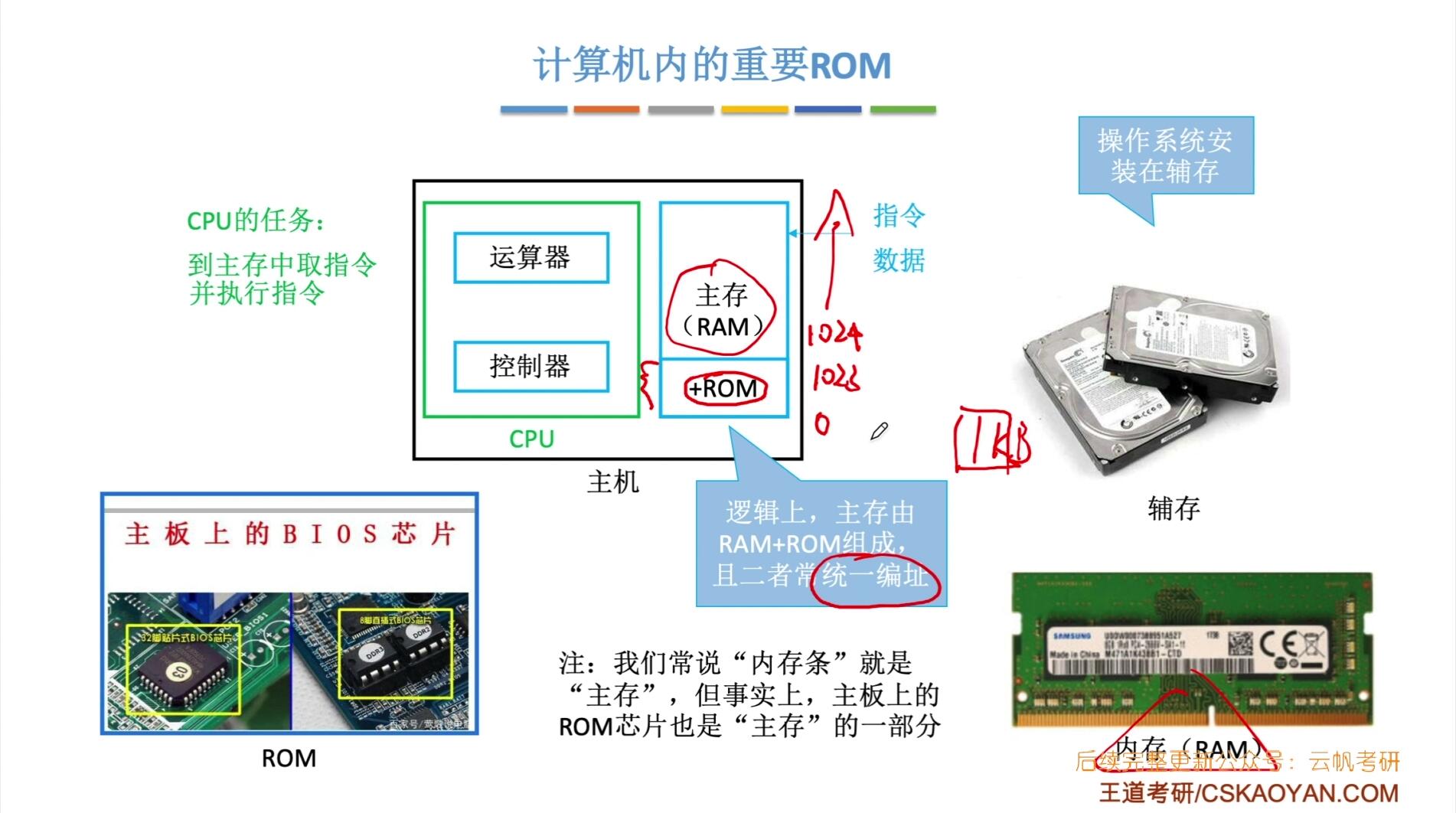

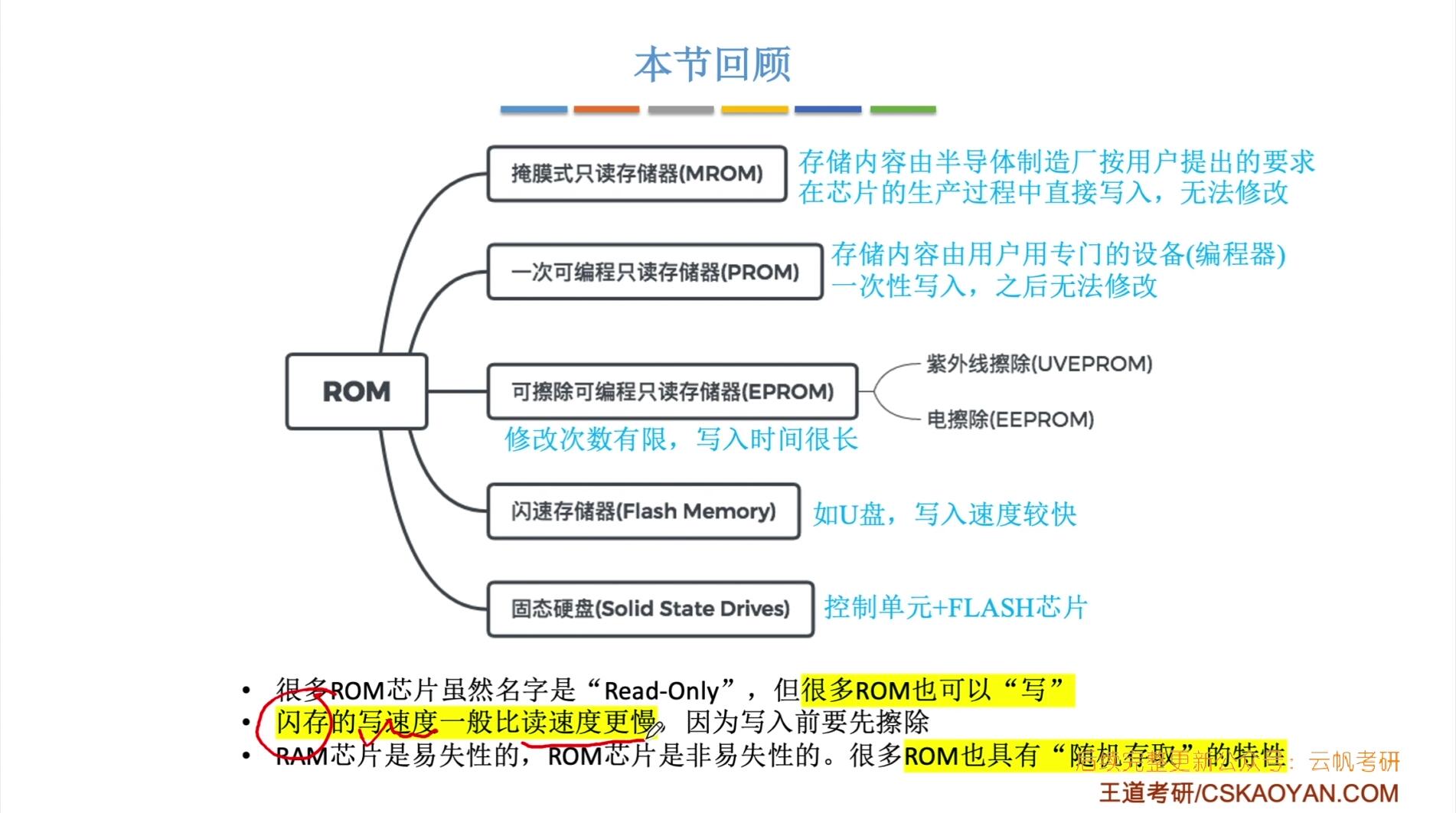

ROM

RAM:随机存取的芯片

易失性,断电后数据消失

ROM:

非易失性,断电数据不会丢失

MROM(Mask Read-Only Memory)-掩膜只读存储器

PROM(Programmable Read-Only Memory)-可编程(写一次)

EPROM(Erasable Programmable ReadOnly)-可擦除可编程只读存储器

FlashMemory–闪速存储器(U盘,SD卡就是闪存)

E2PROM:断电也能保存信息,先擦除再写入,读比写快

SSD(solid state Drives)-固态硬盘

RAM:内存

ROM:辅存

BIOS:重要的ROM:开机时读取系统和指令到内存,内存条就是内存,主板上ROM也是主存的一部分。

ROM:也具有随机存取的特性,并不与RAM完全对立

RAM:具有易失性

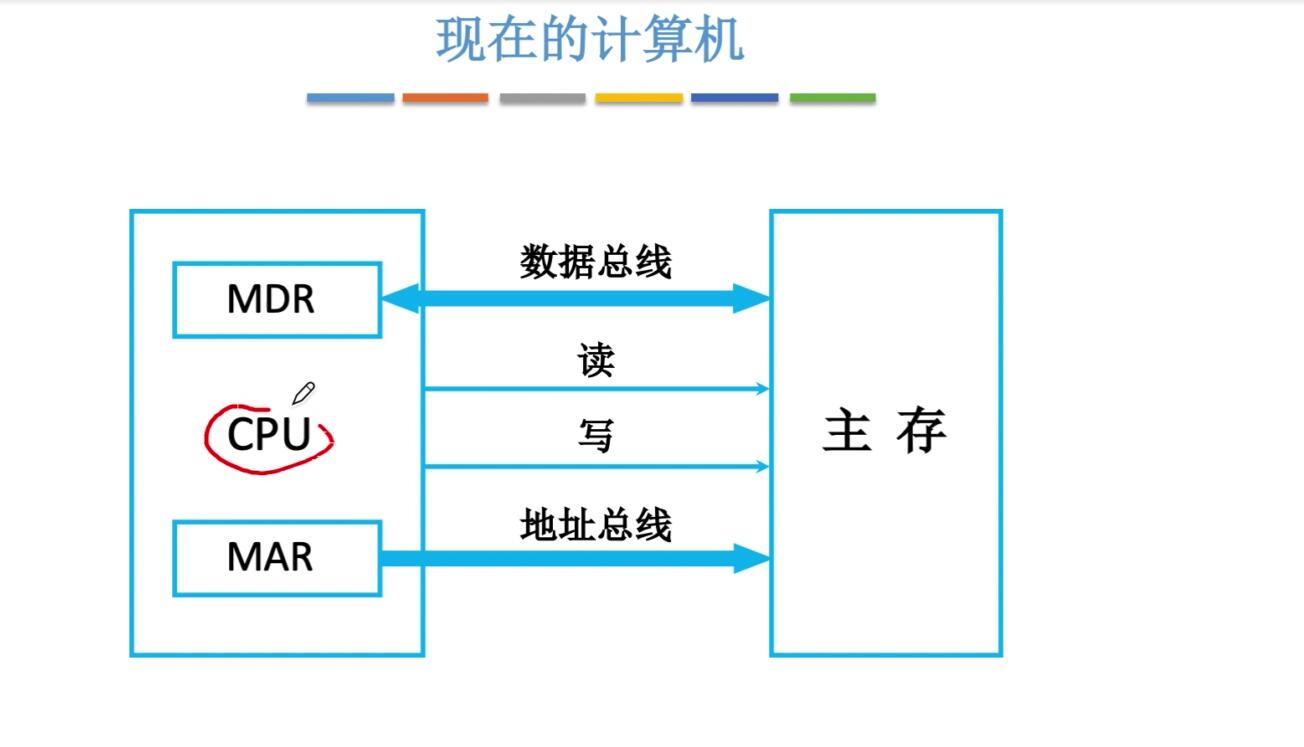

主存储器与CPU的连接

数据总线(宽度=存储字长)

单存储芯片与CPU的连接

常见符号

CS/CE:片选信号,上面有 —:代表低电平有效

WE/WR:读写控制线

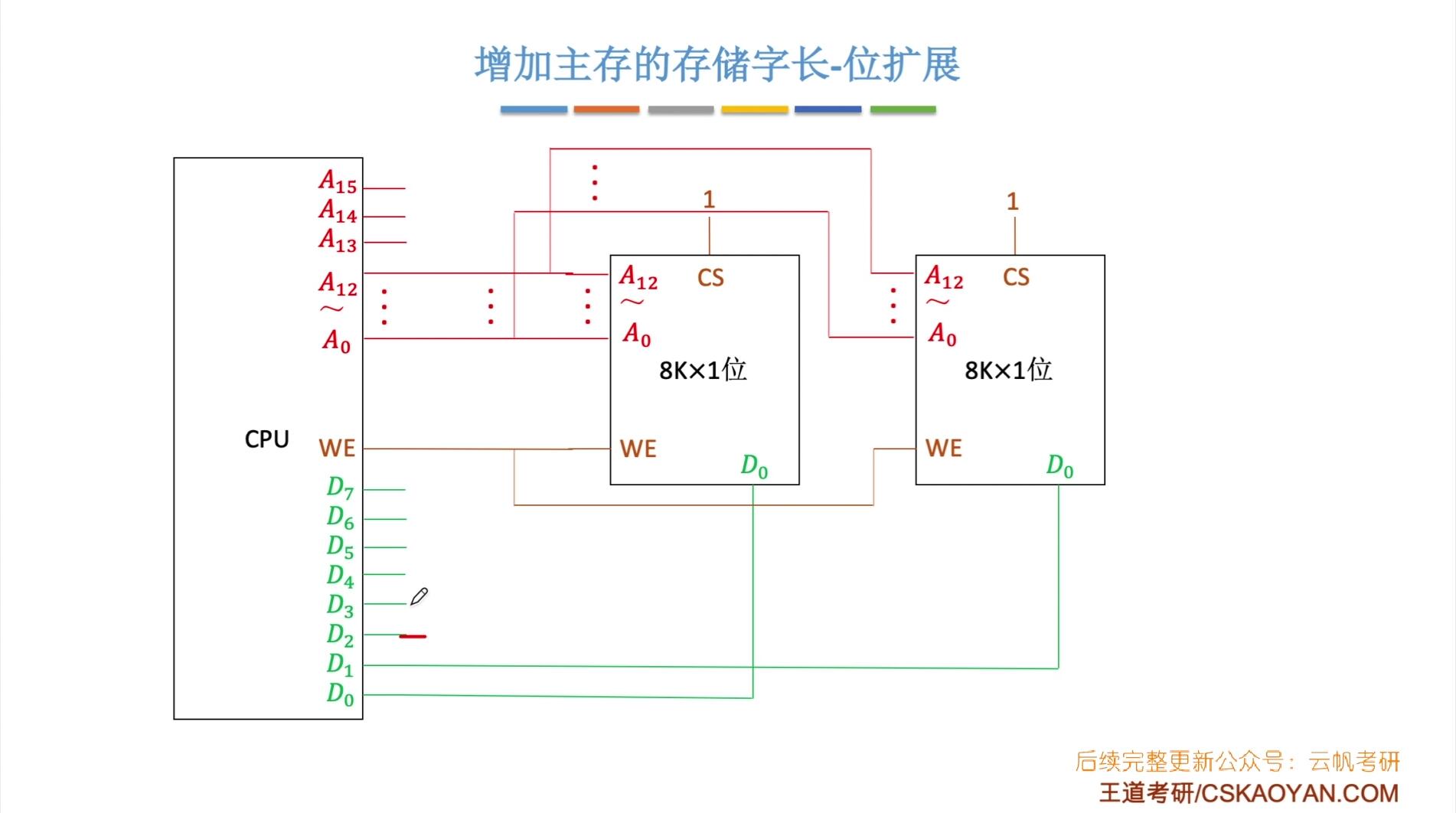

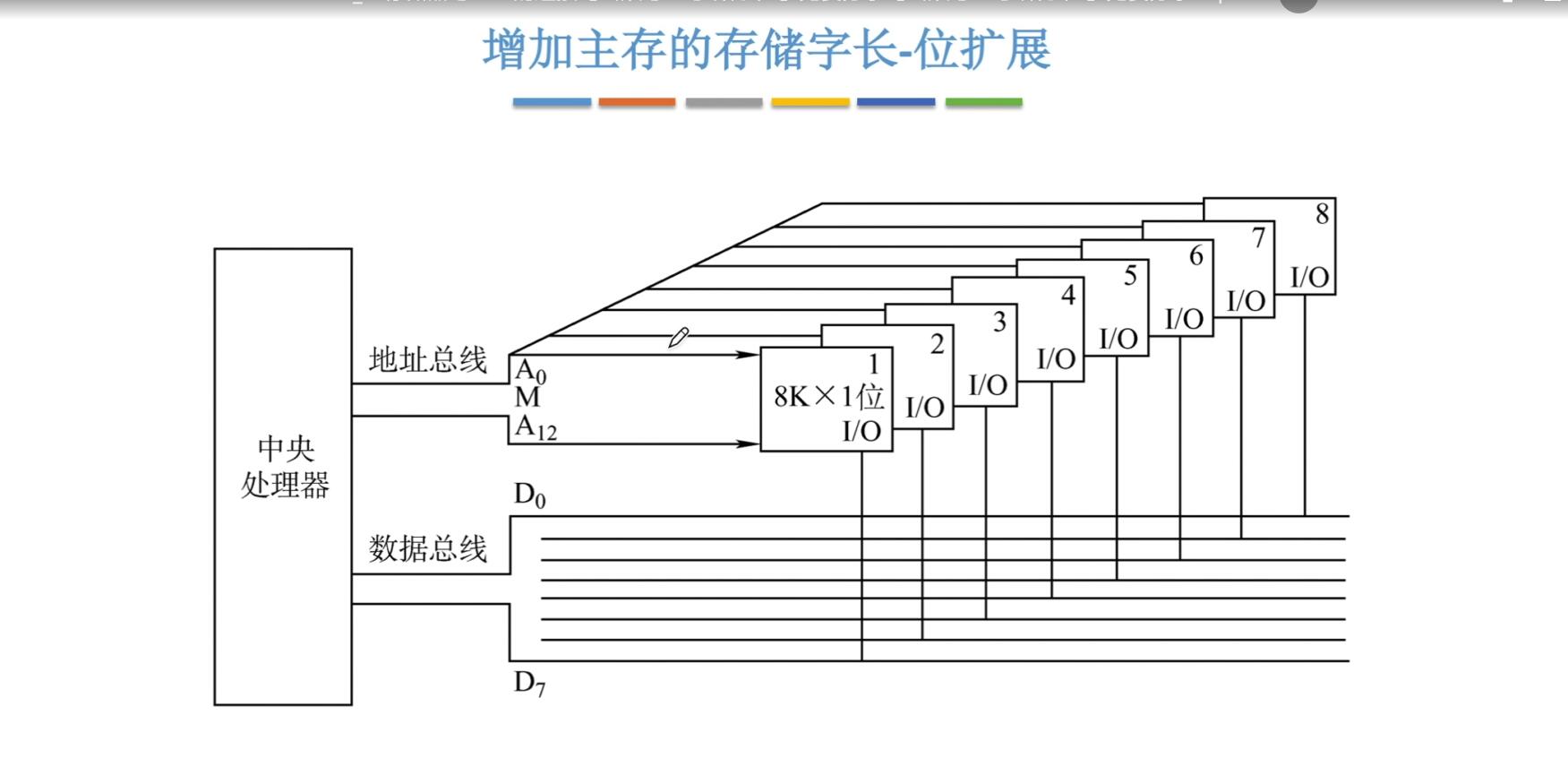

增加主存的存储字长-位拓展

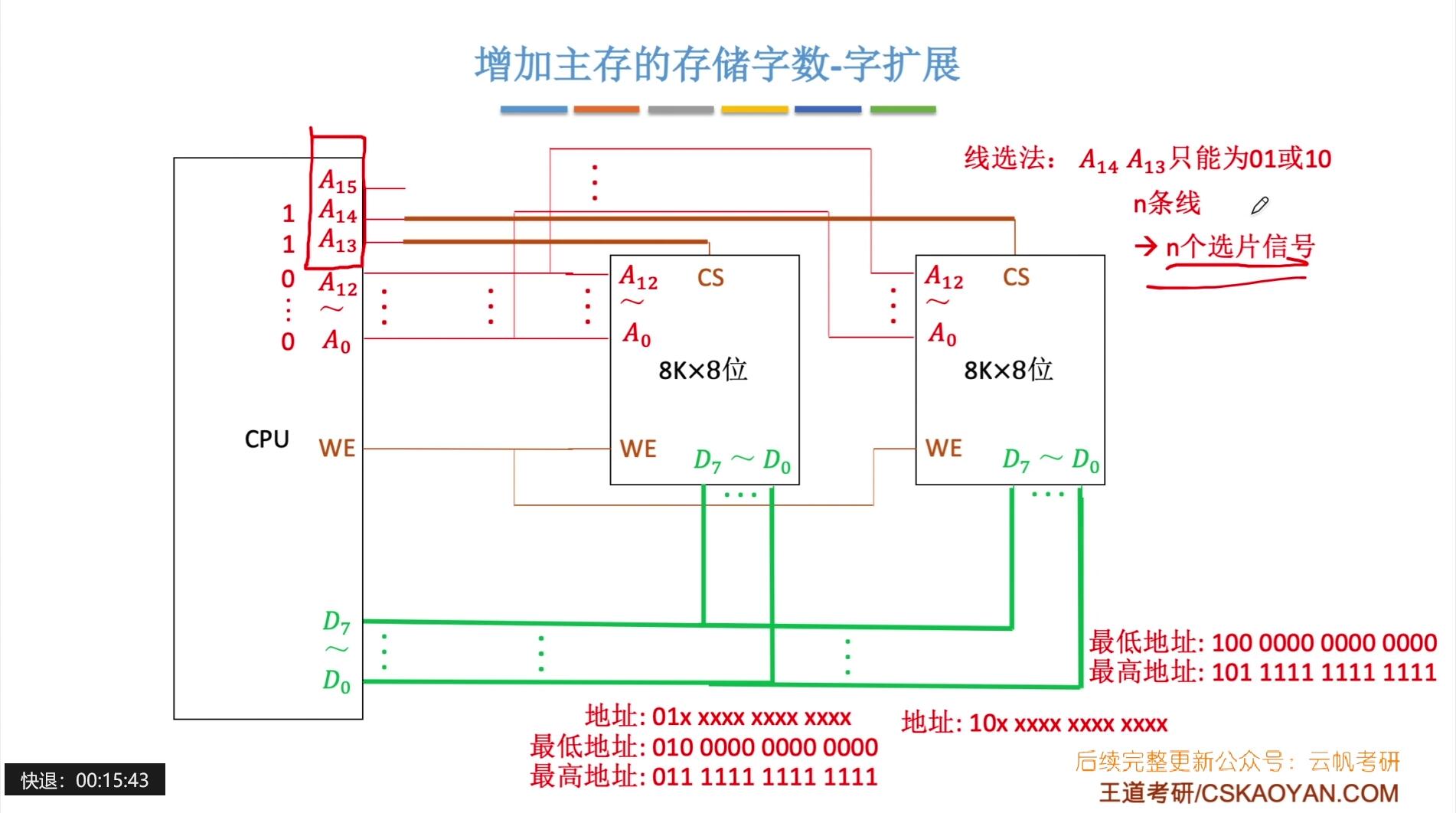

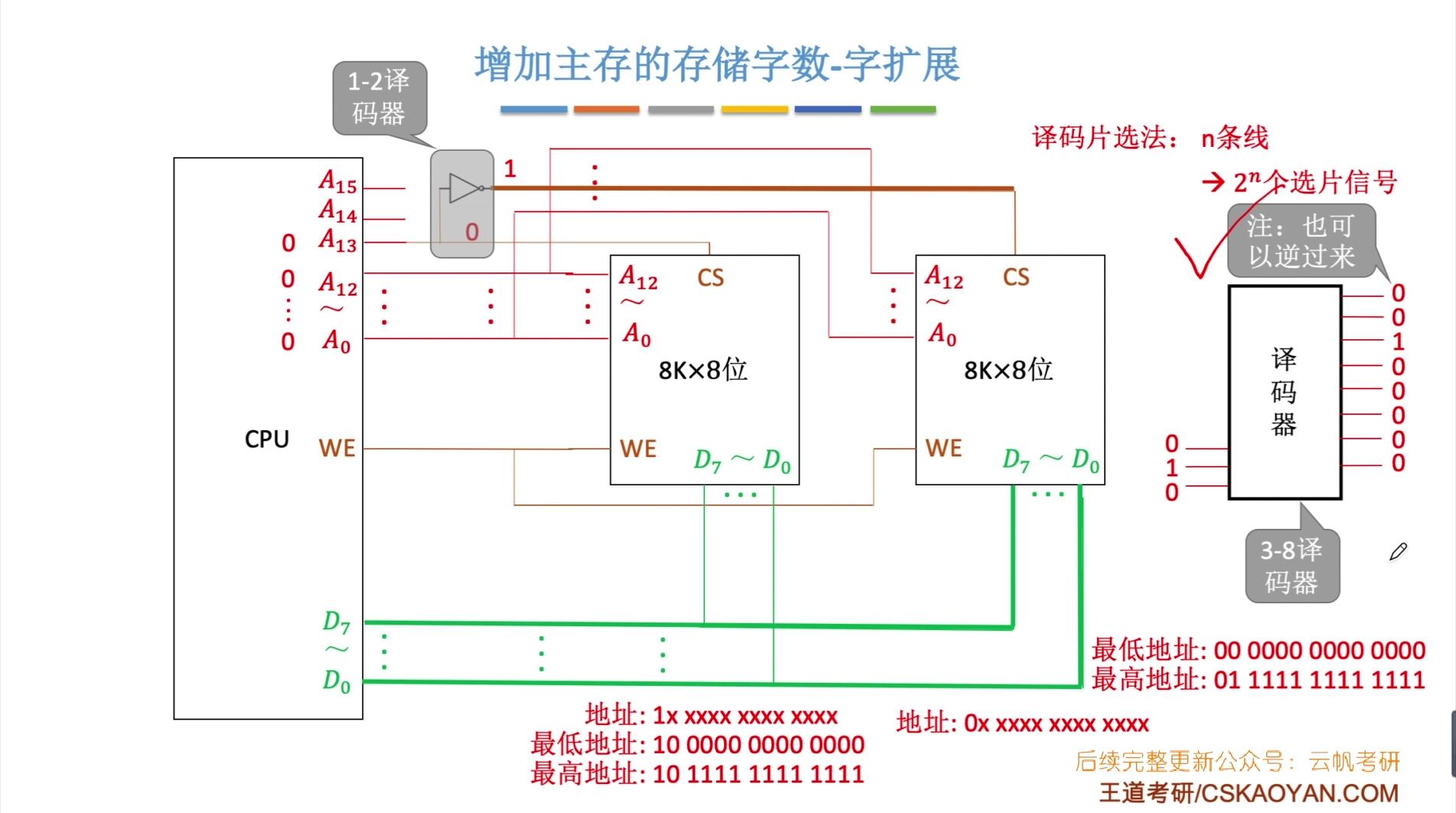

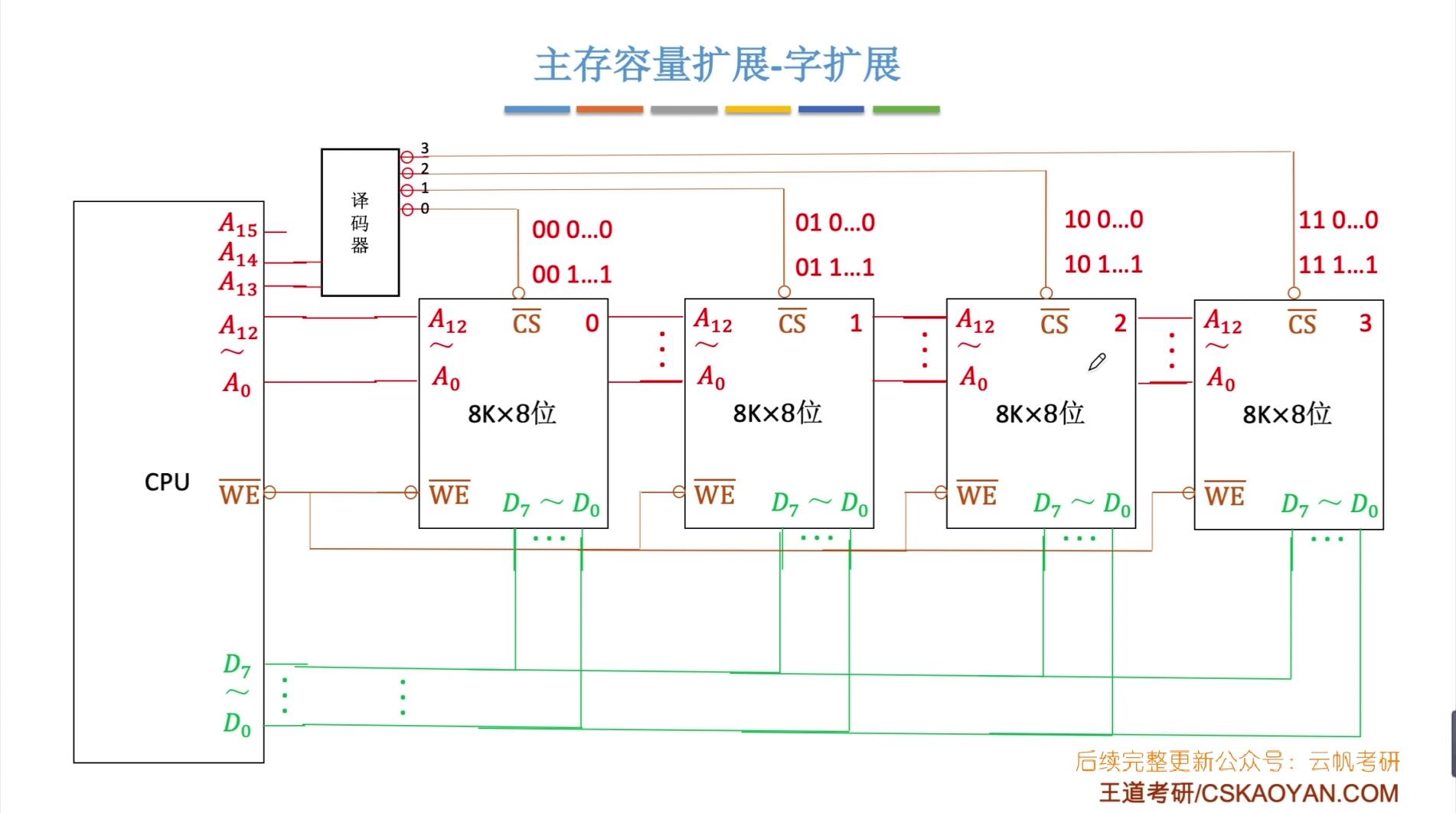

增加主存的存储字数-字扩展

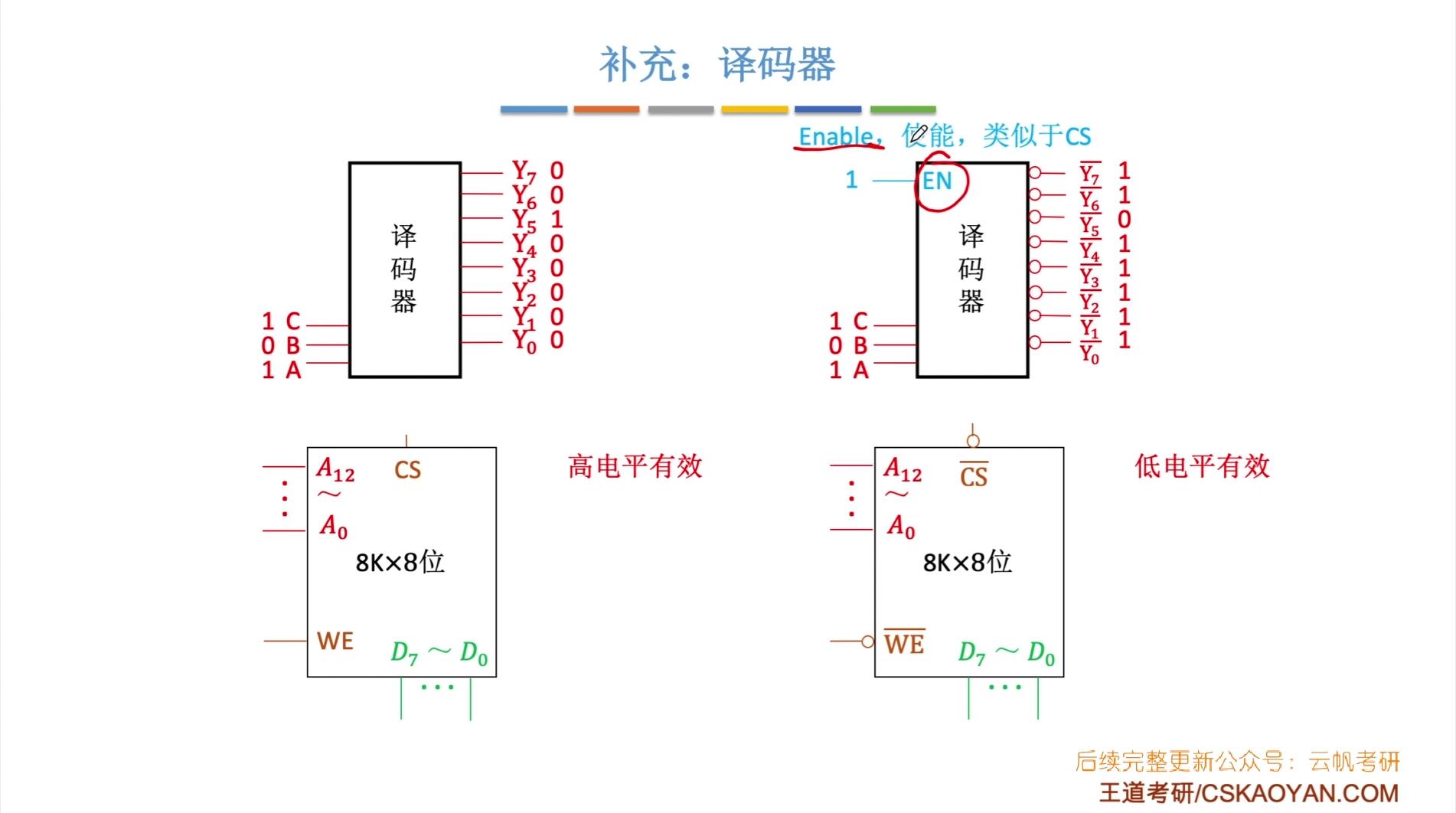

线选法:

1-2、3-8 译码器

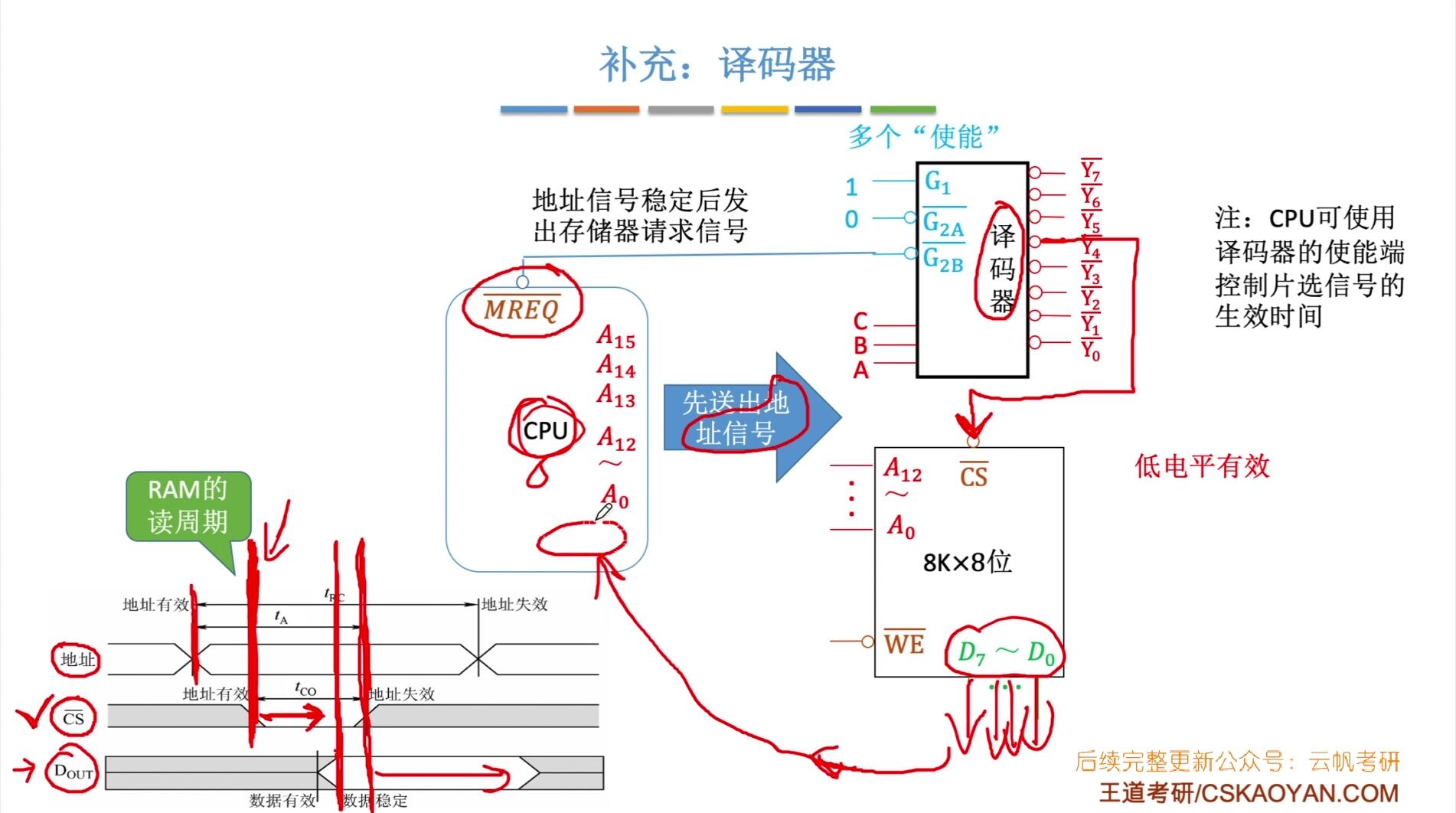

译码器

CPU中具有使能端:地址信号稳定后向存储器发出请求信号,使产生有效的片选信号

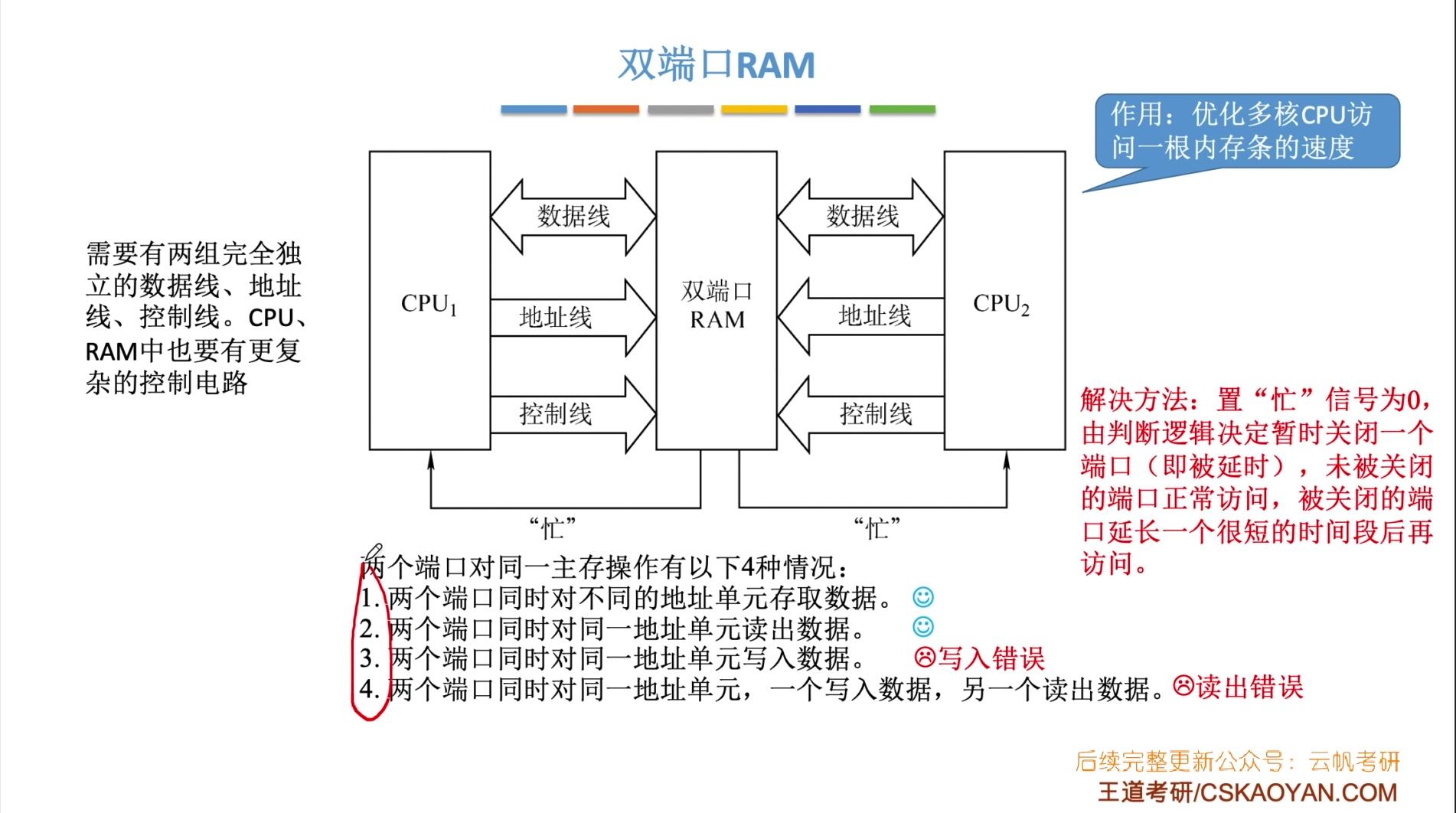

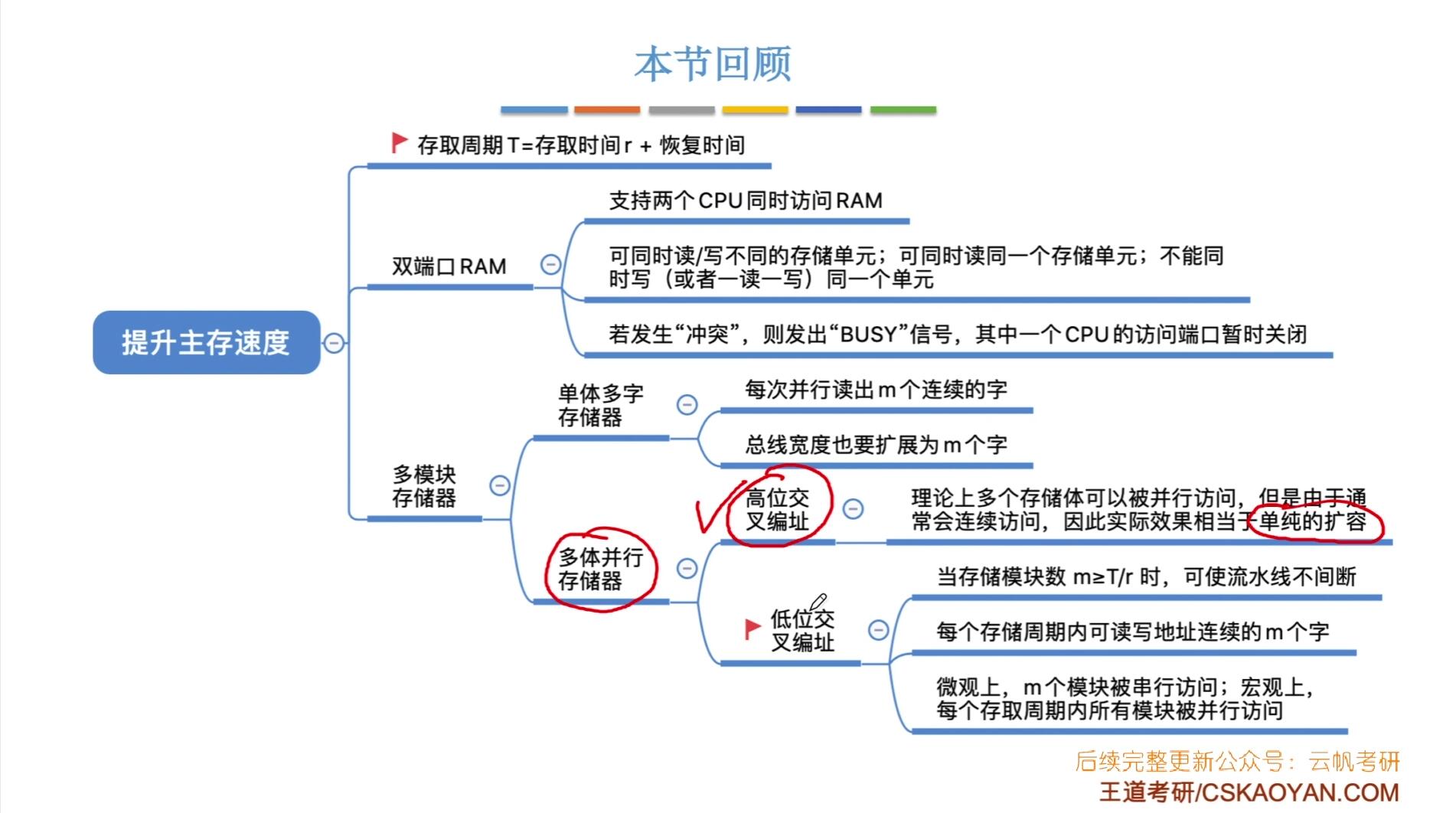

双端口RAM和多模块存储器

双端口RAM

优化多核CPU访问同一根内存条的速度

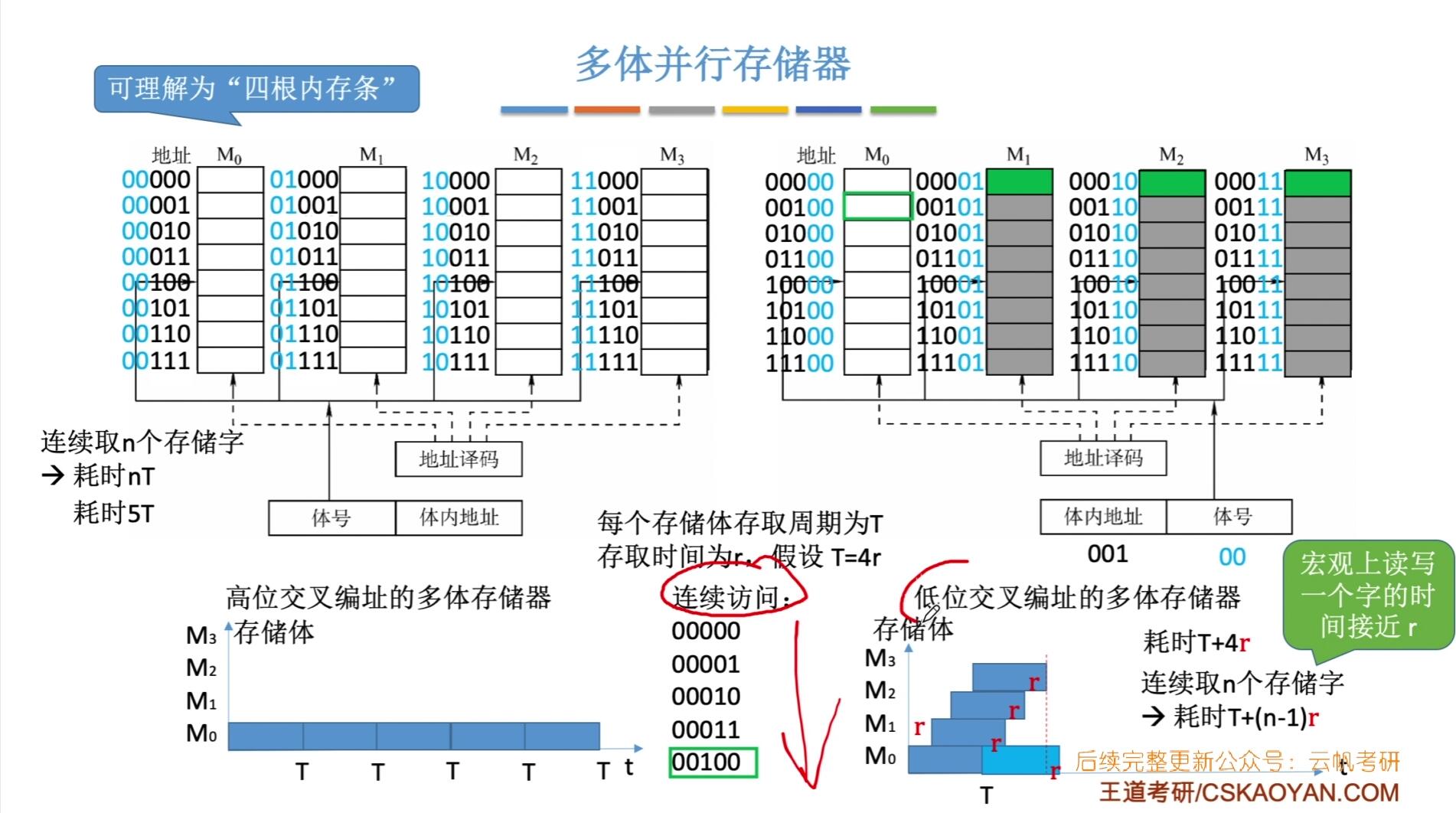

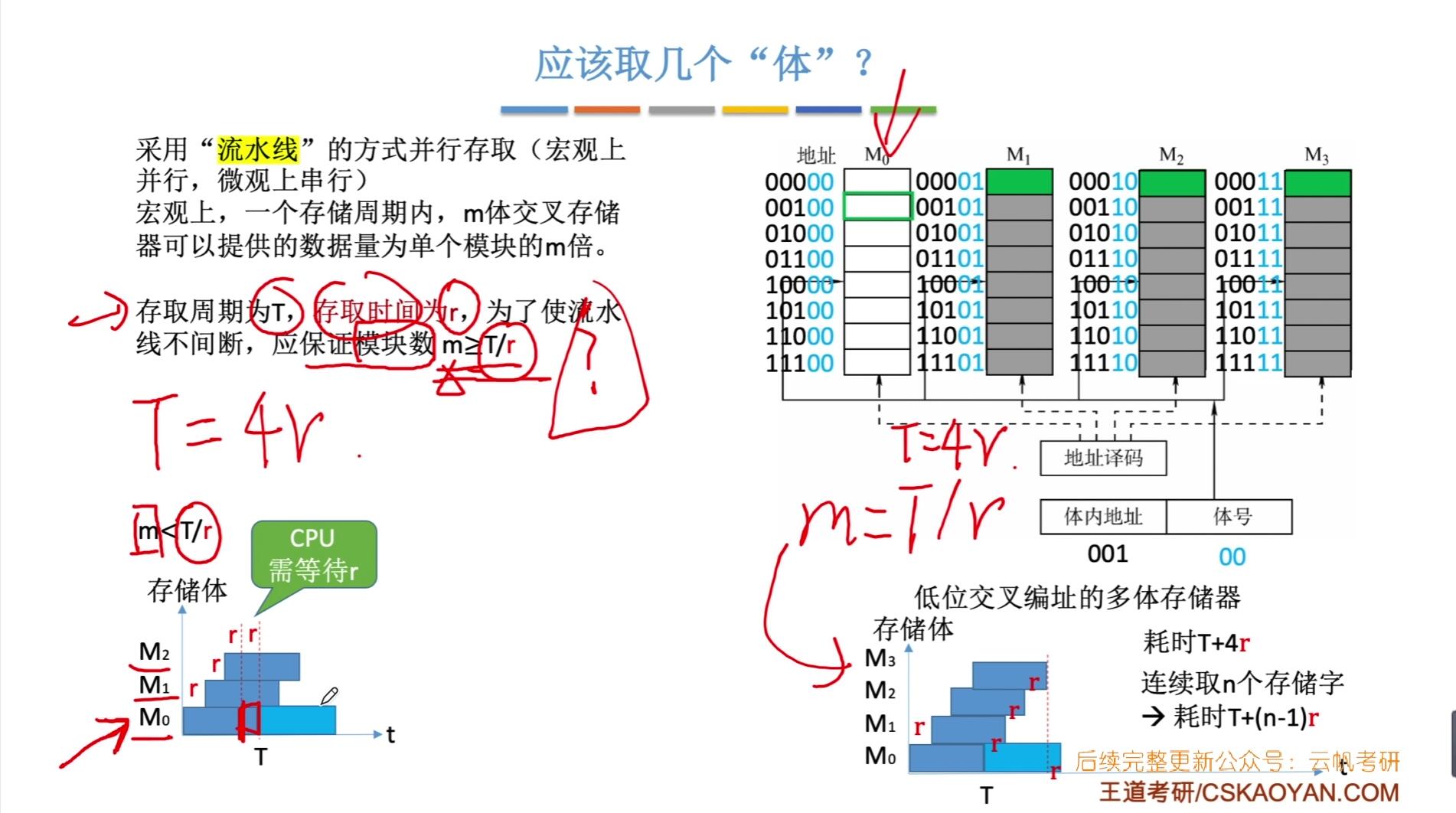

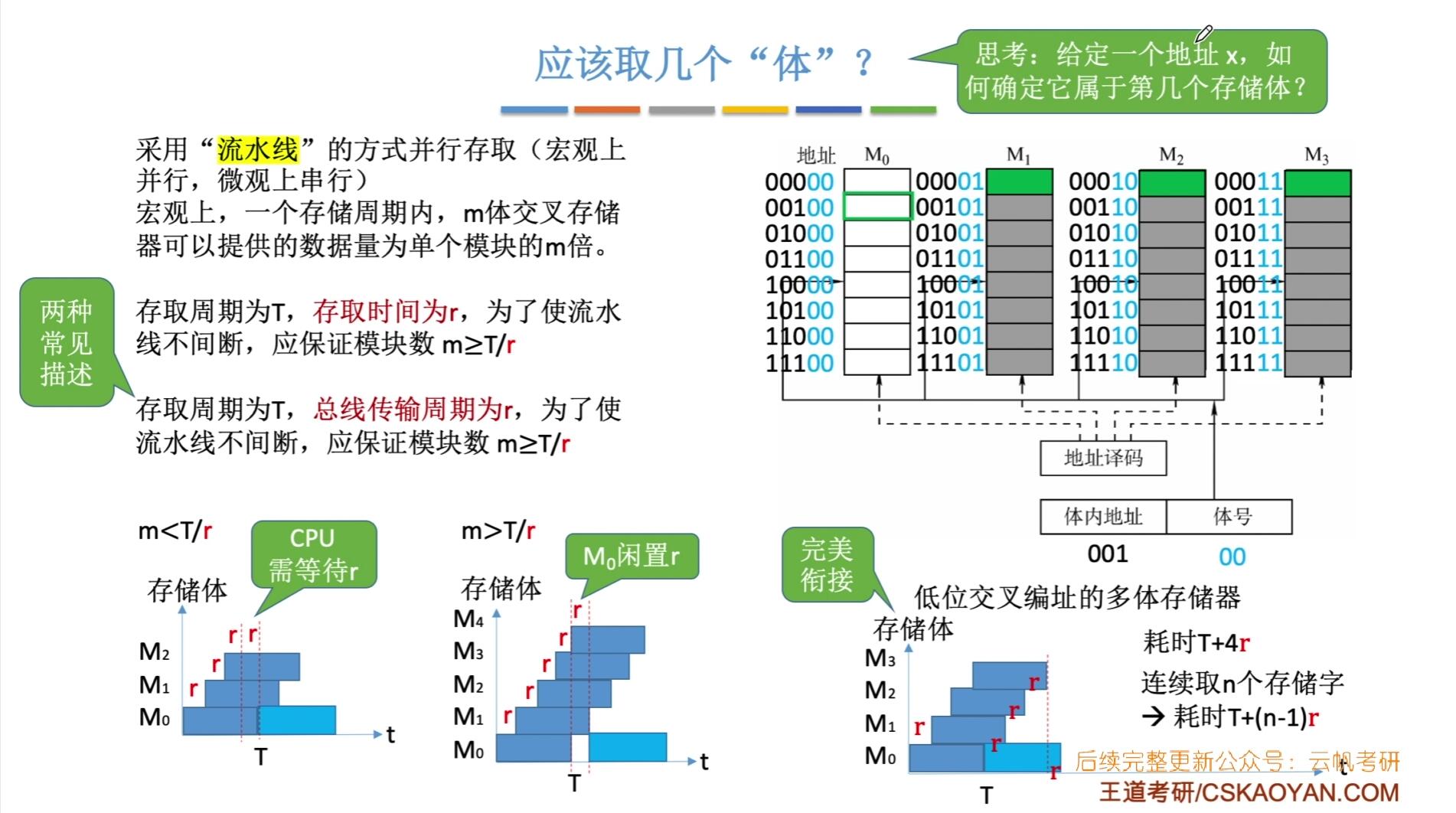

多体并行存储器

m = T / R:存取周期,或者是总线传输周期

主频越高,读写周期越短

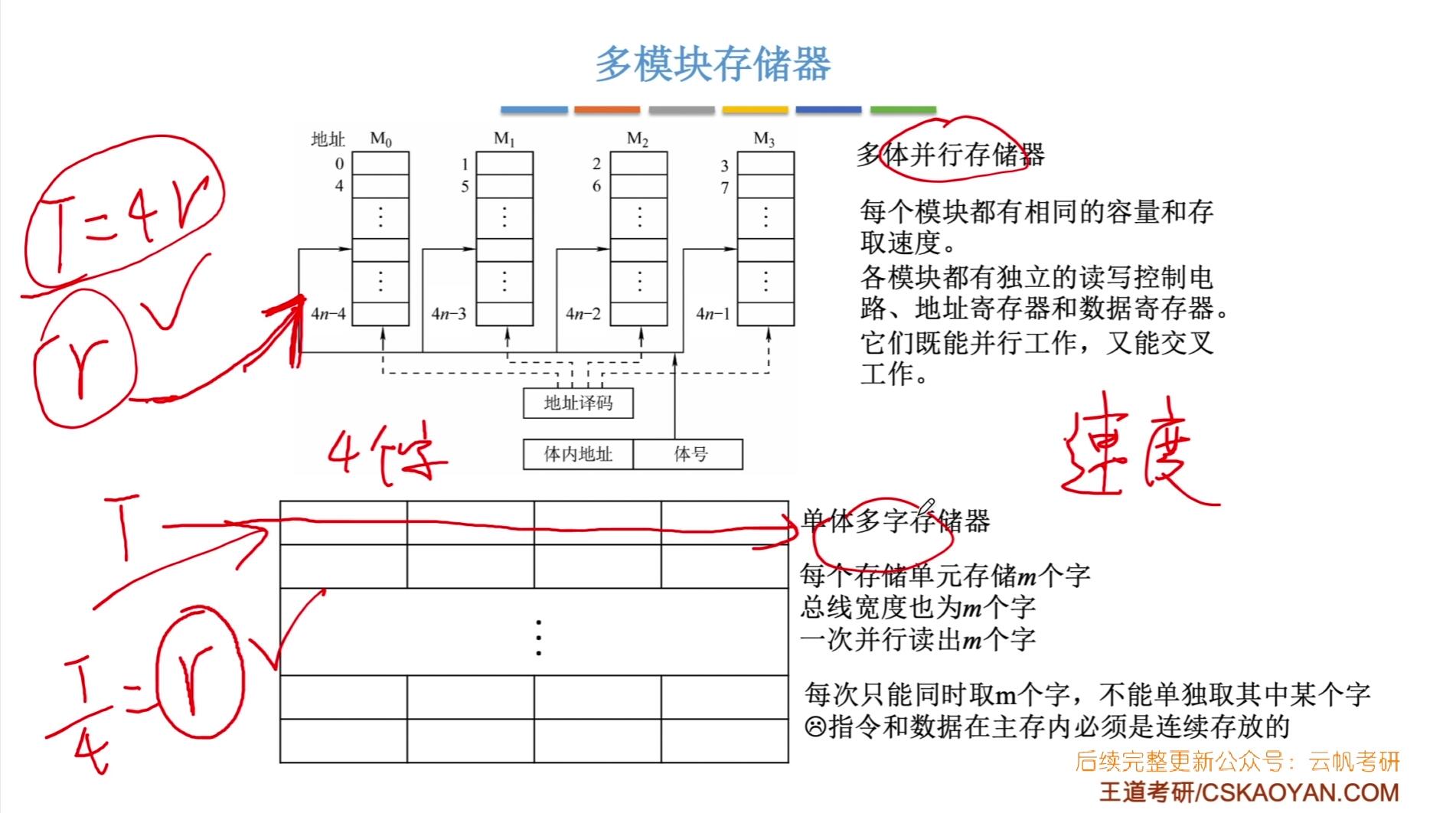

多模块存储器

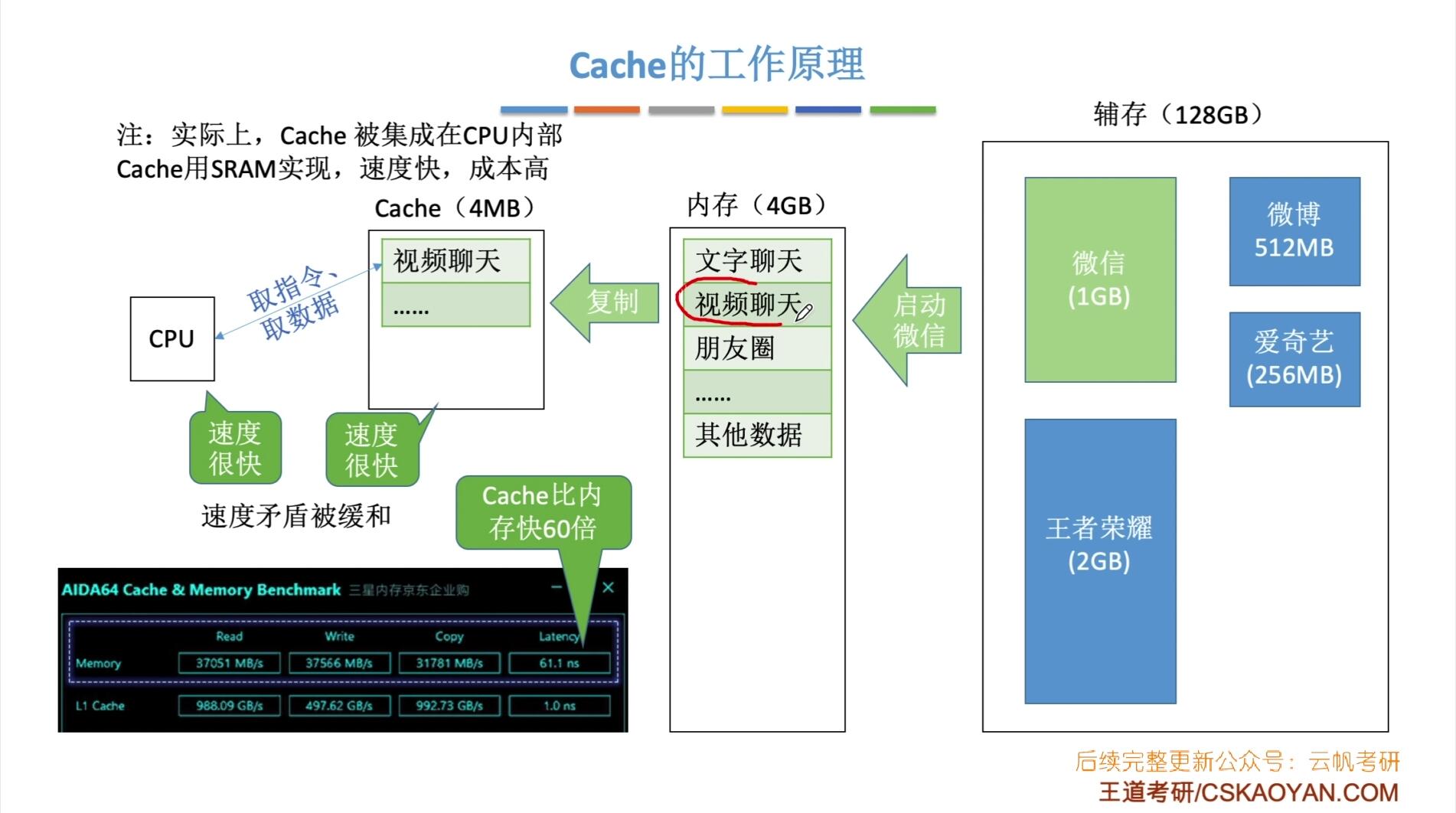

cache

工作原理

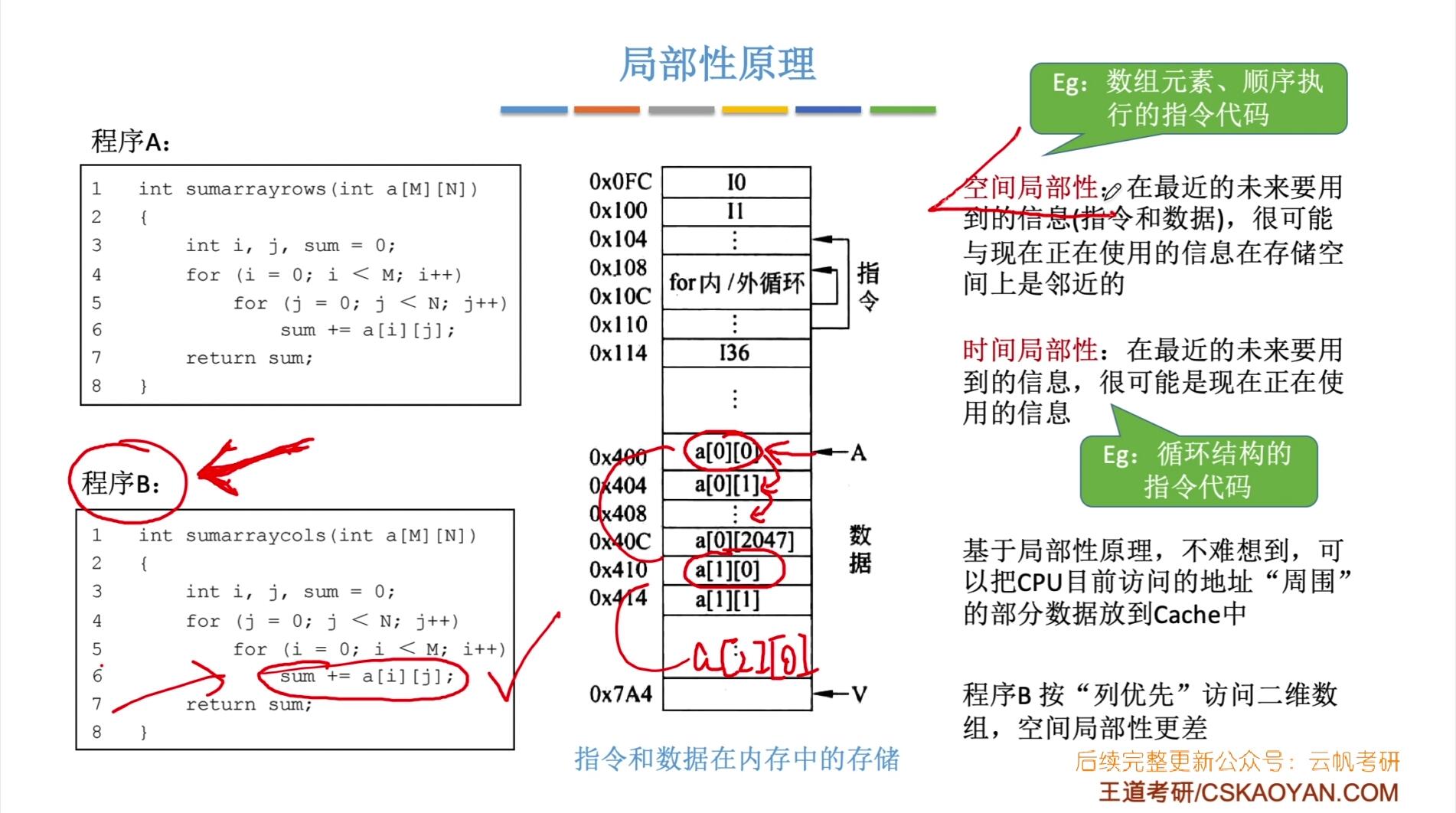

局部性原理

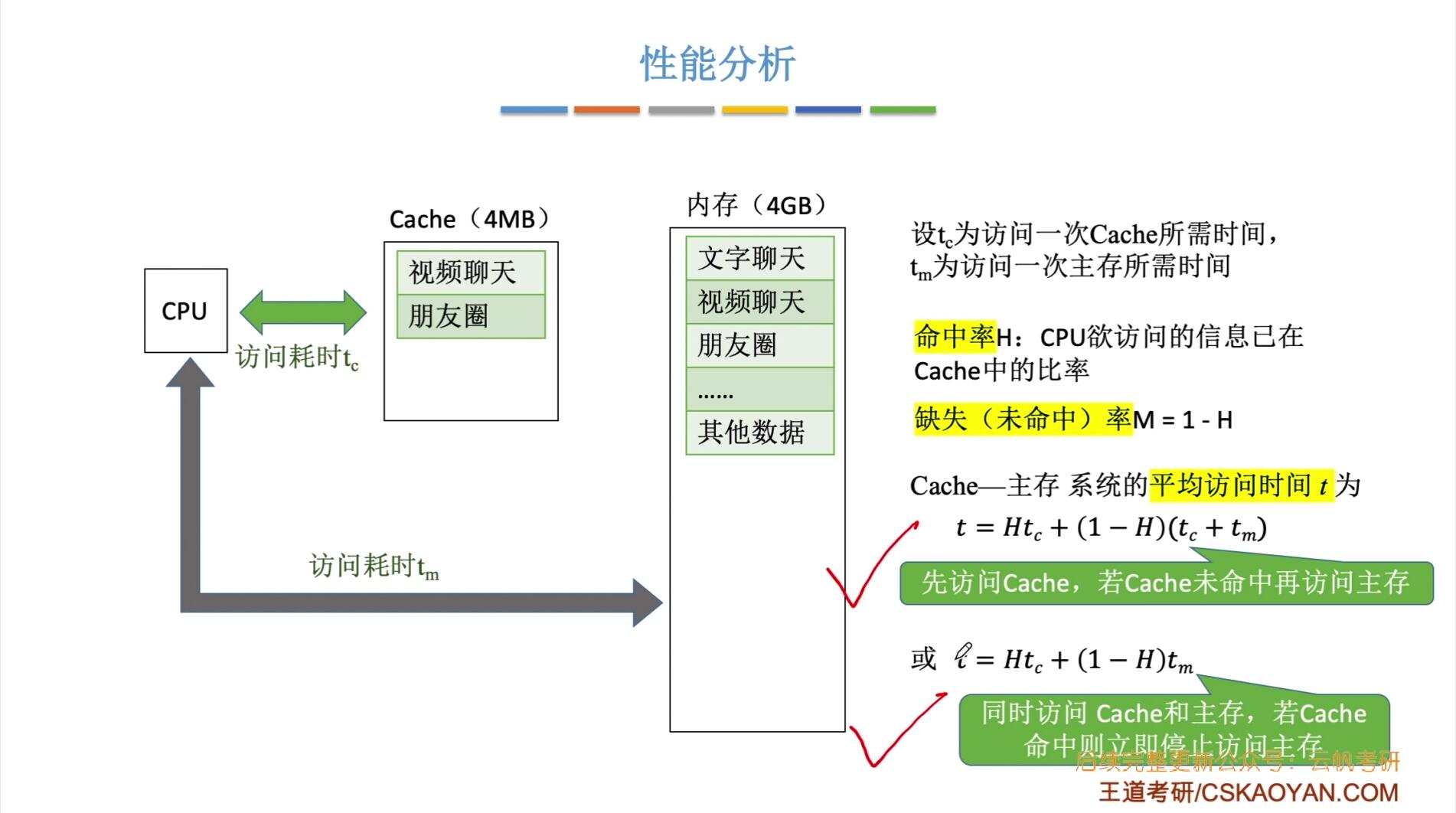

性能分析

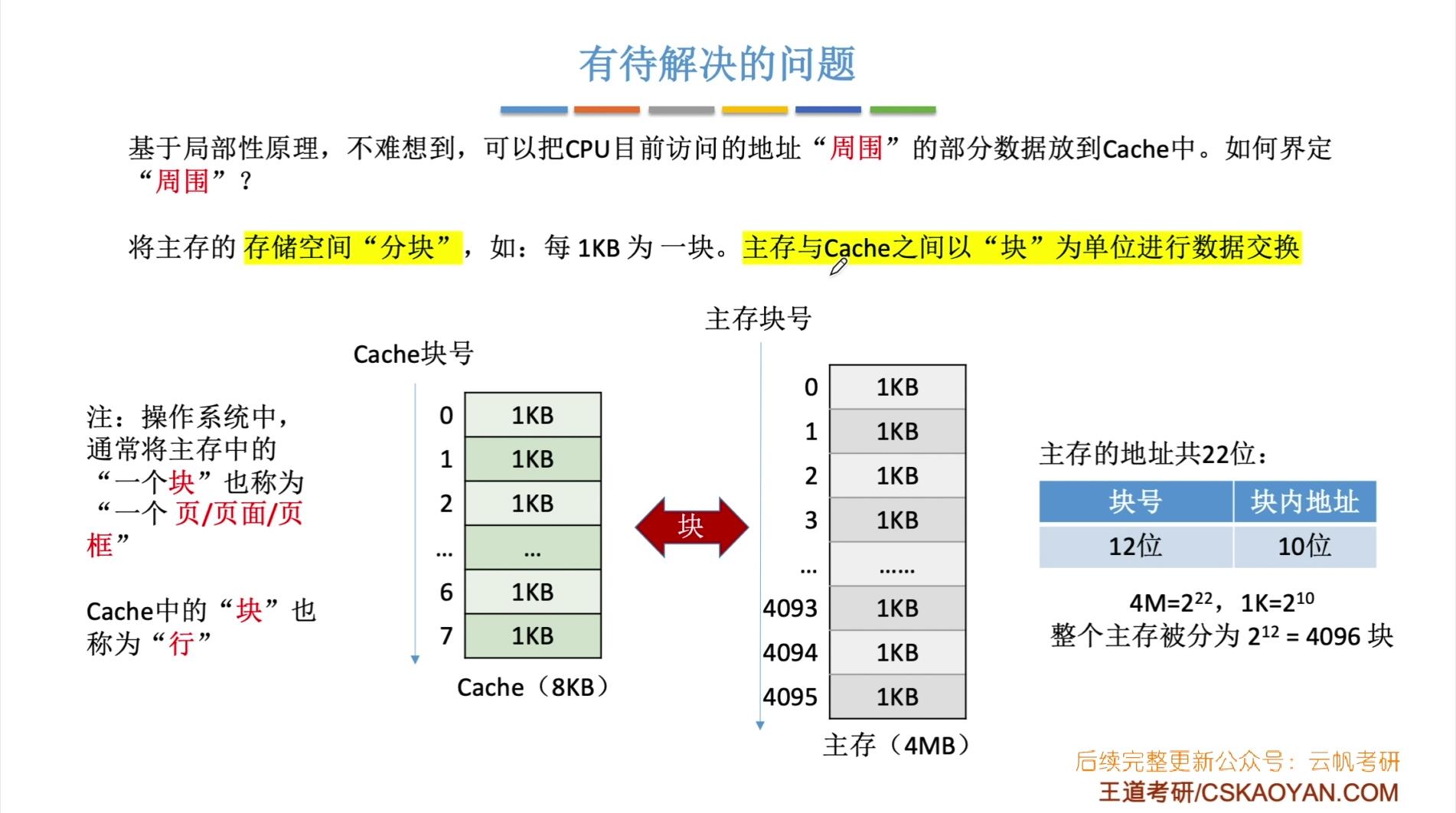

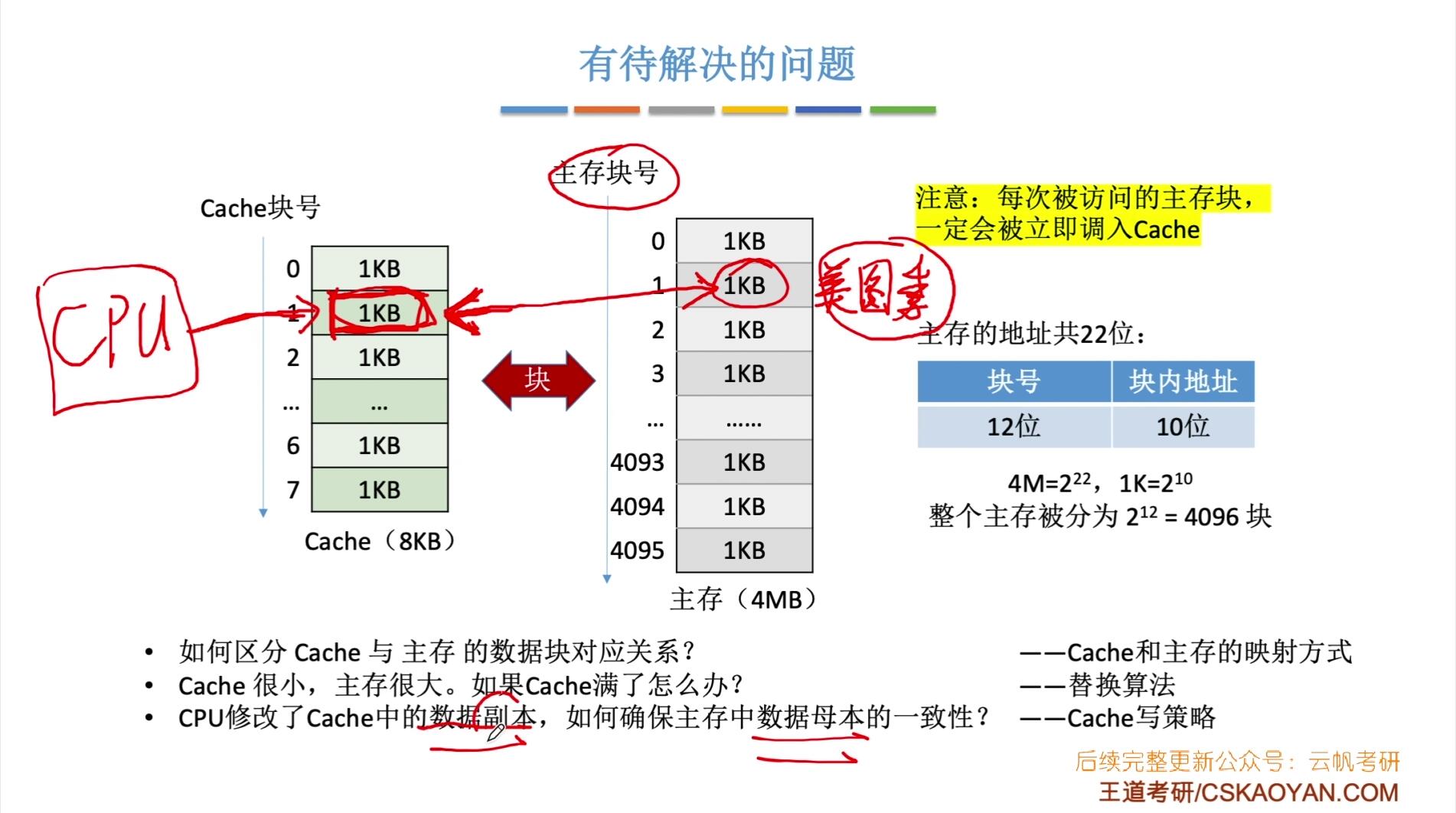

待解决的问题

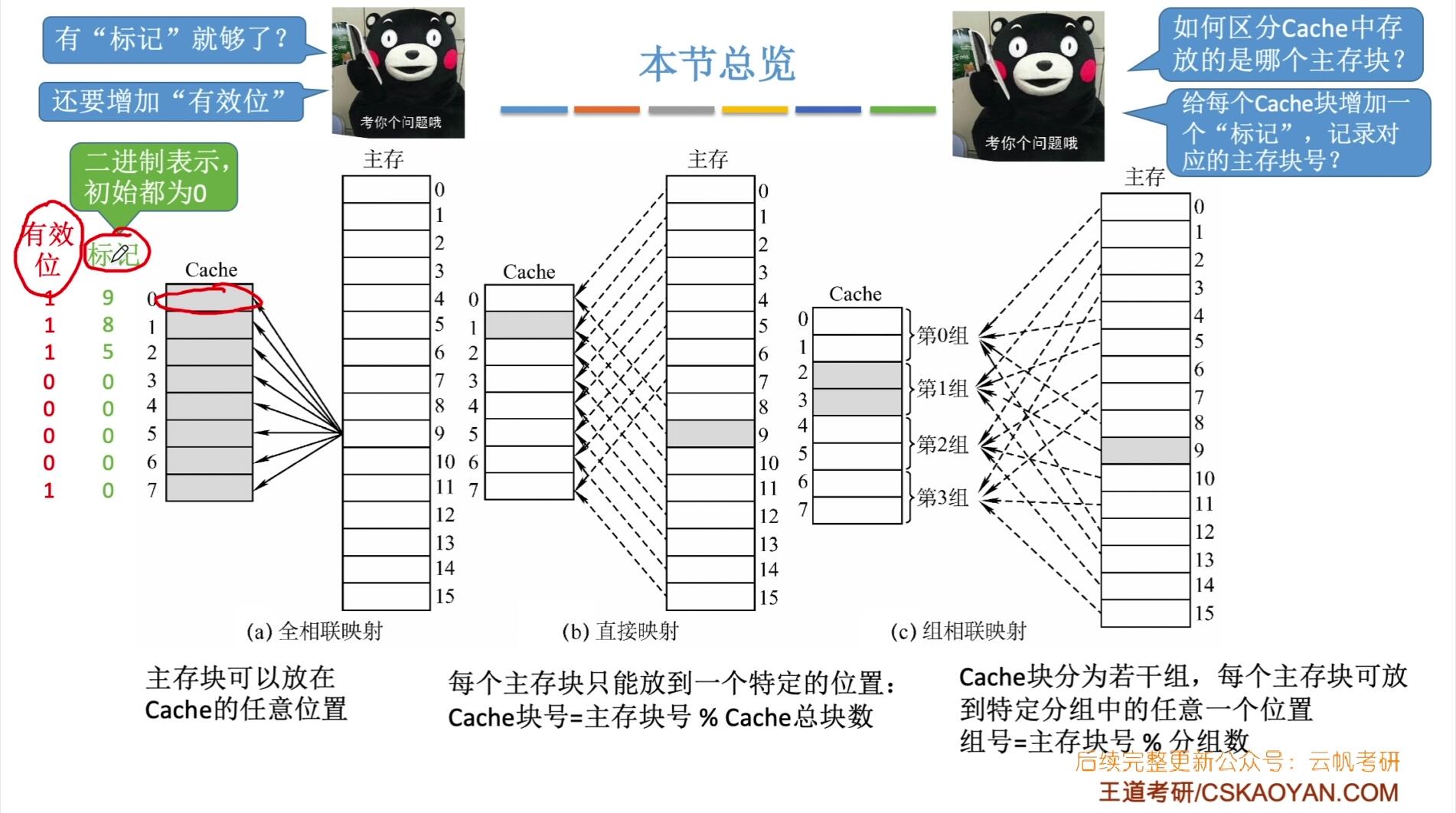

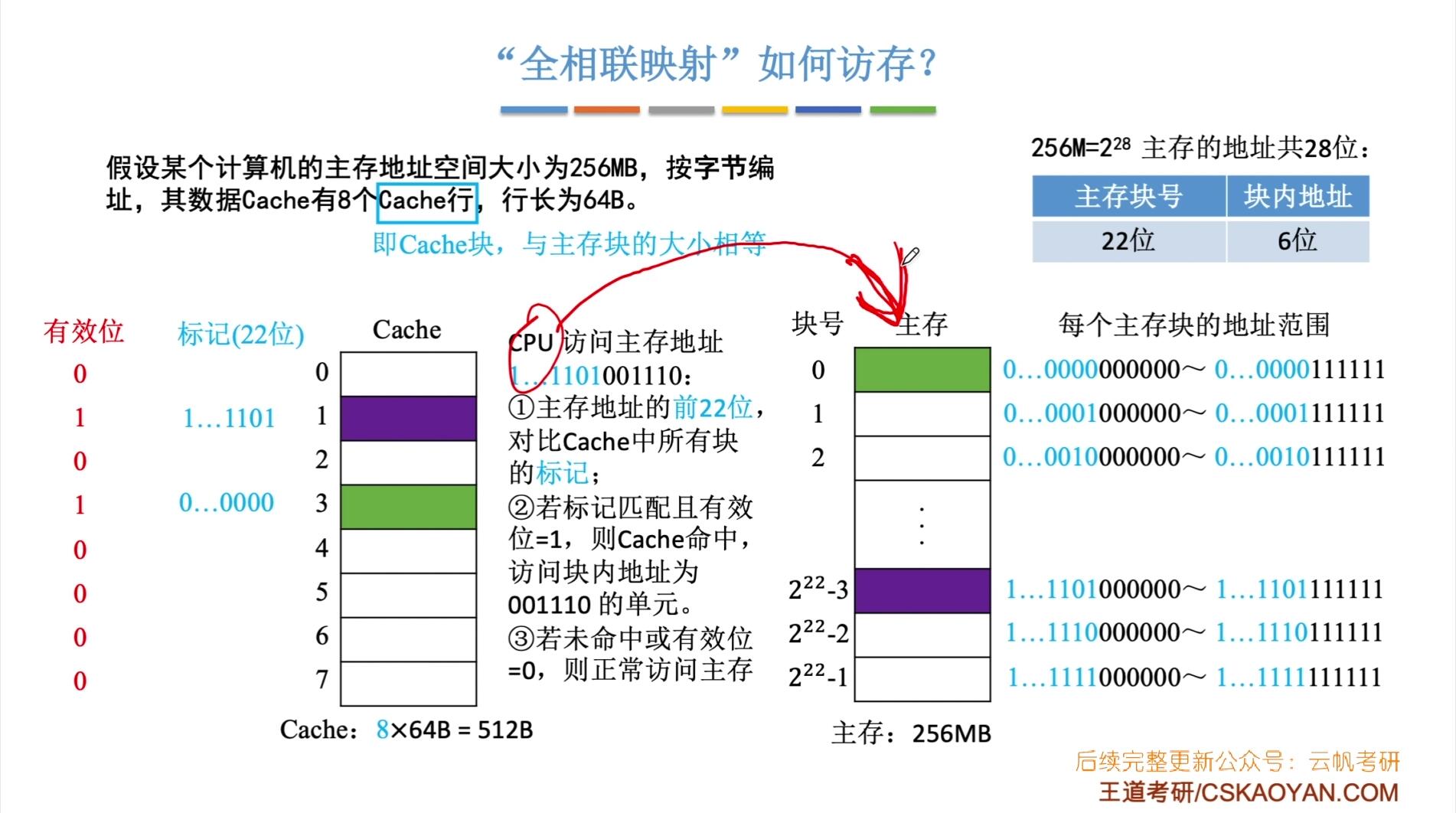

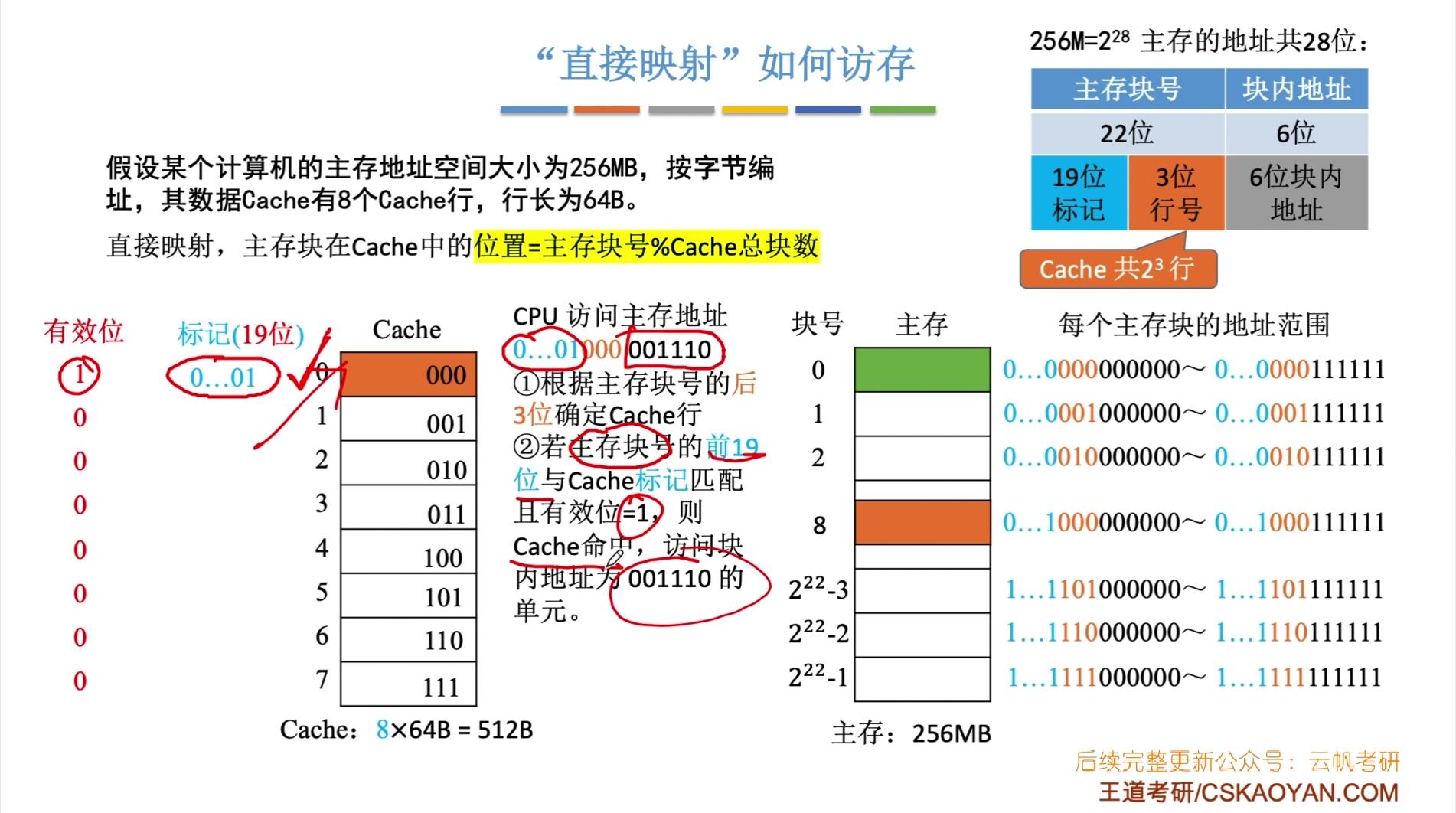

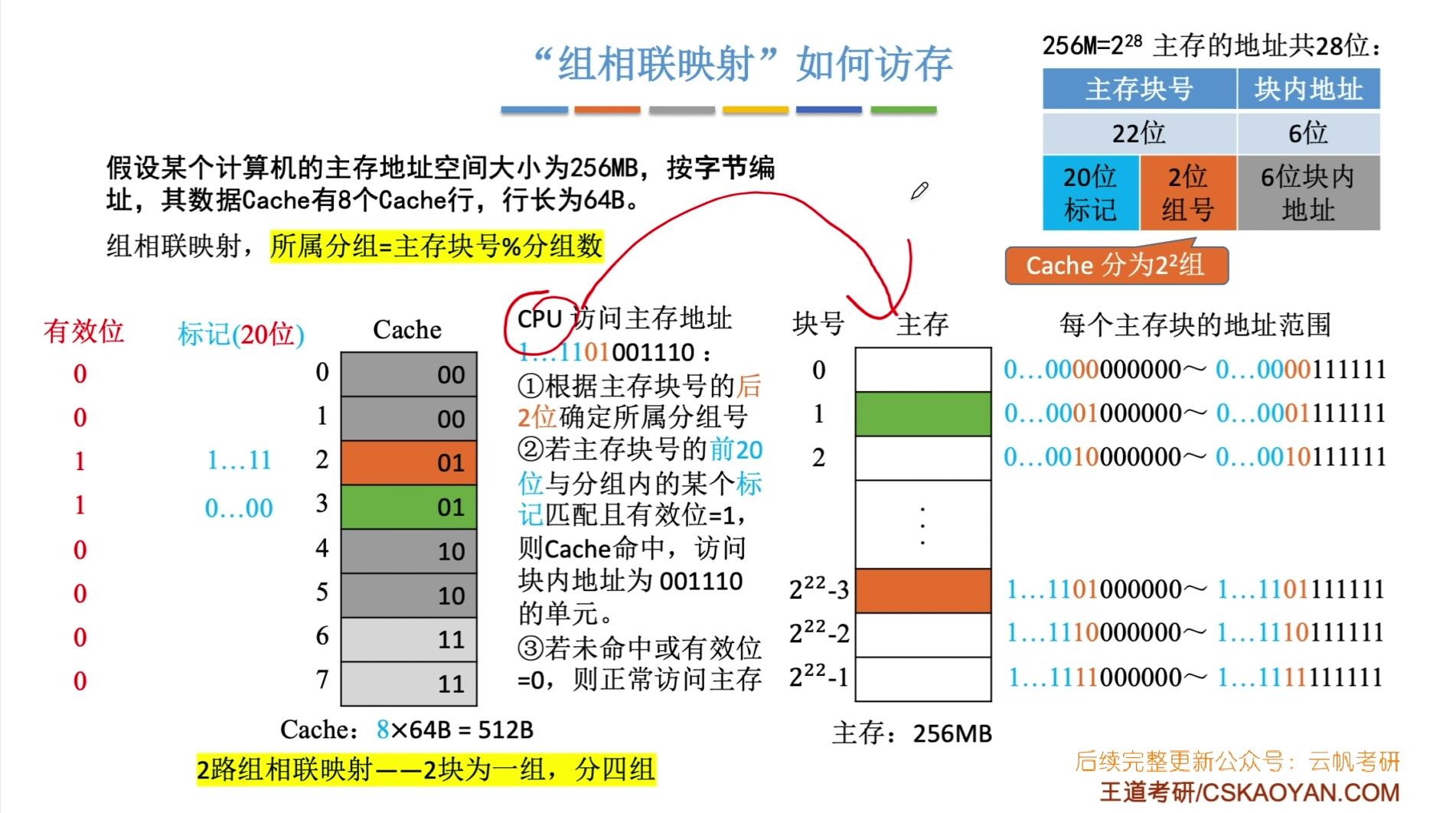

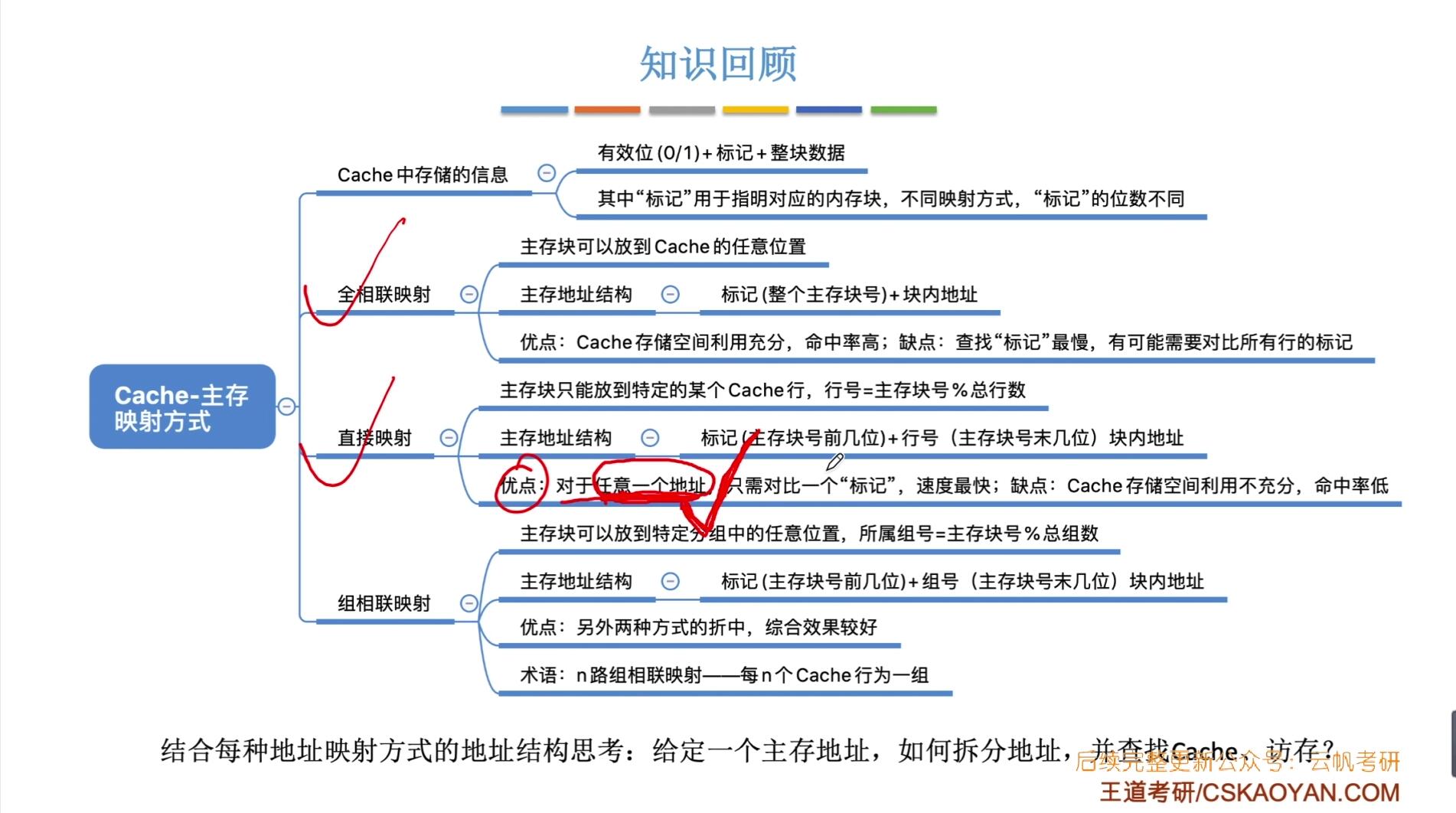

cache与主存的三种映射方式

- 全相联

- 直接相联

- n路组相联

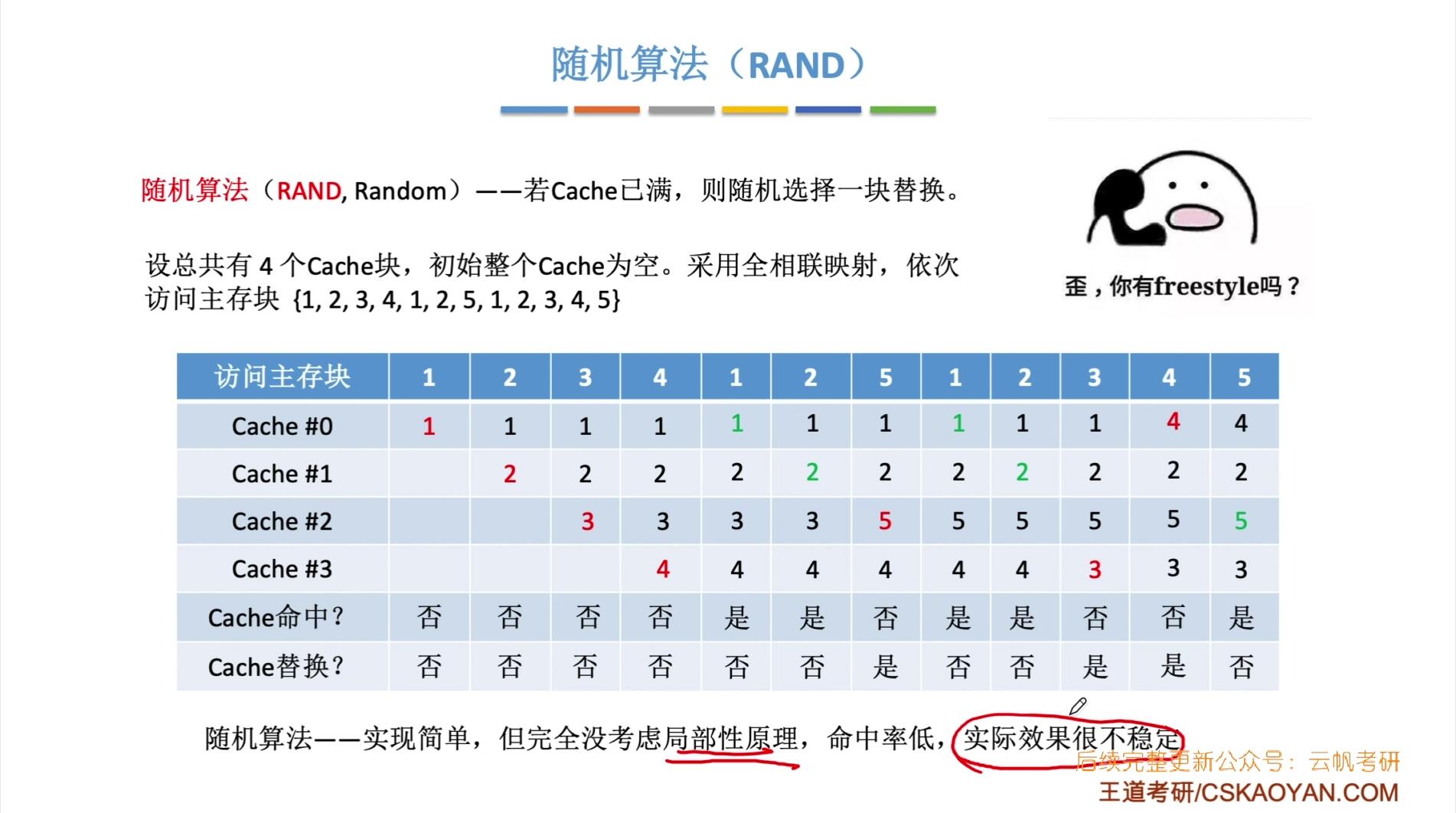

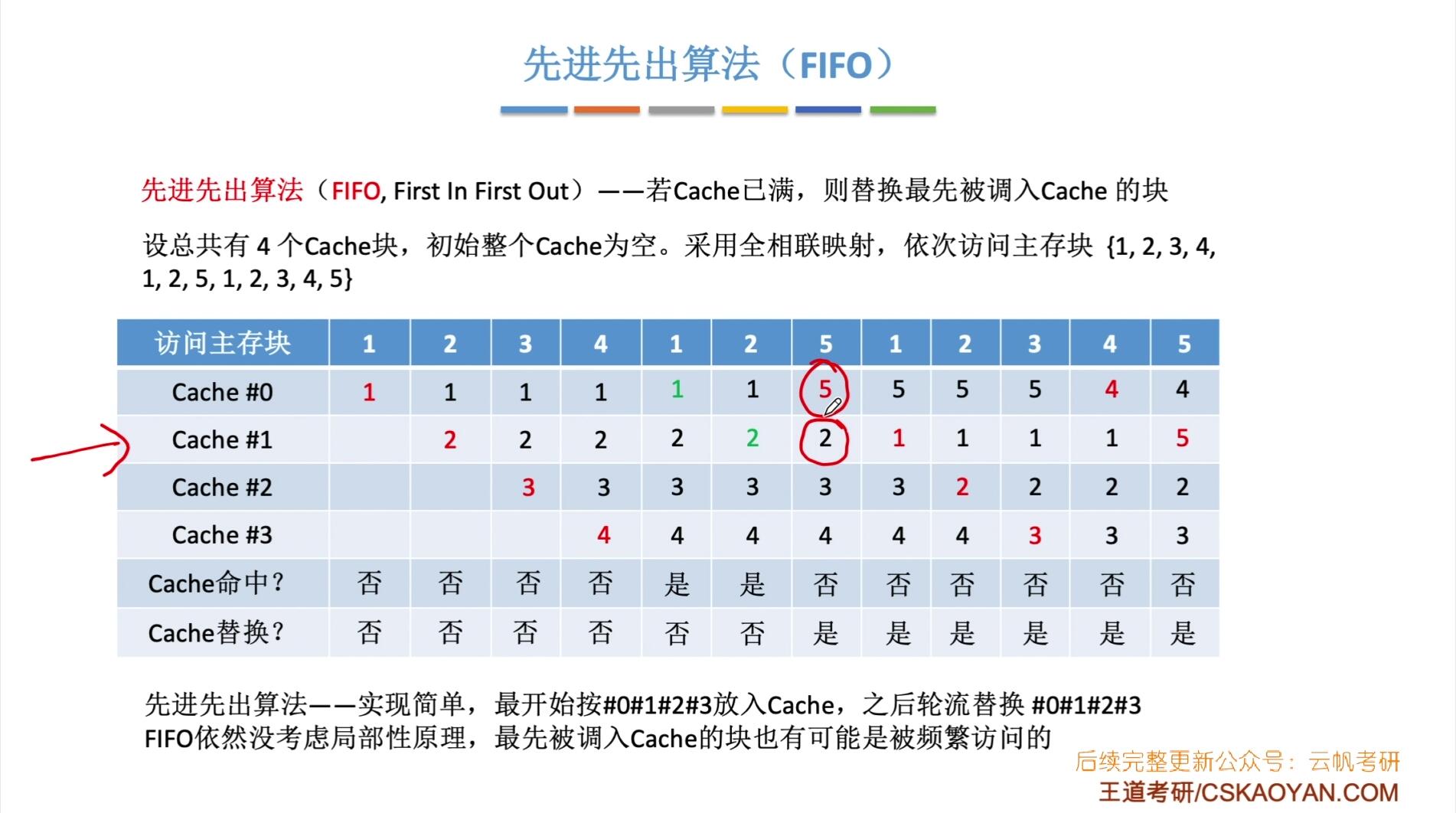

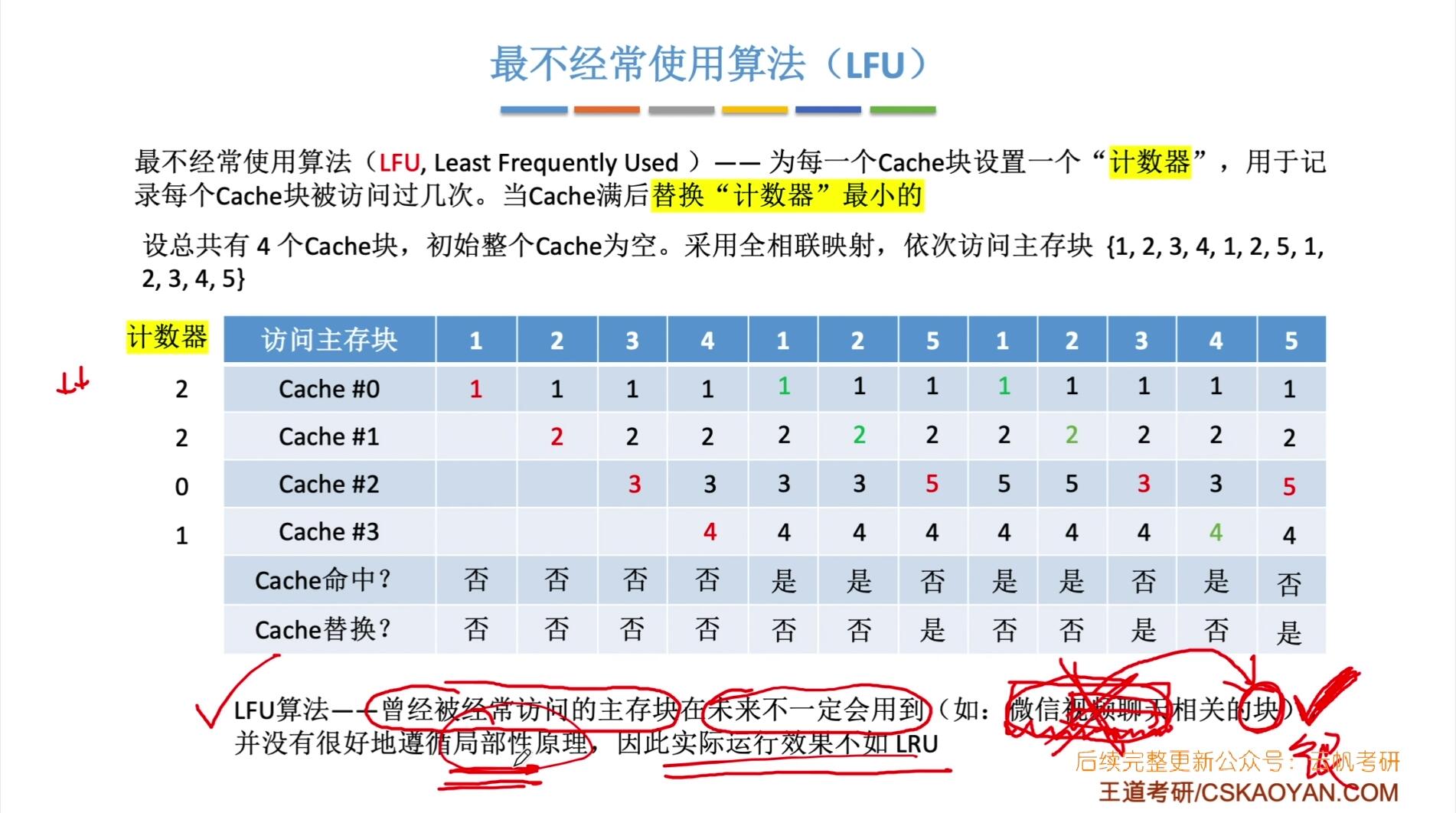

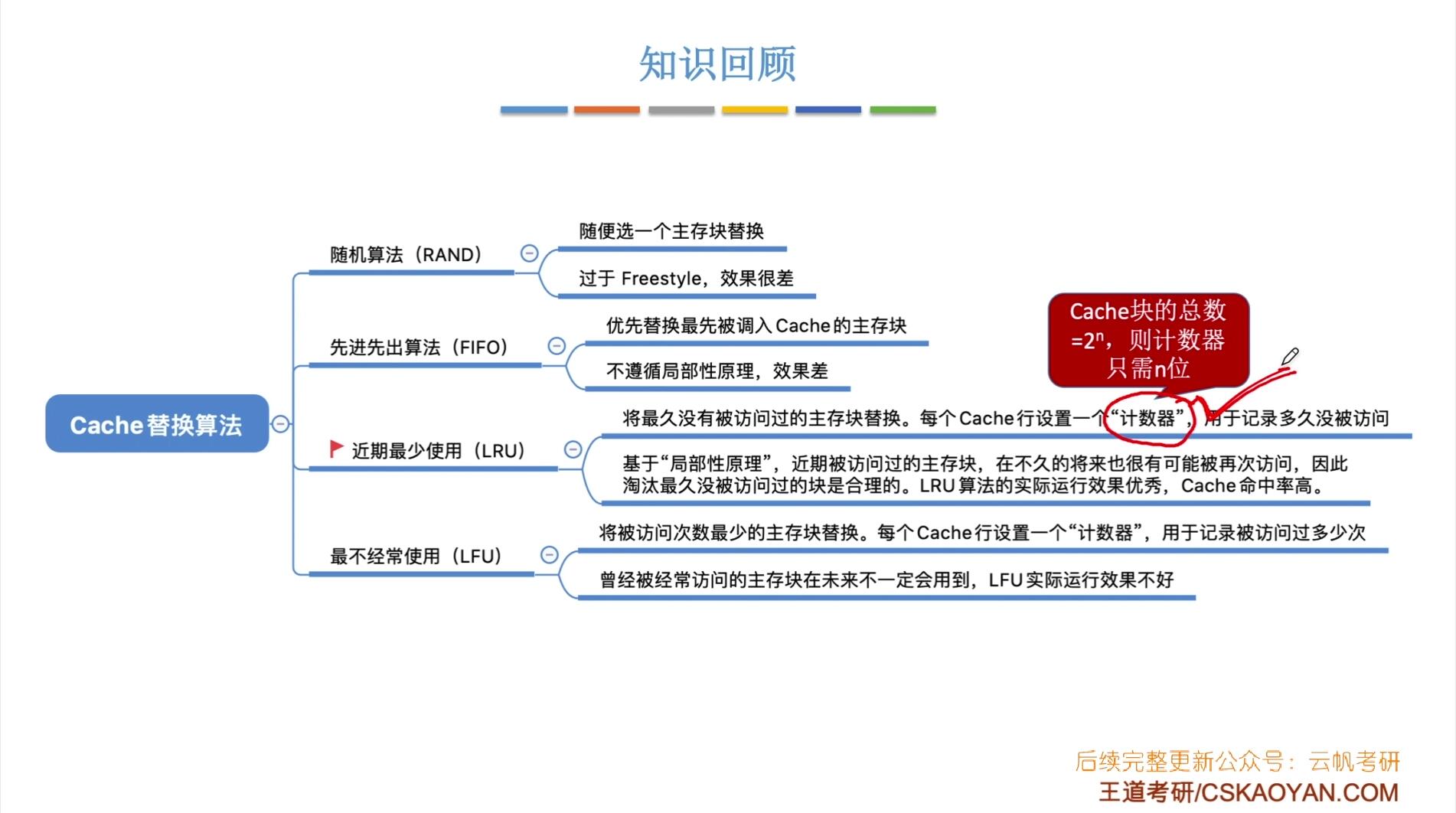

替换算法

随机算法(RAND)

先进先出(FIFO)

发生抖动现象:最先换出的很快就被换入

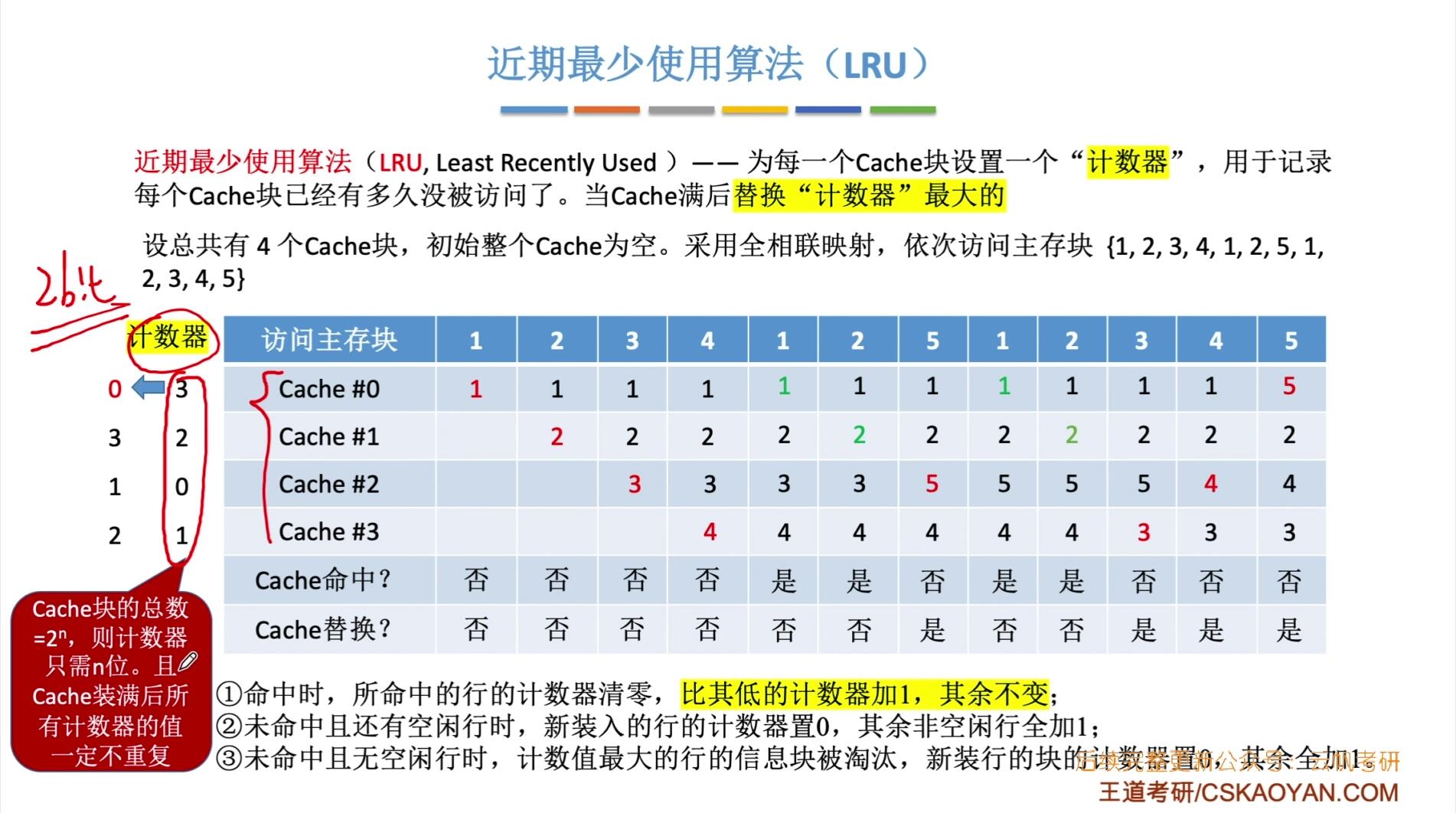

近期最少使用(LRU)

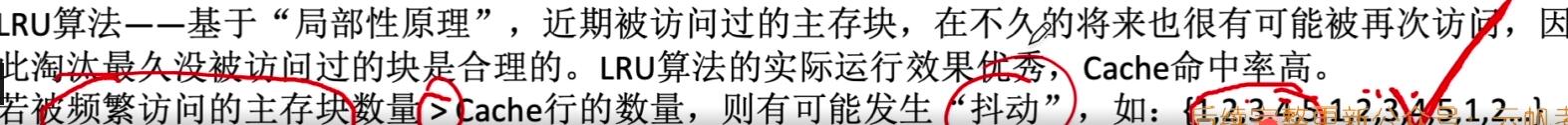

最不经常使用(LFU)

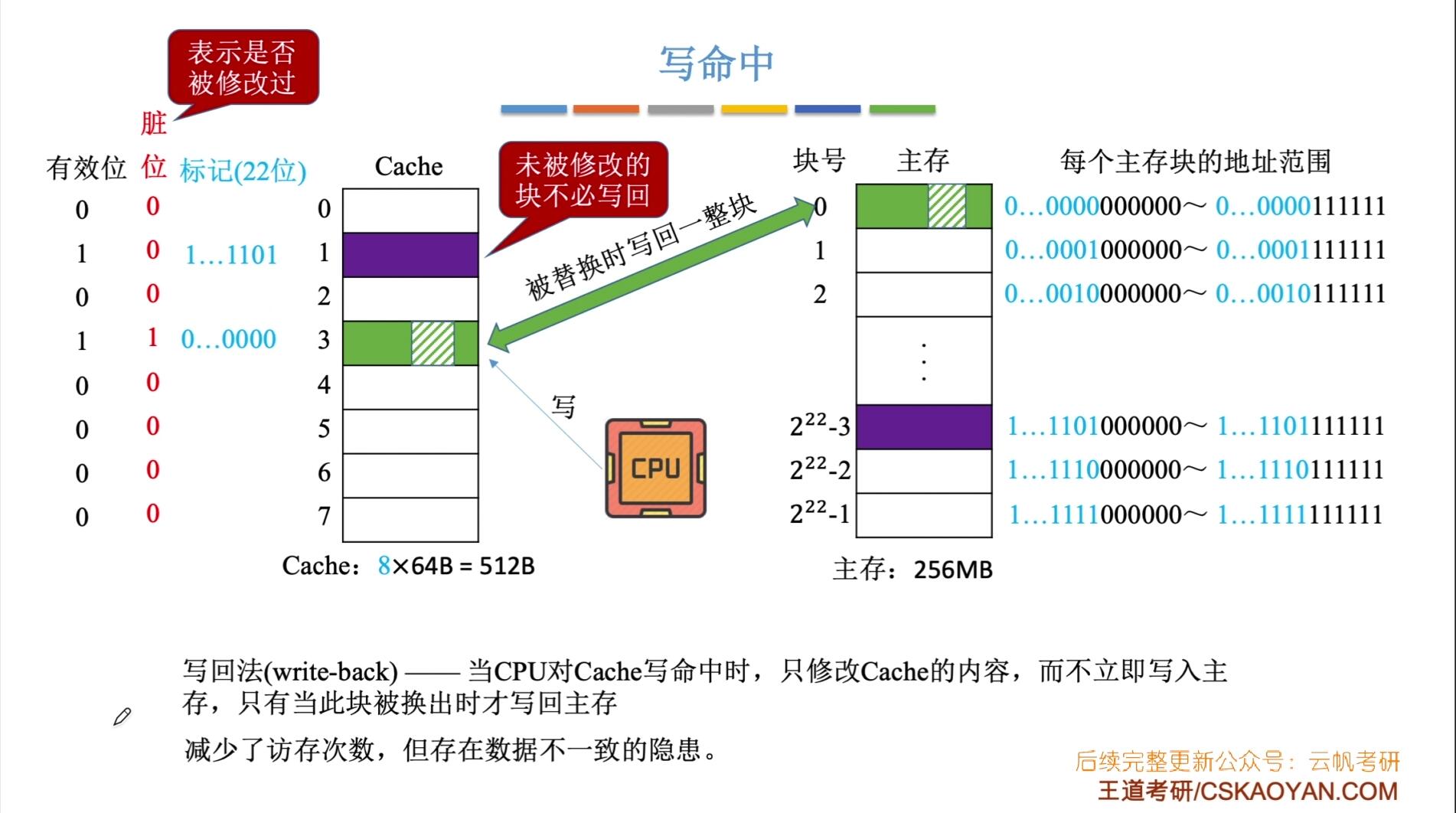

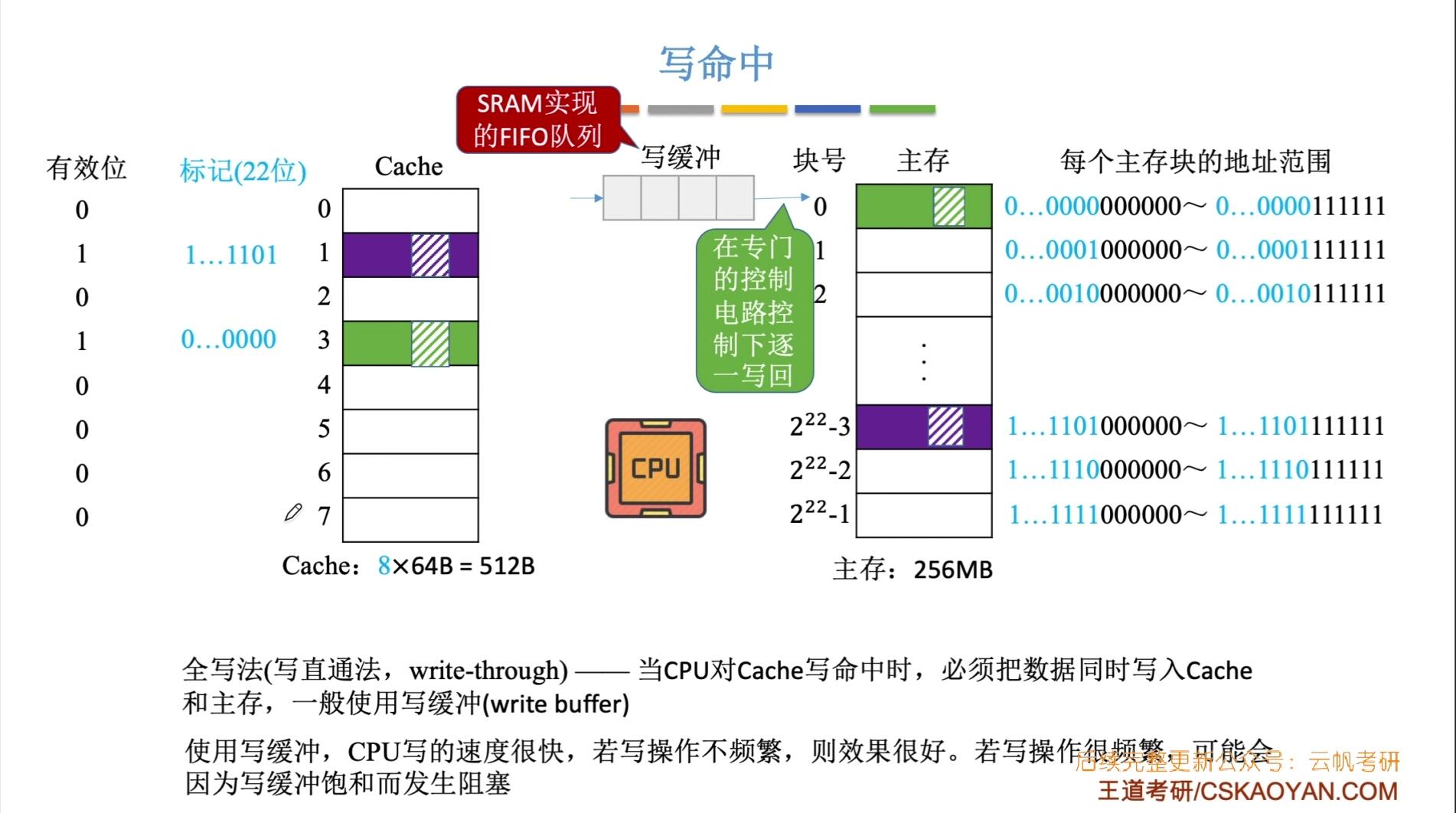

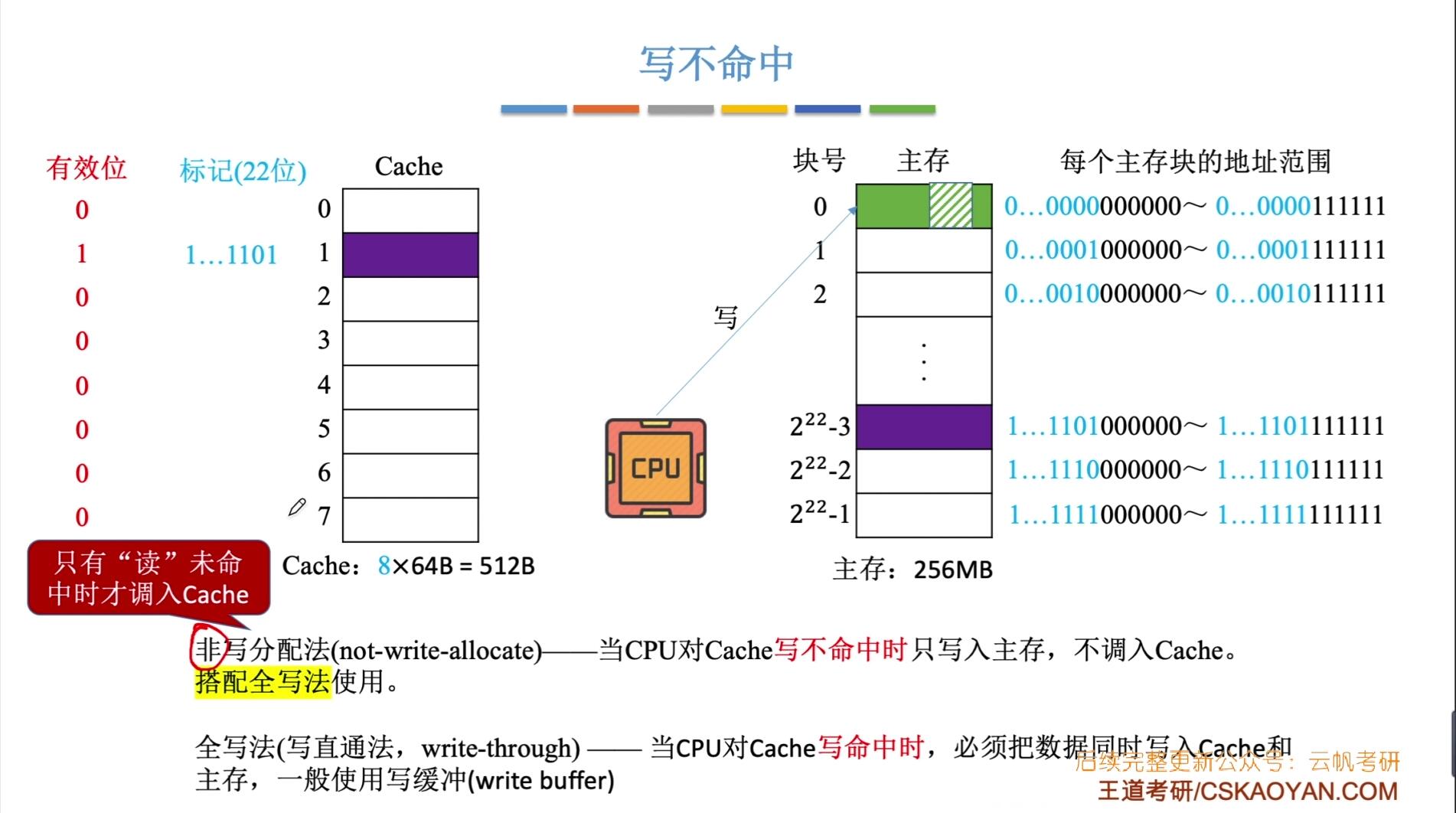

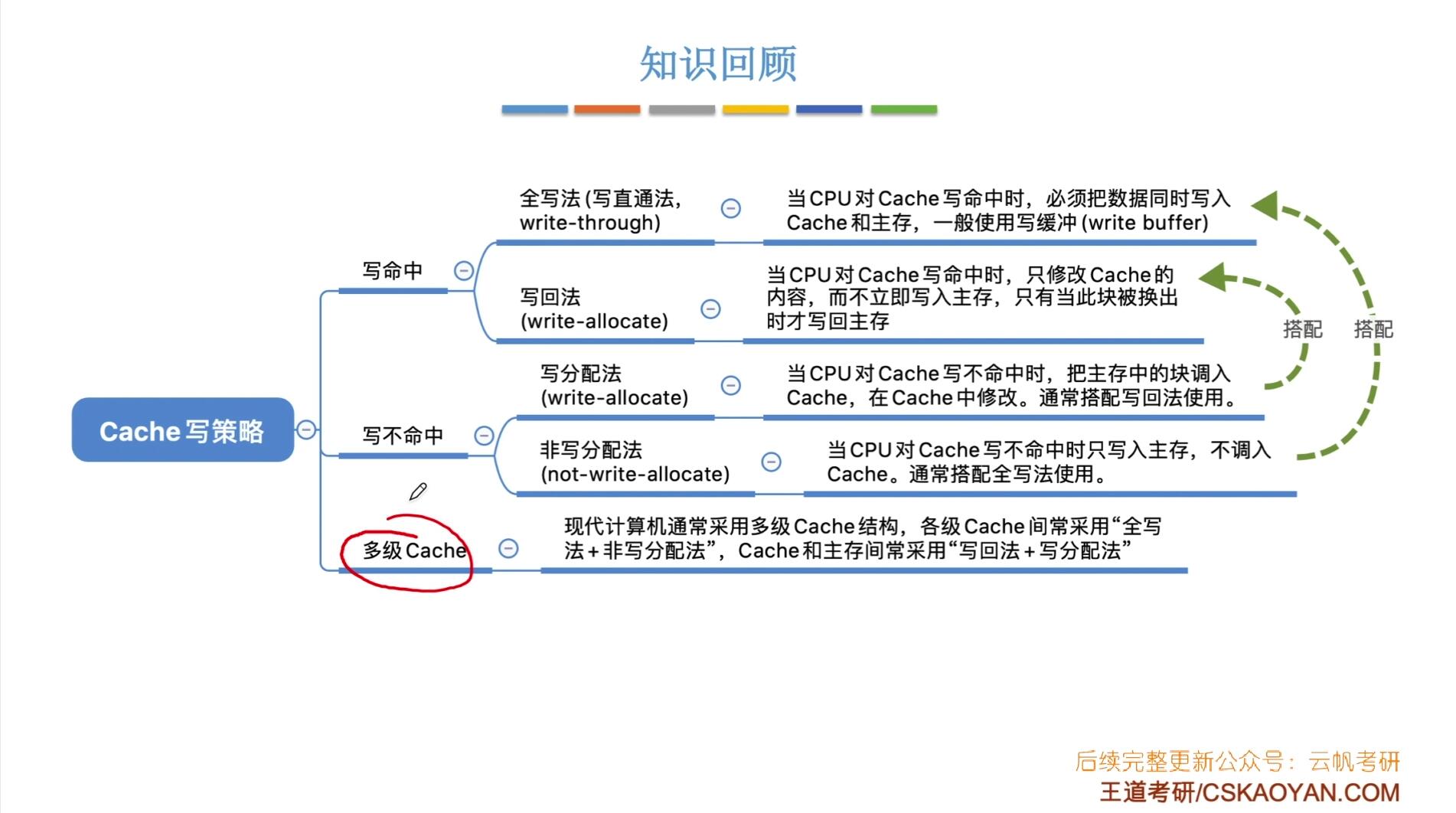

写策略

写命中

写不命中

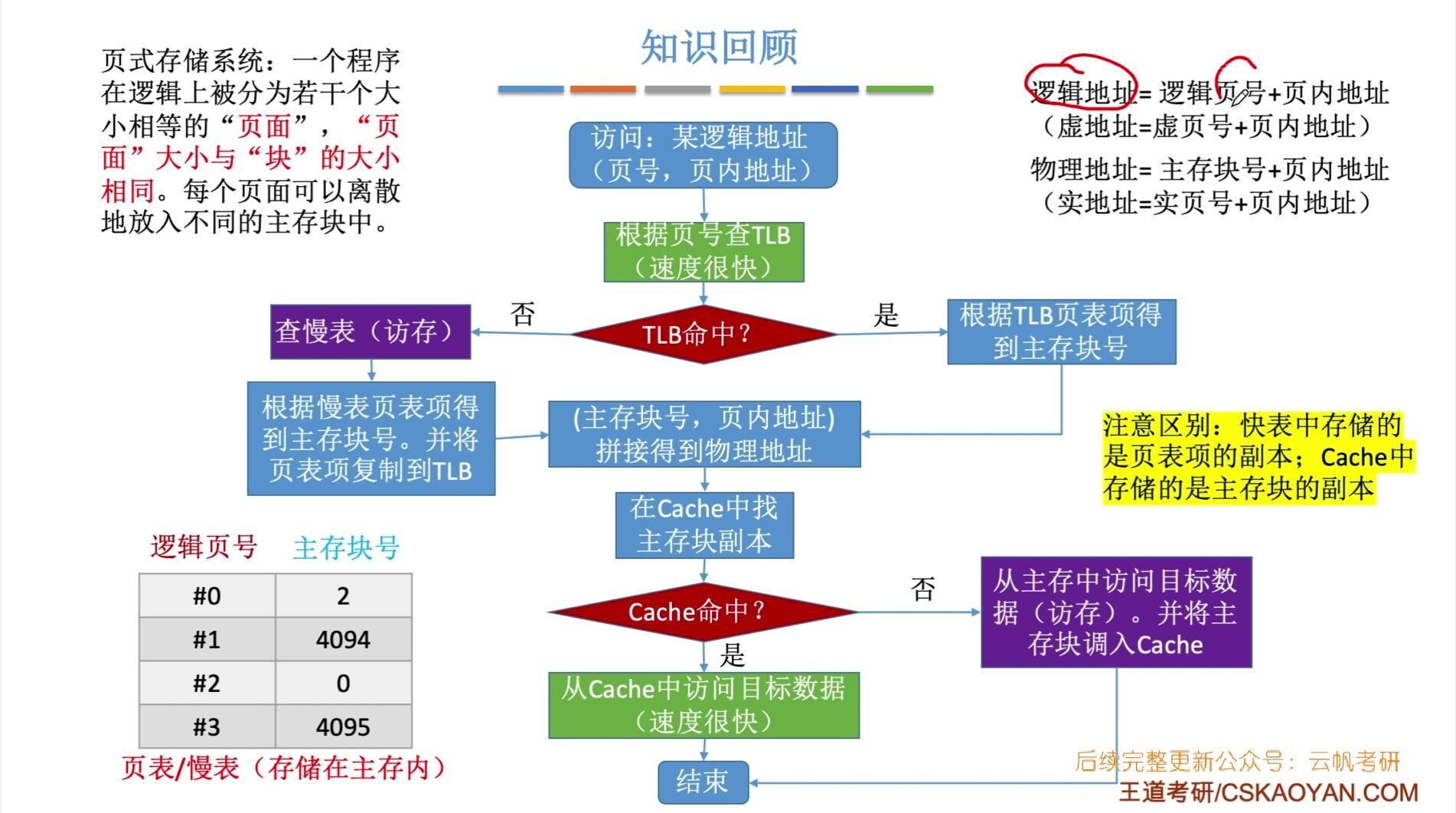

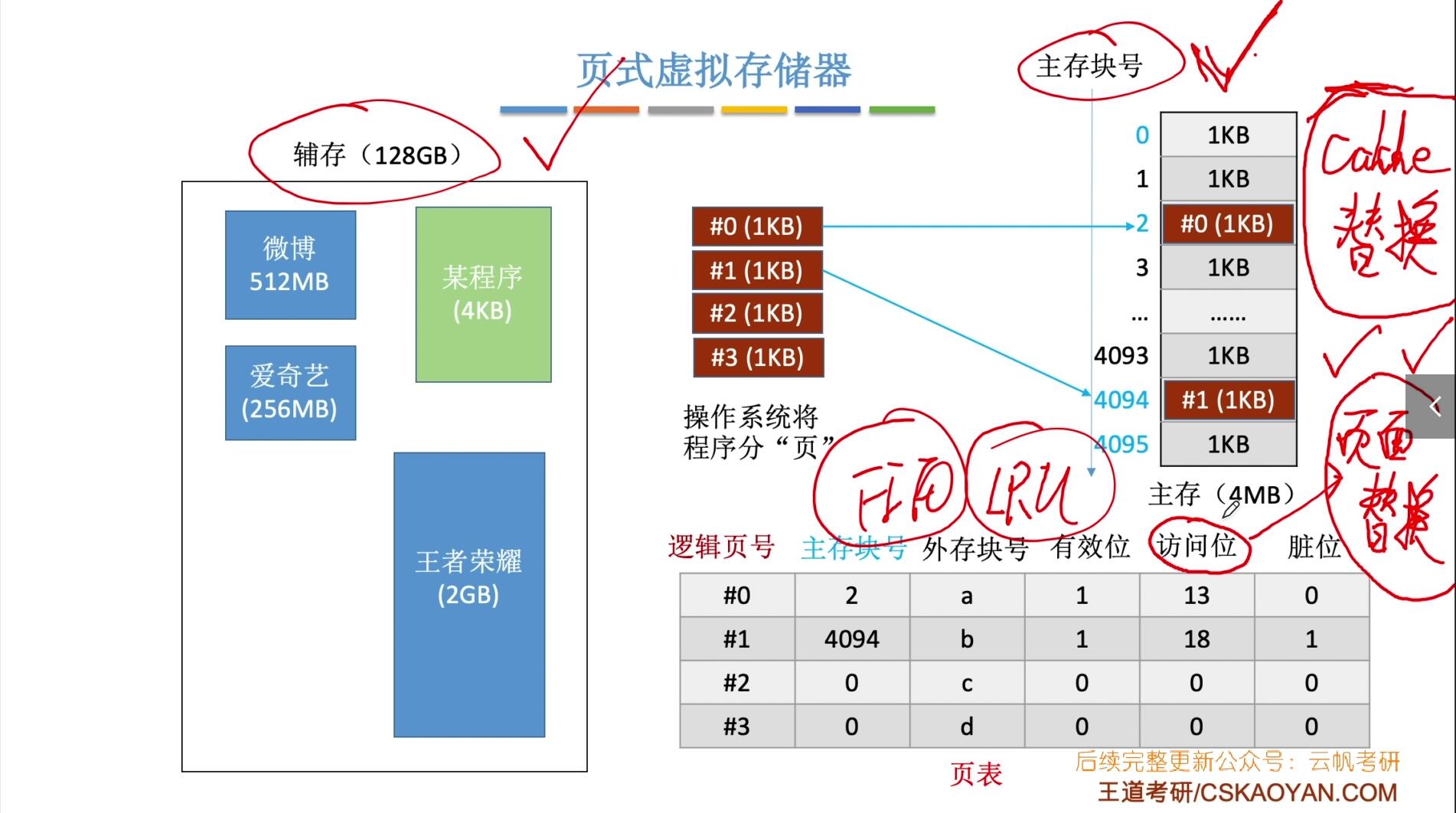

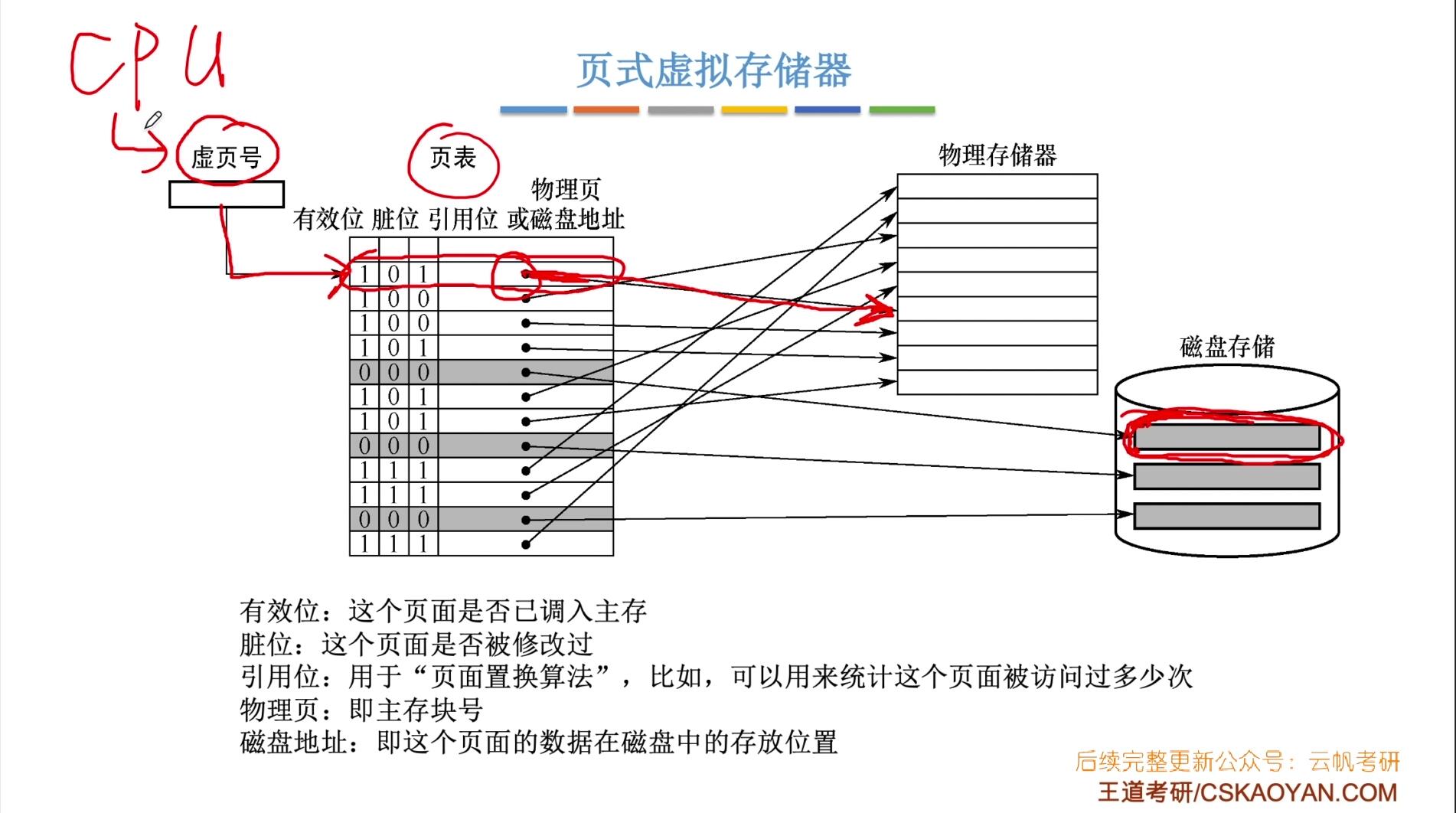

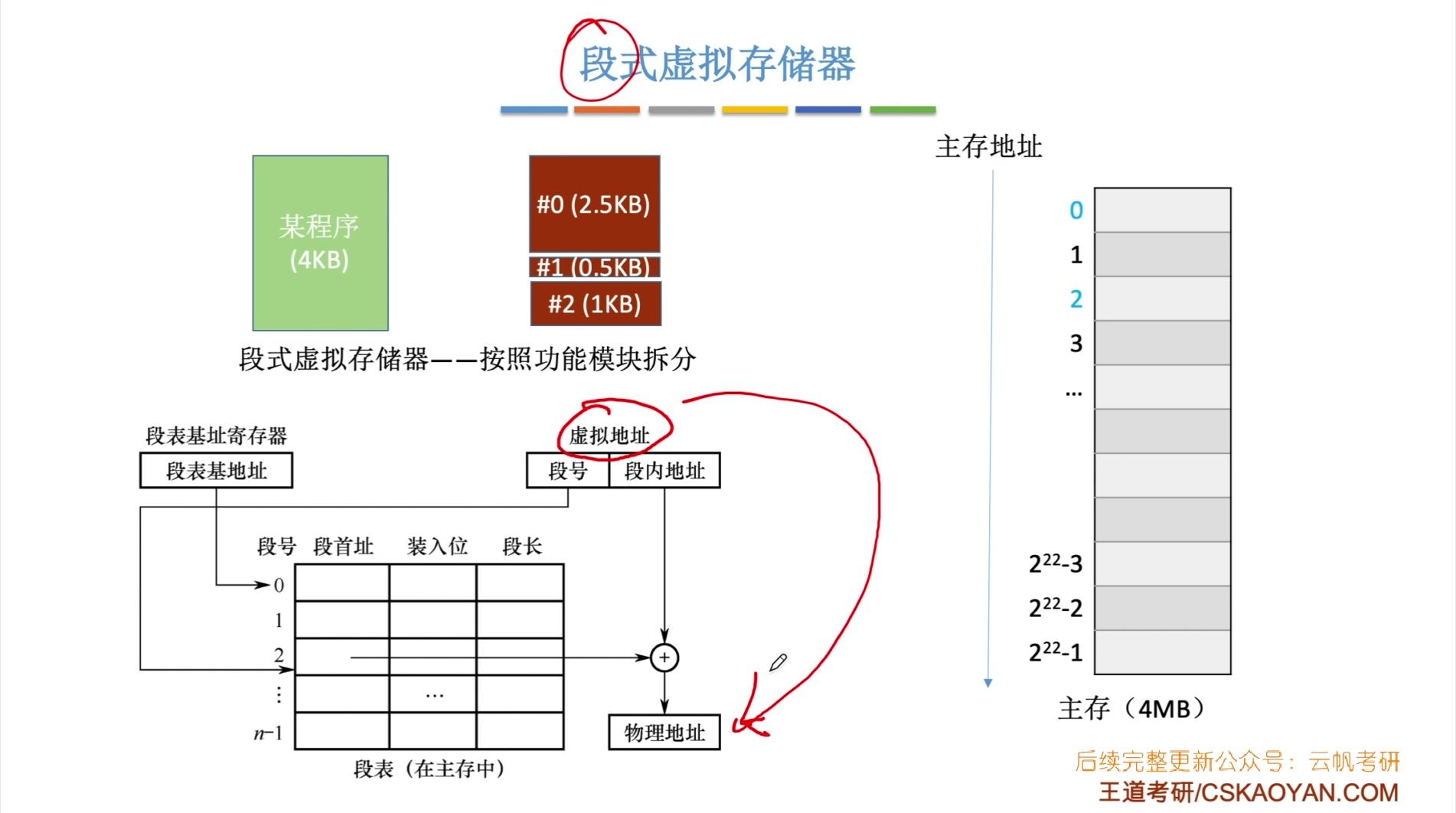

页式存储器

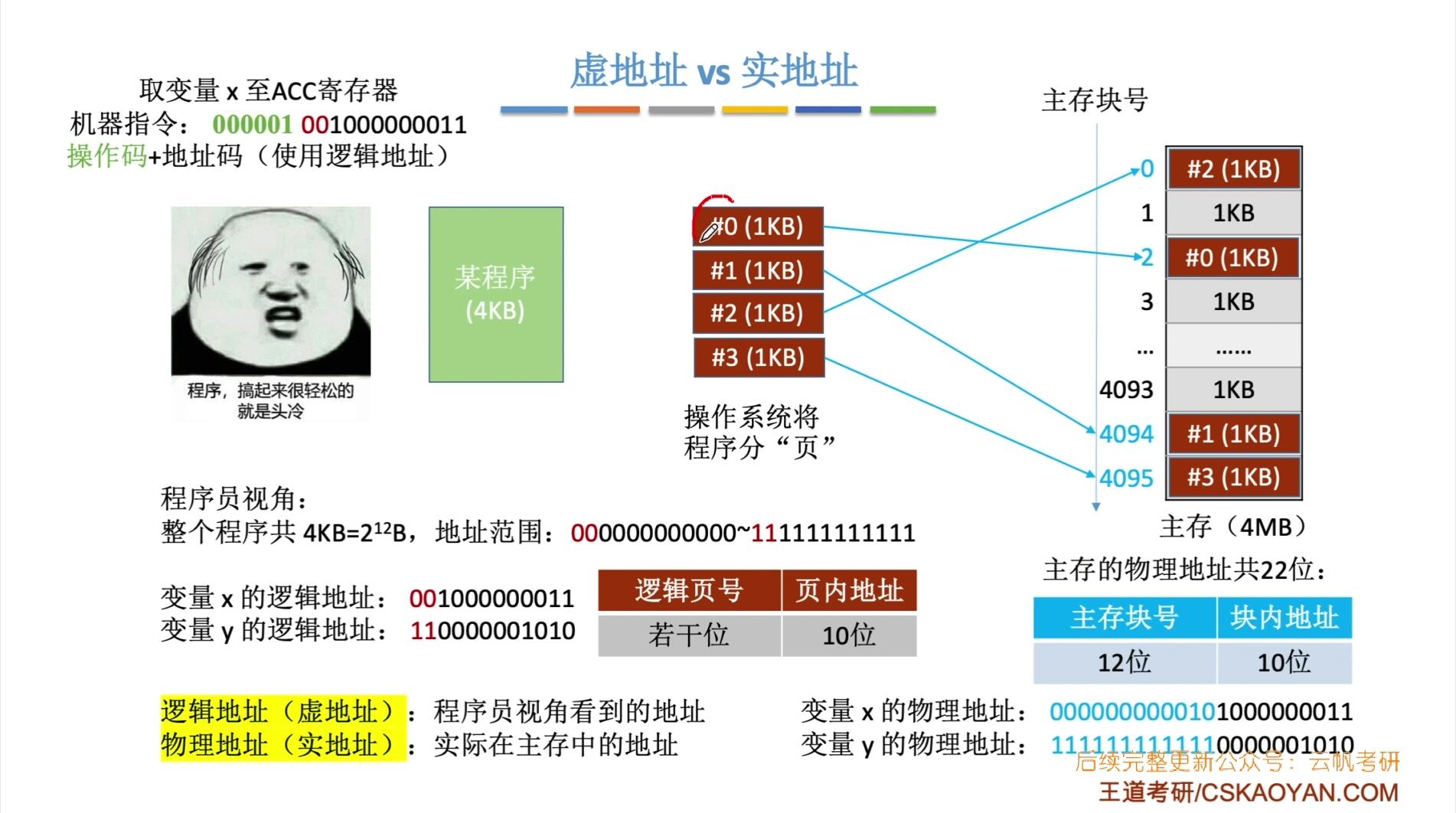

虚地址vs实地址

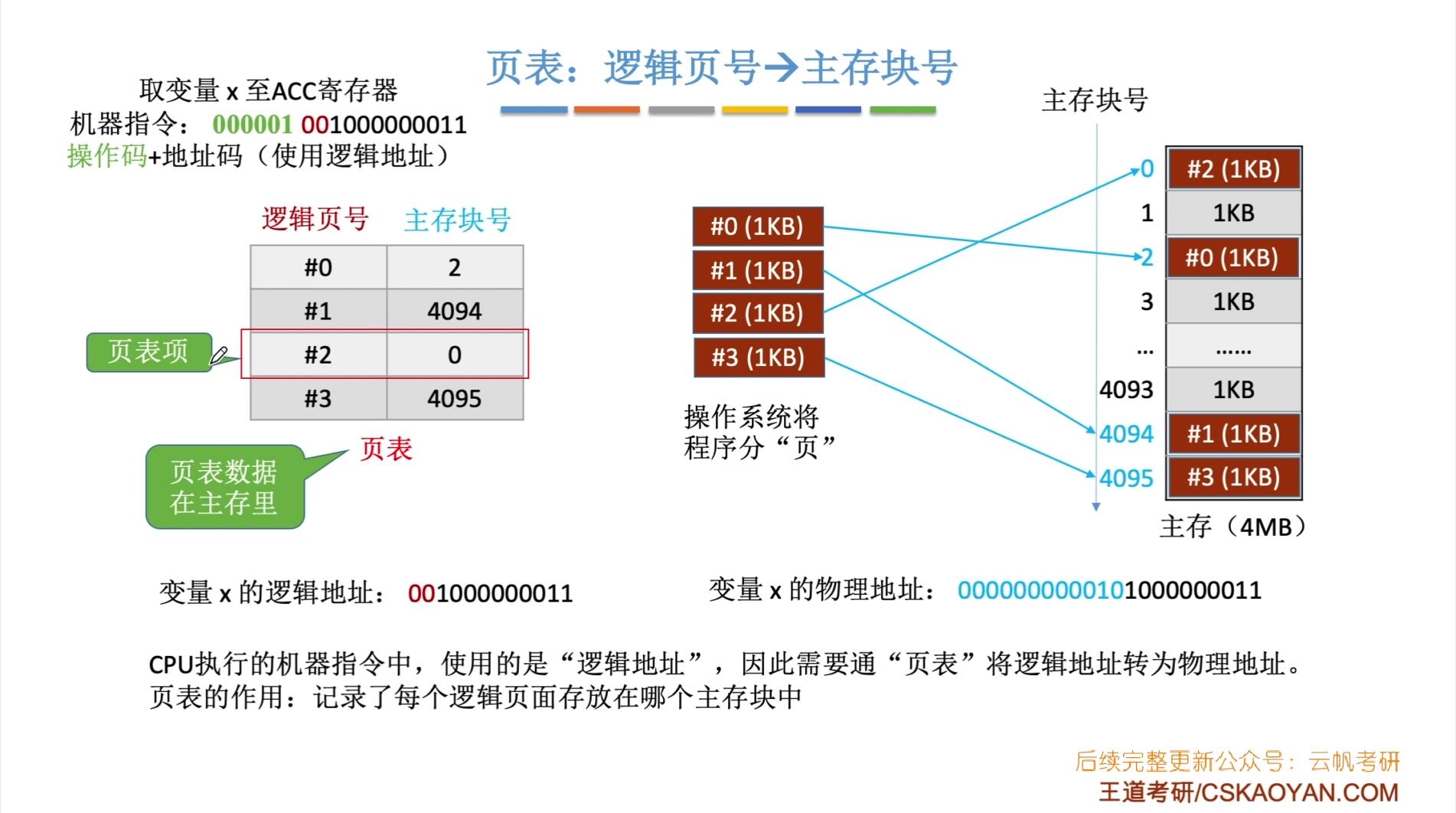

逻辑页号–>主存块号

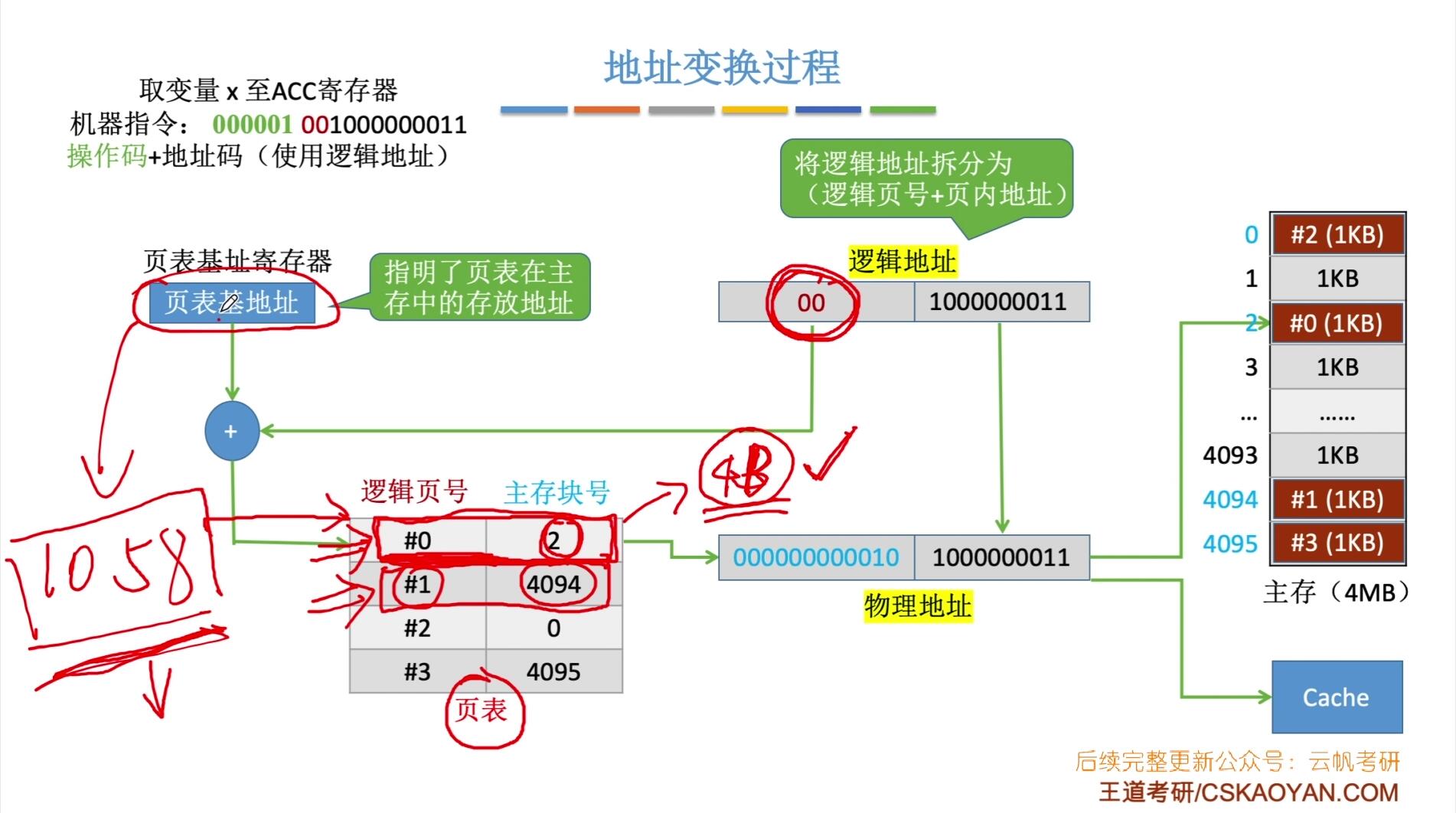

地址变换过程

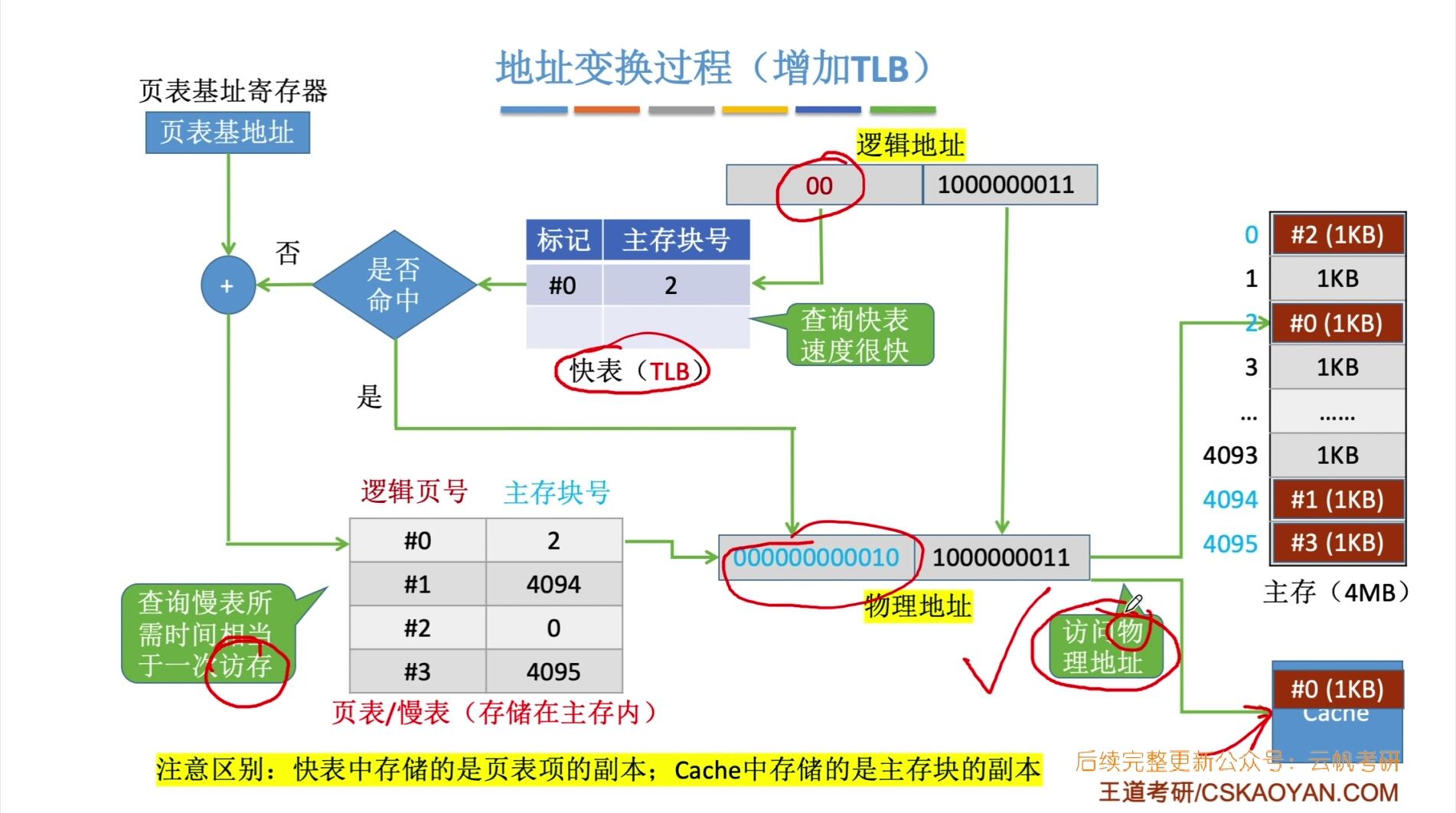

快表是在地址变换过程中起作用

cache是在获取物理地址后,访问物理地址时,起到加速作用

快表相联存储器可以按照内存寻访

(TLB)快表

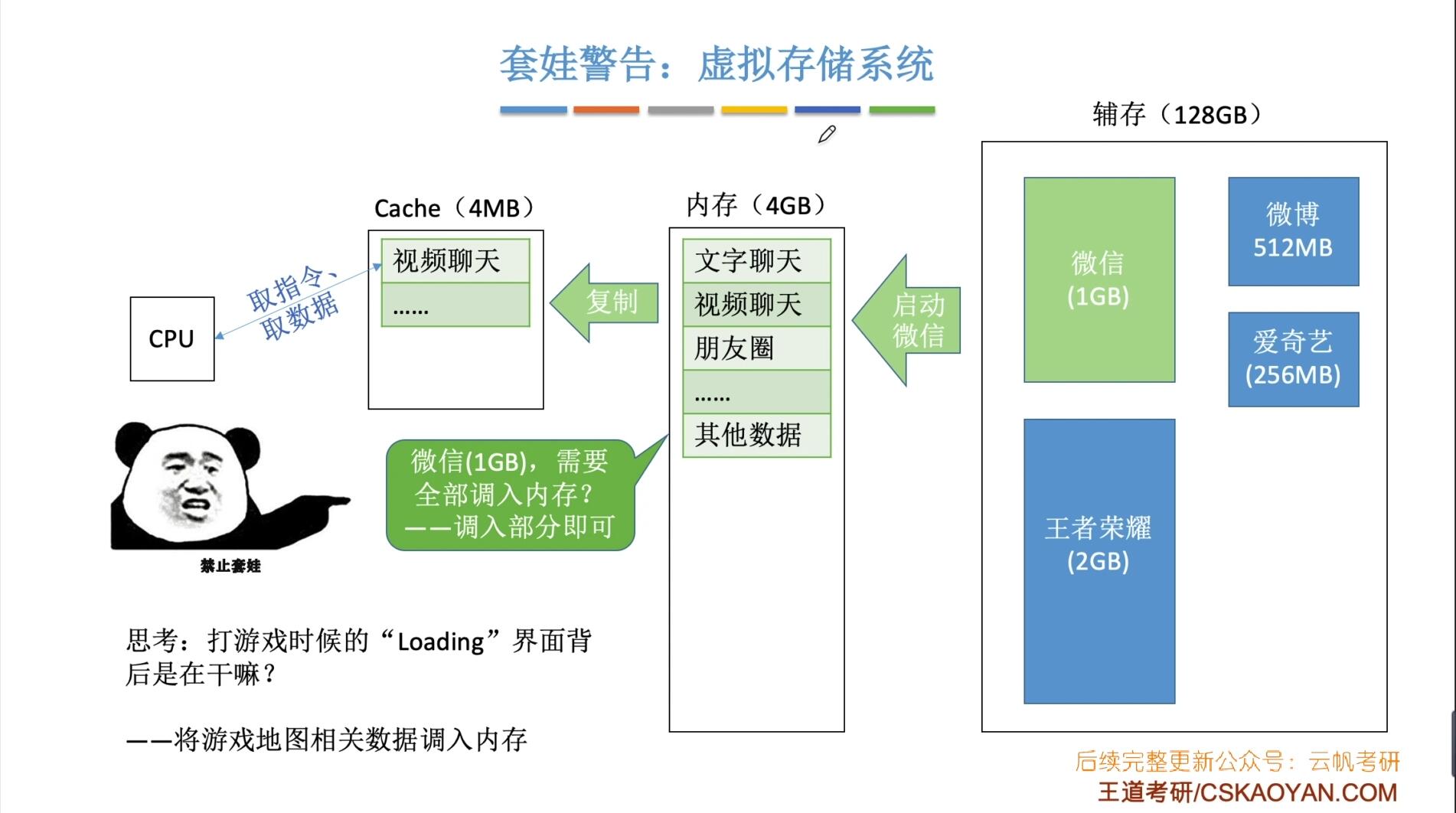

虚拟存储技术

页式虚拟存储器

层次结构

段式虚拟存储器

段页式虚拟存储器

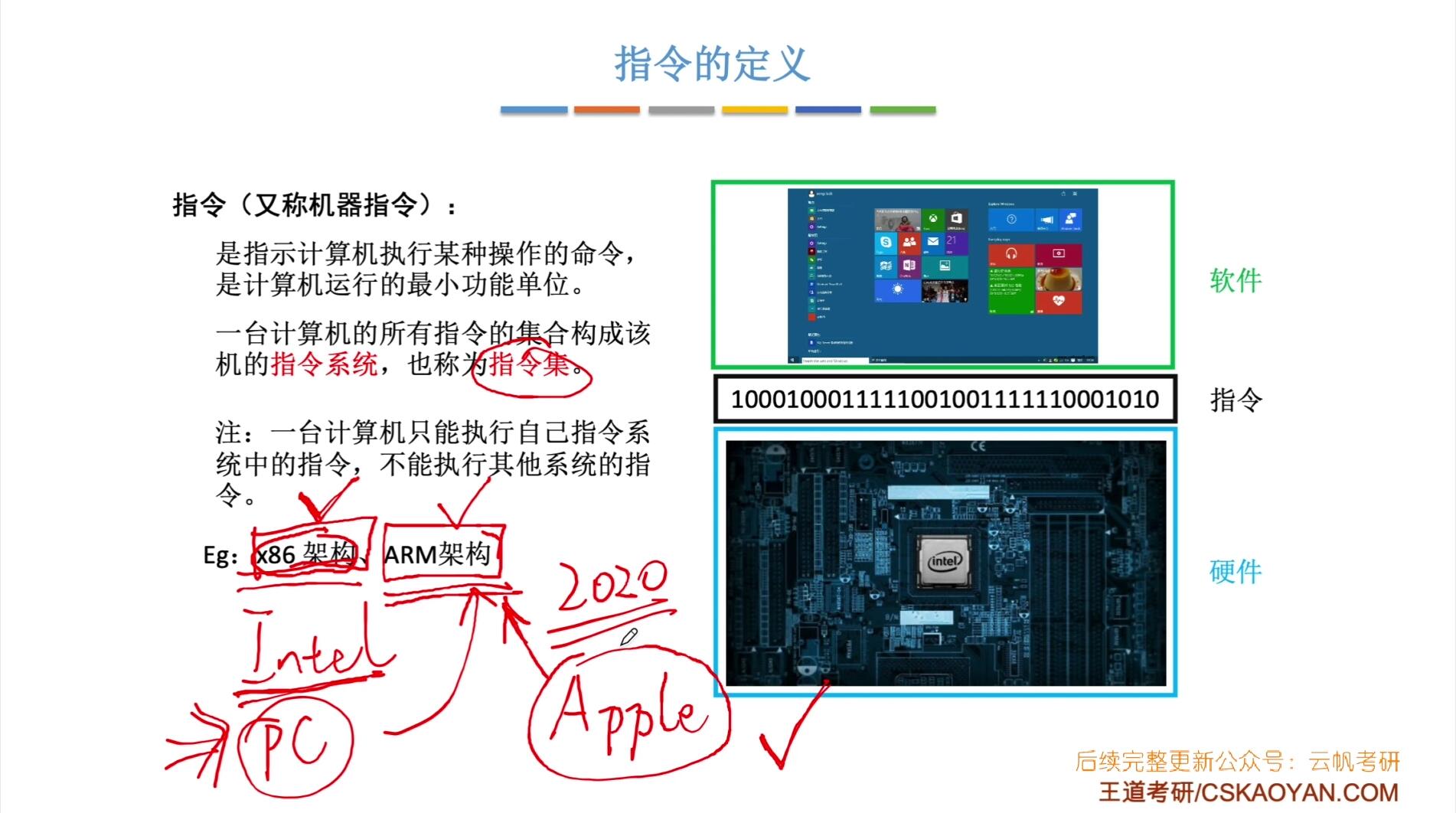

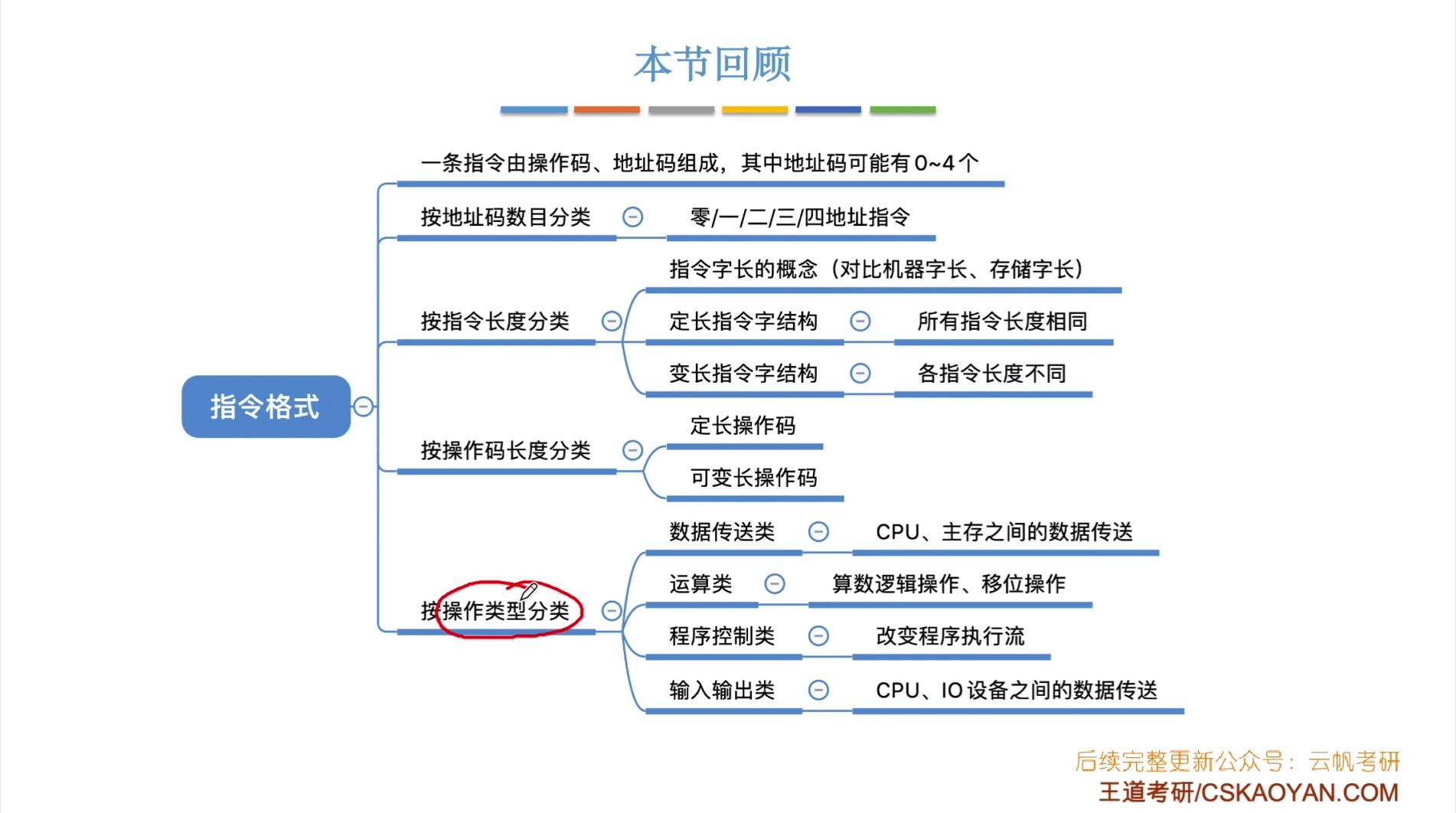

指令系统

指令定义

ARM:手机支持的指令系统架构

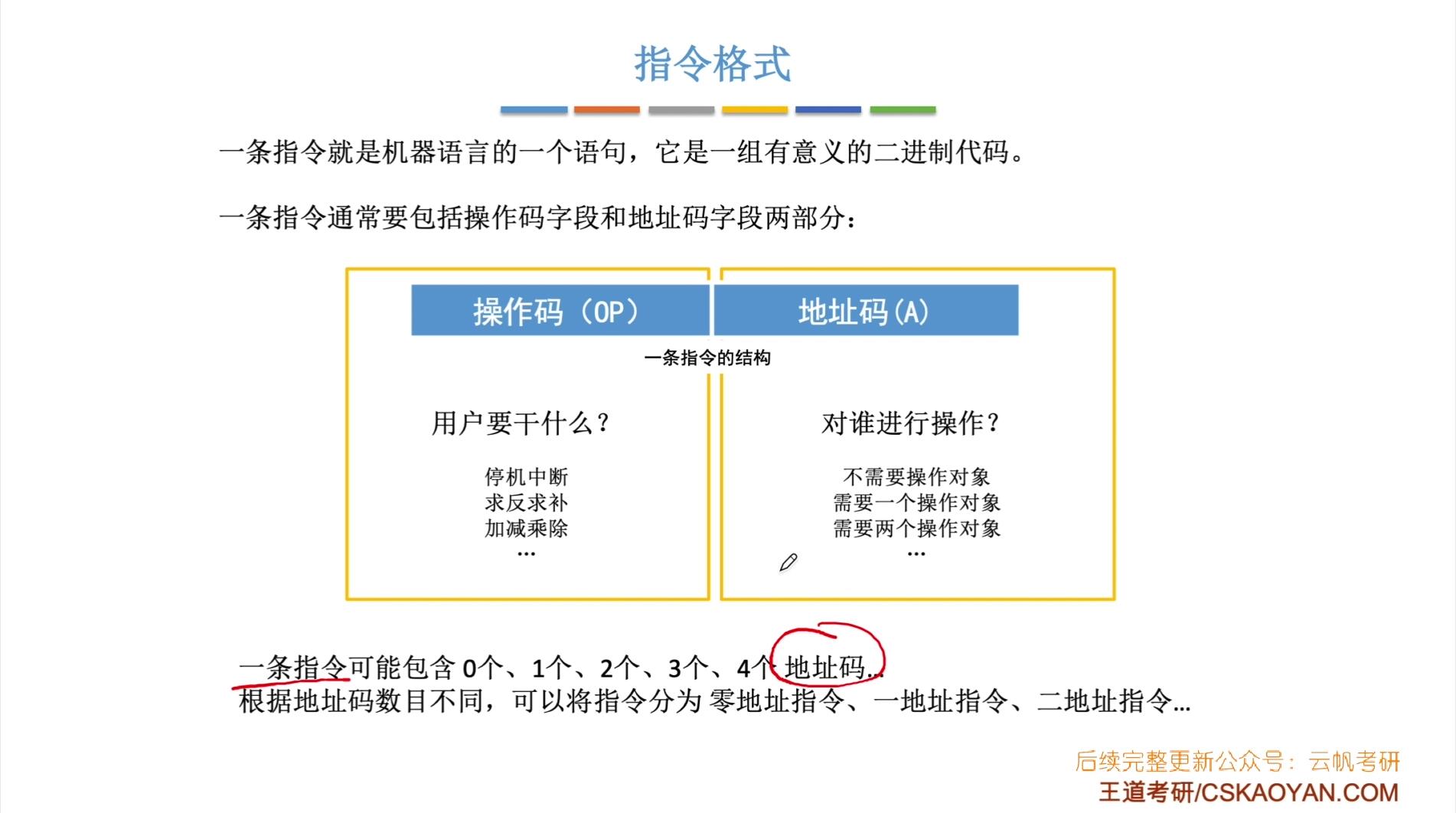

指令格式

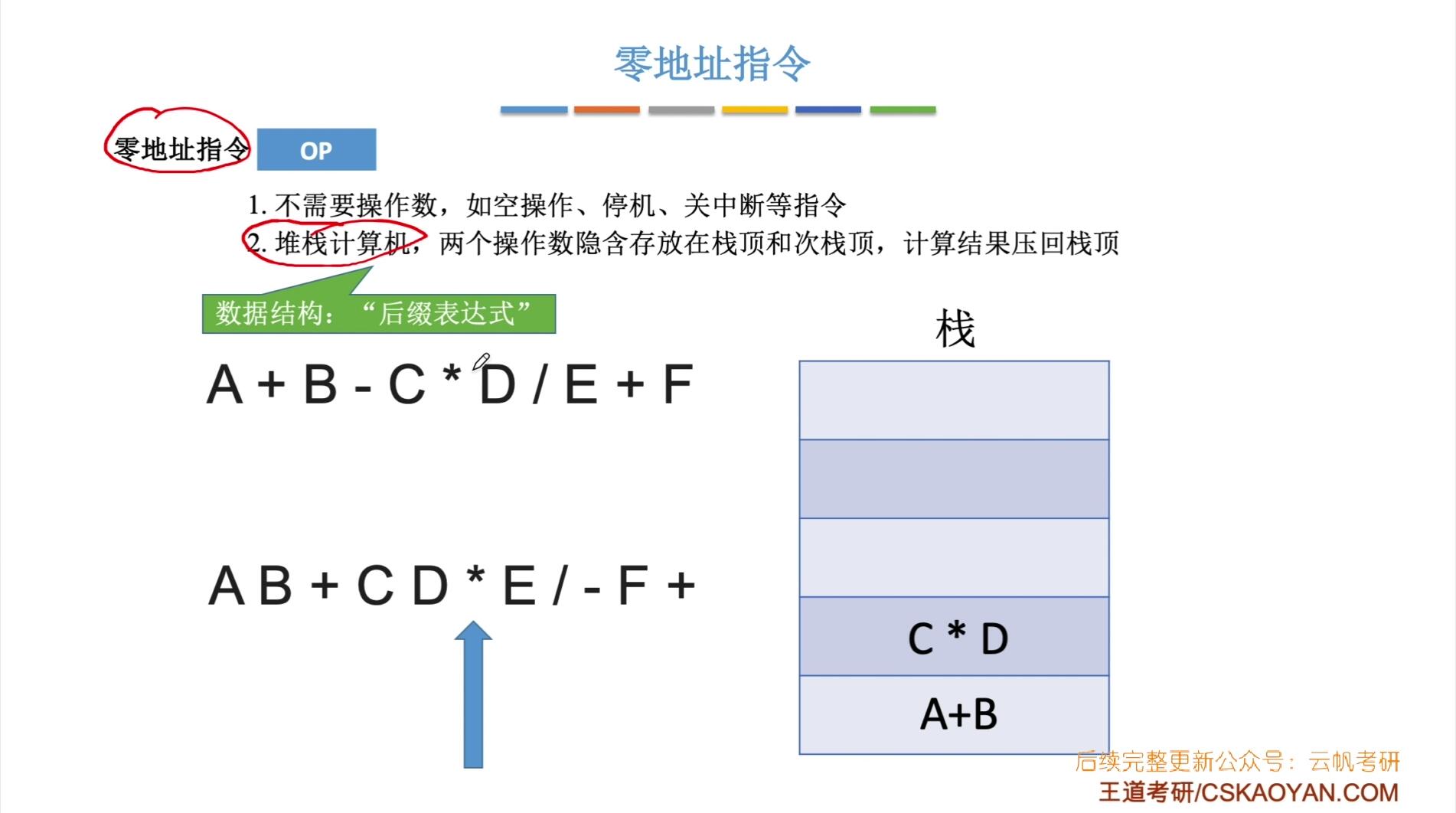

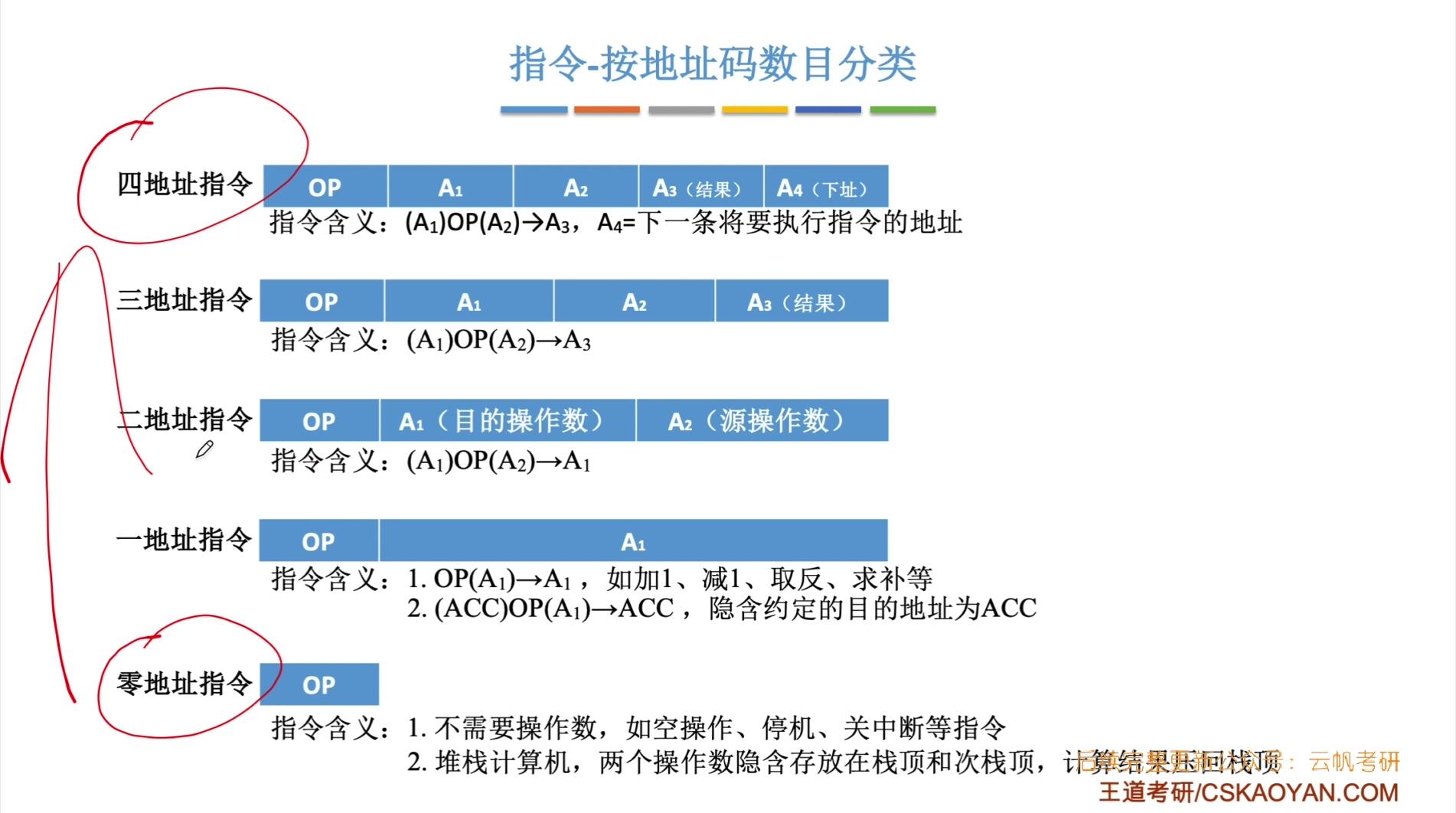

零地址指令

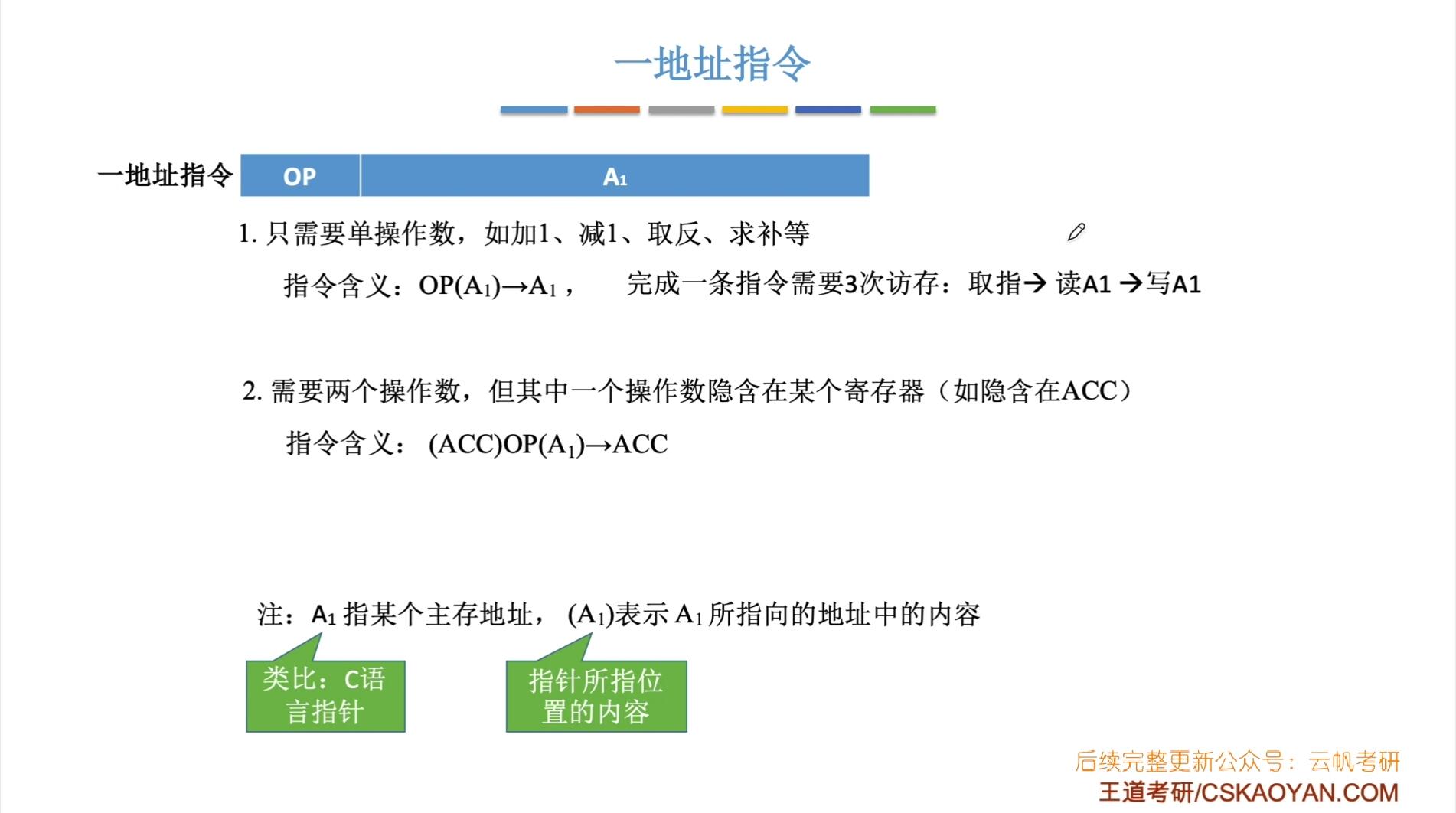

一地址指令

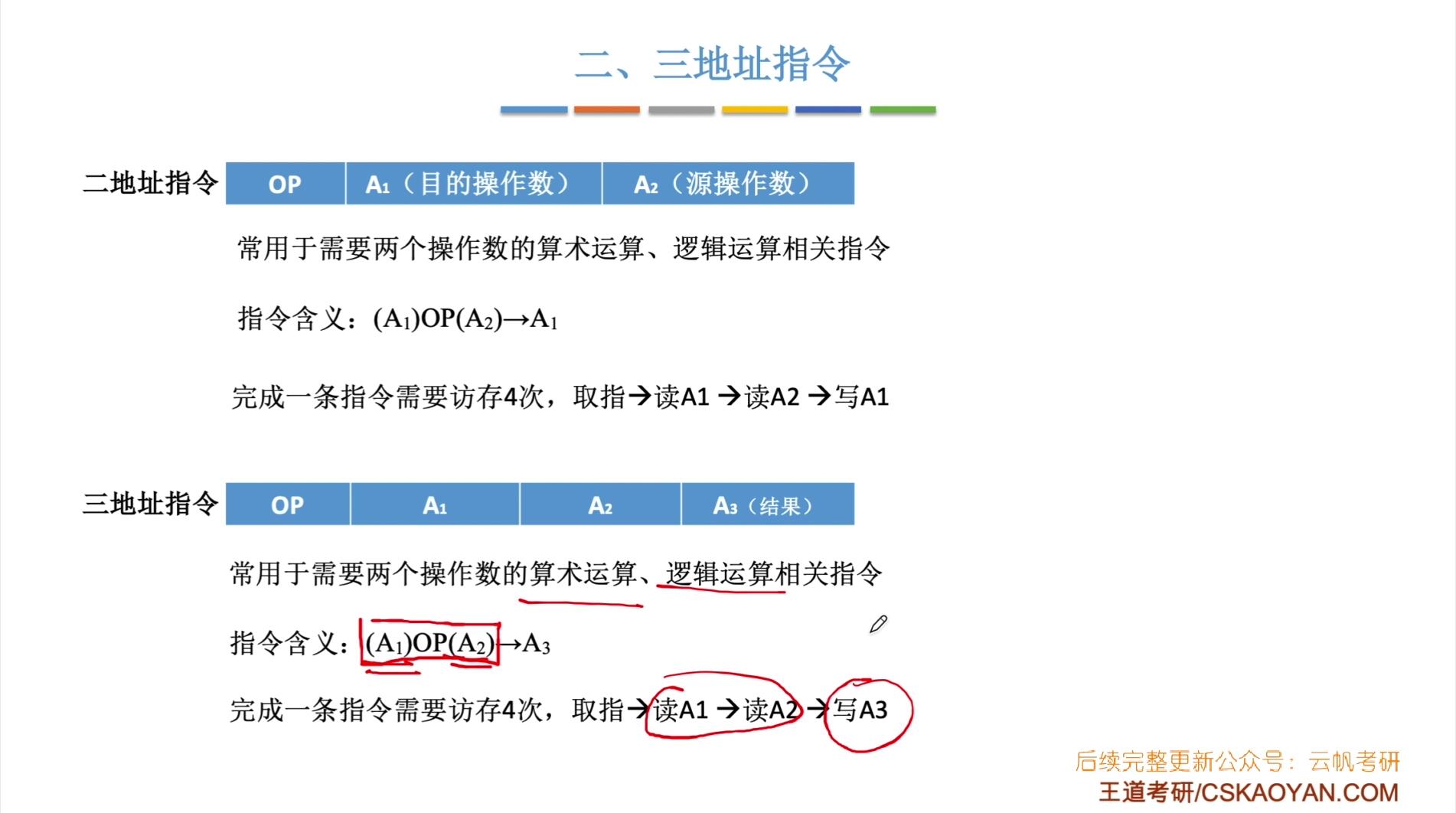

二三地址指令

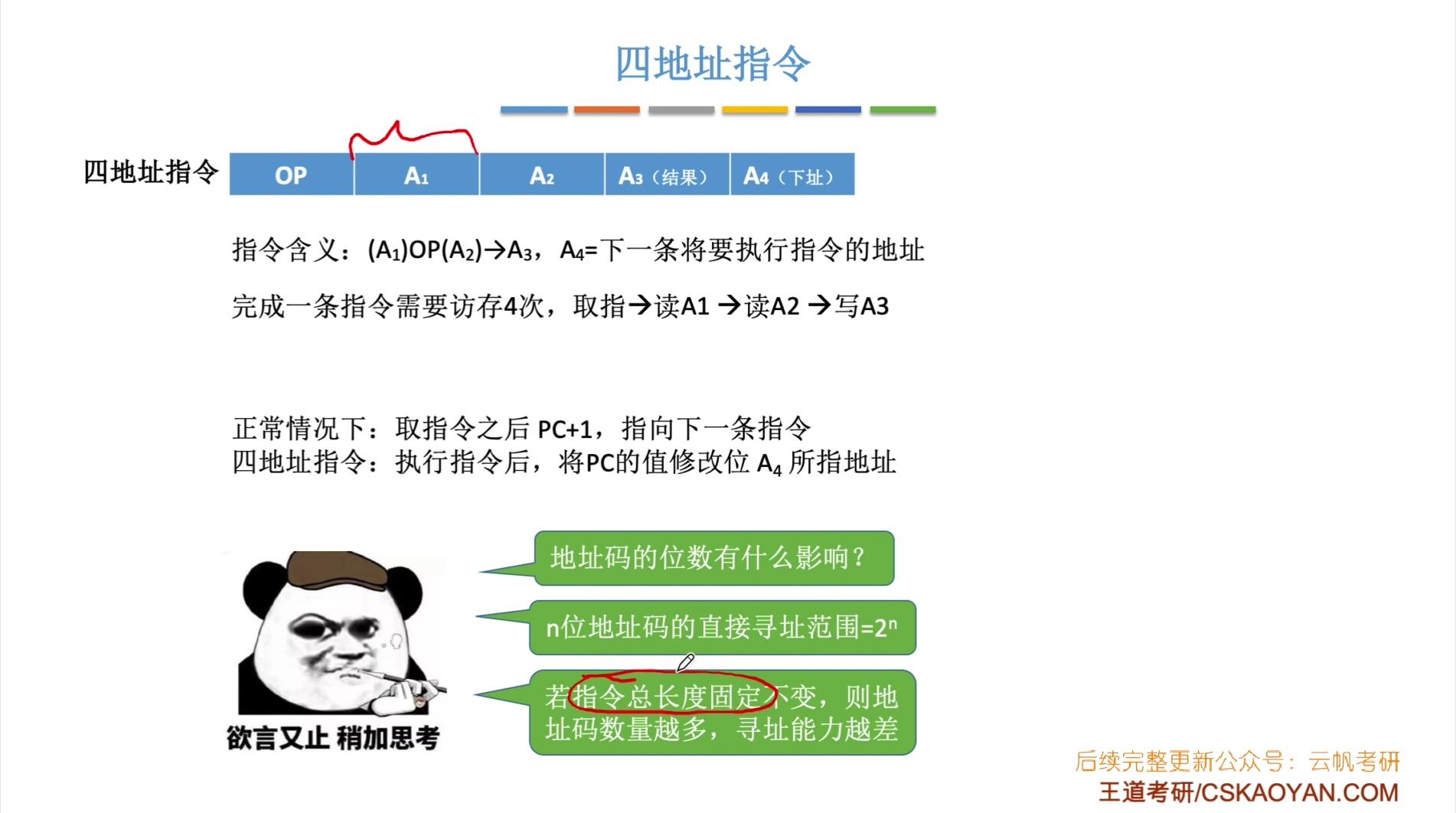

四地址

A4:下一条要执行的指令地址

指令执行后 将PC的值修改为 A4 所指的地址

指令的分类

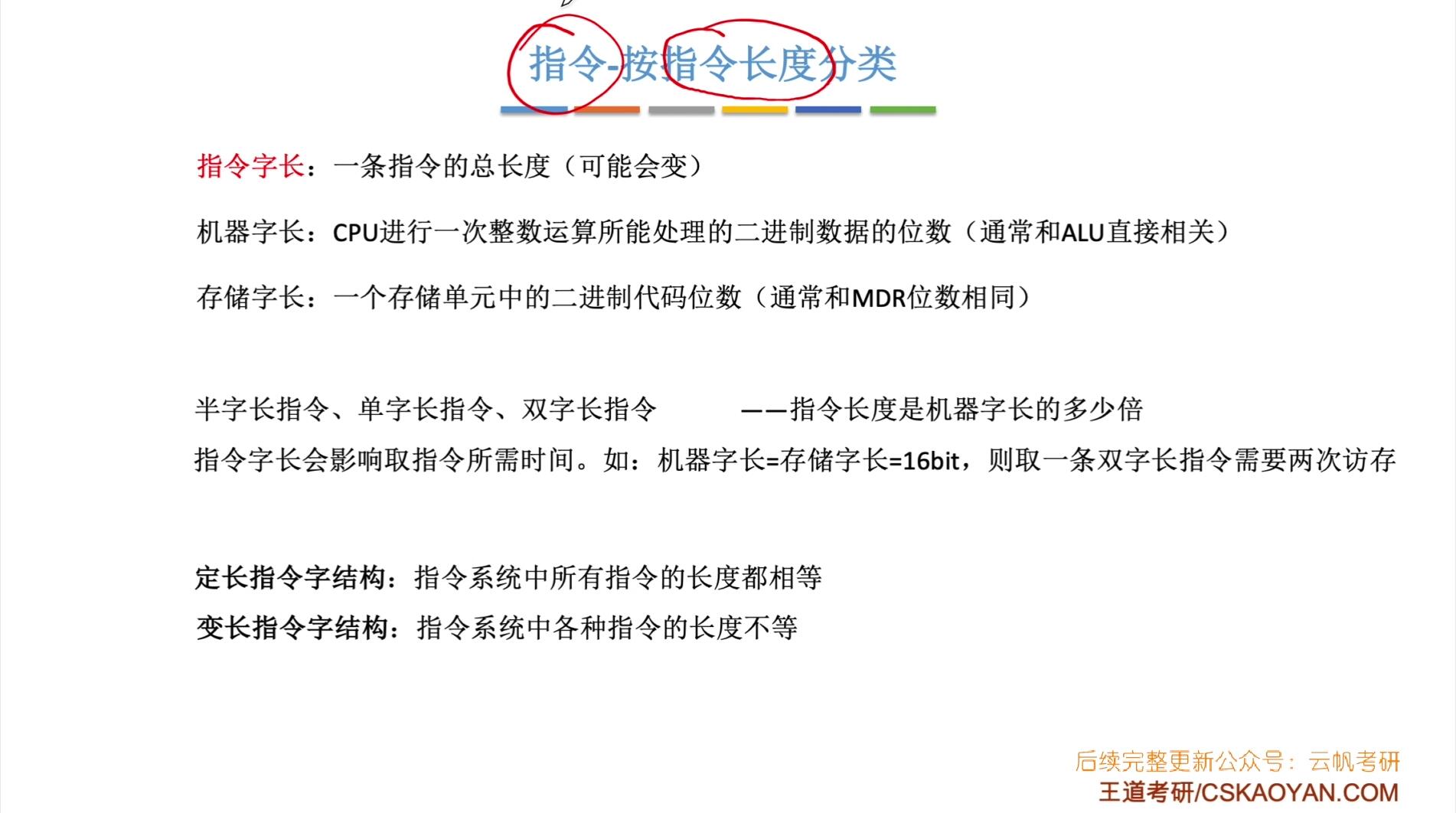

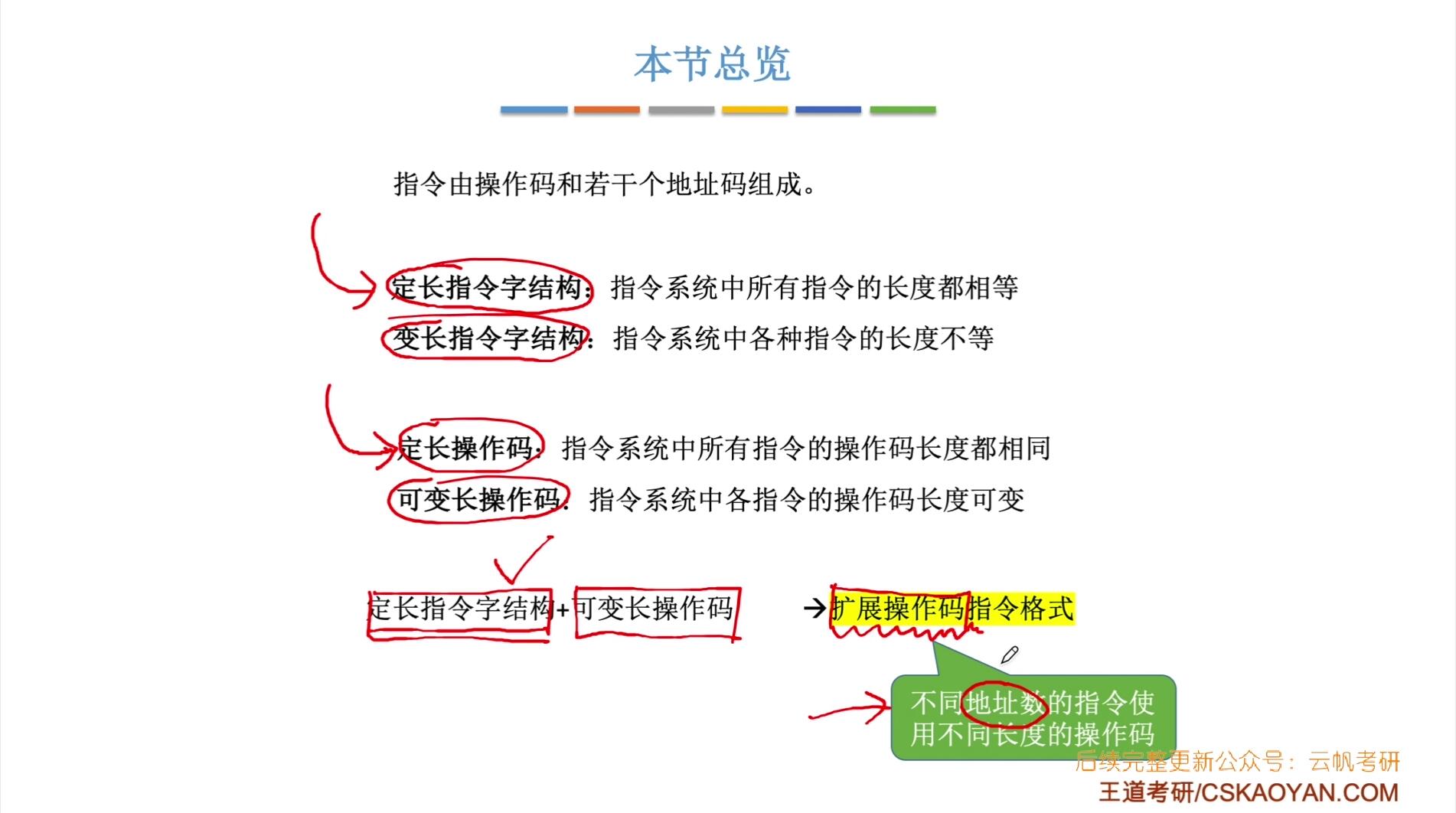

按指令长度分类

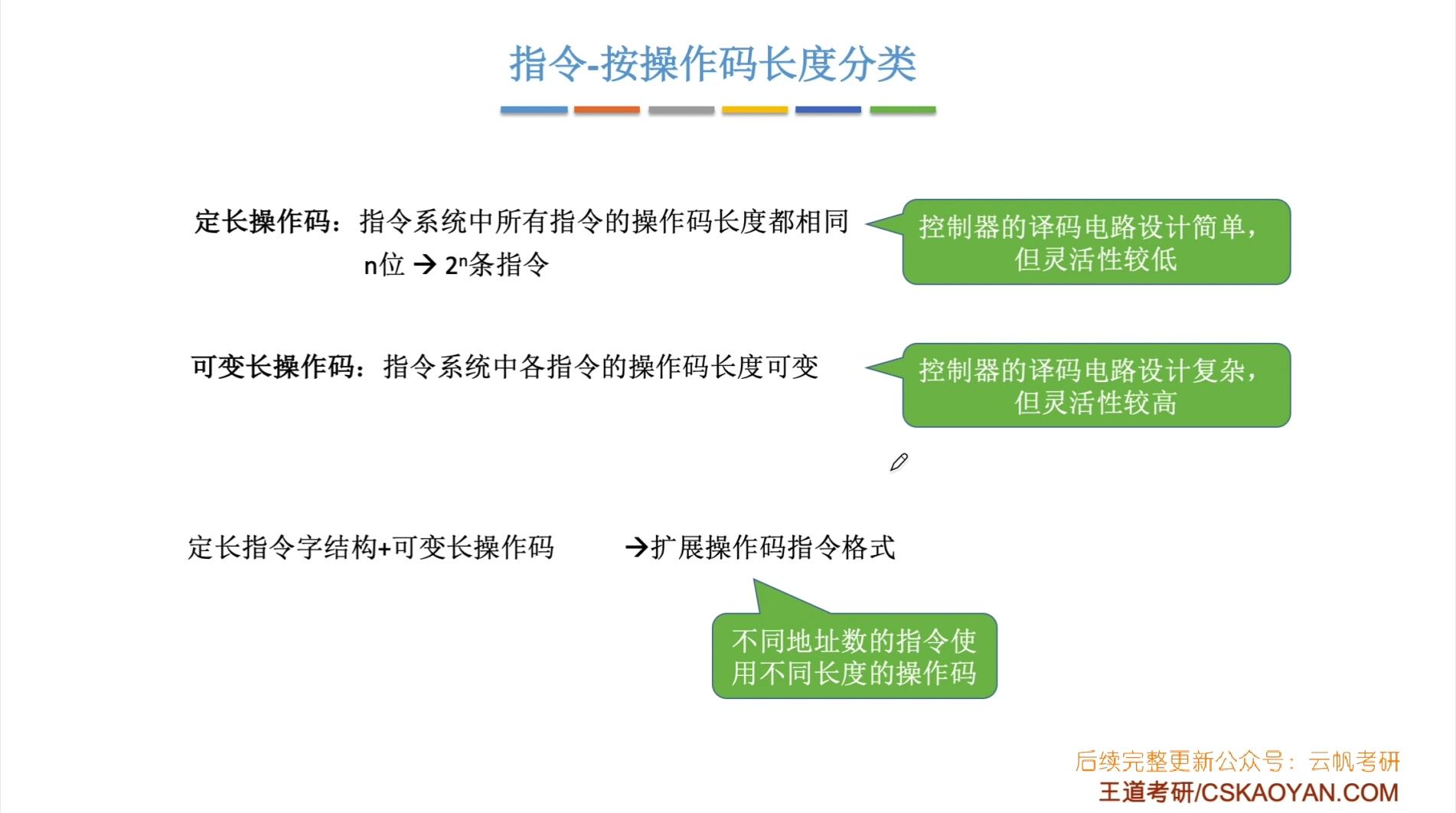

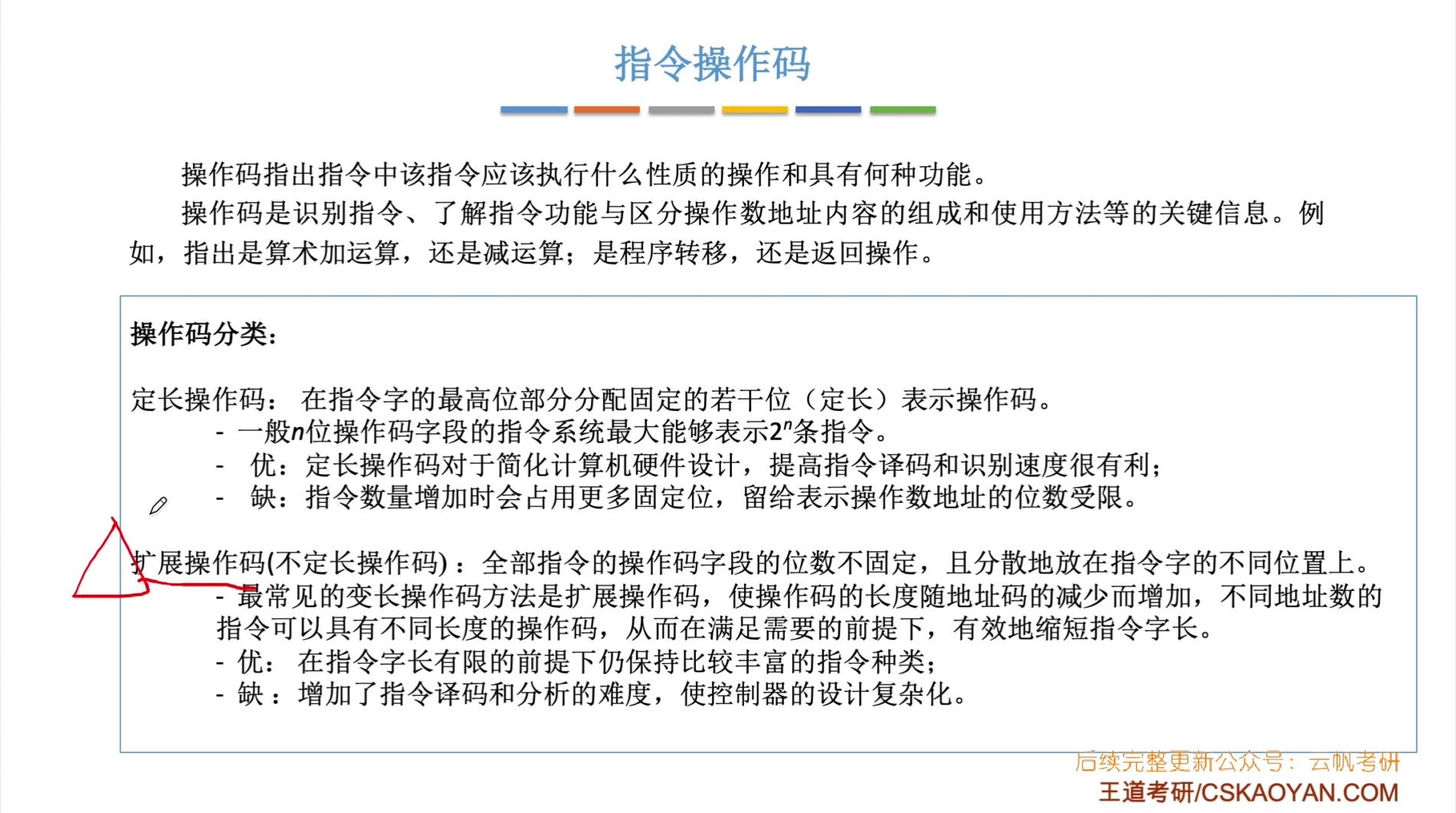

按操作码长度分类

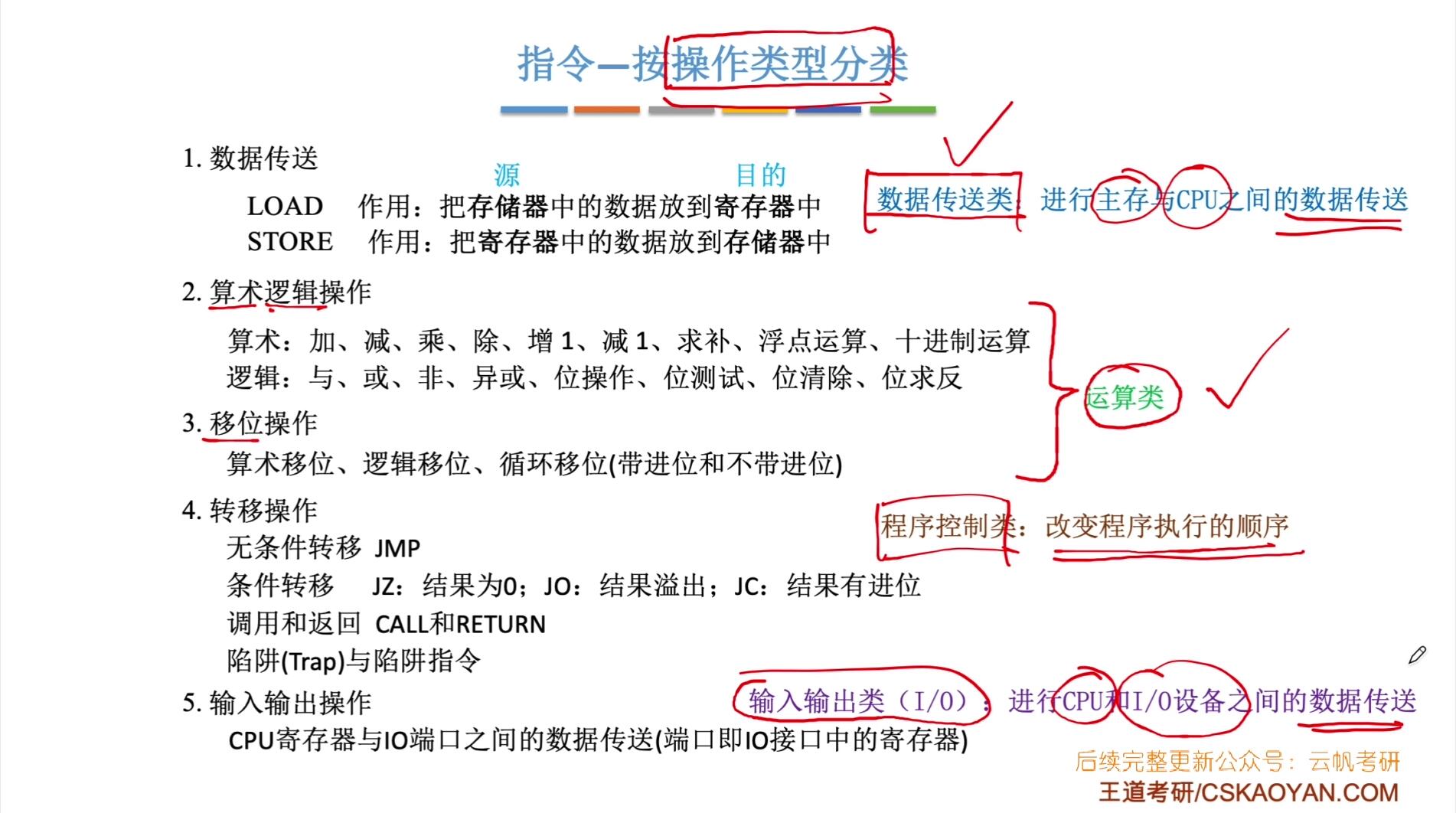

按操作类型分类

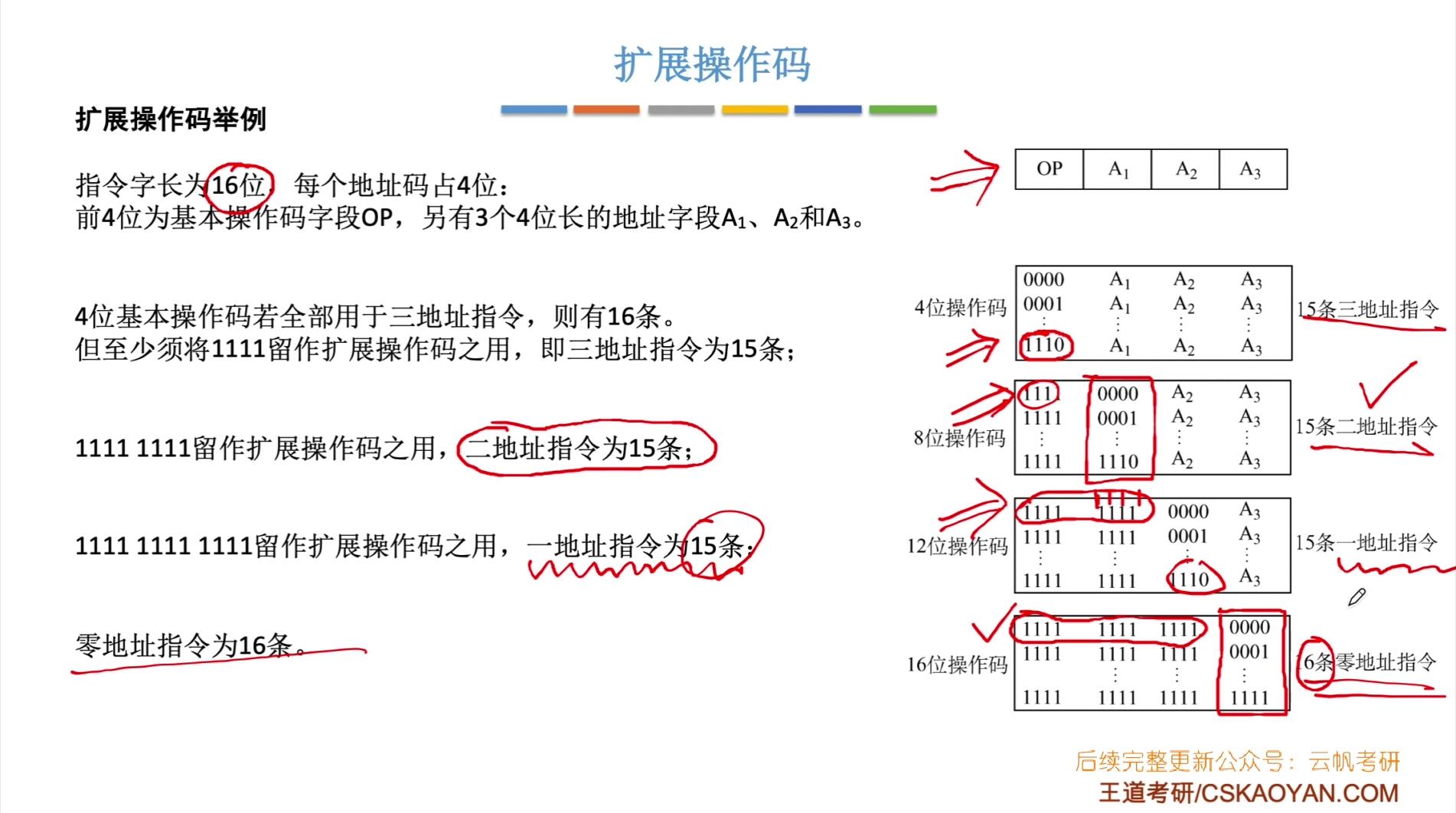

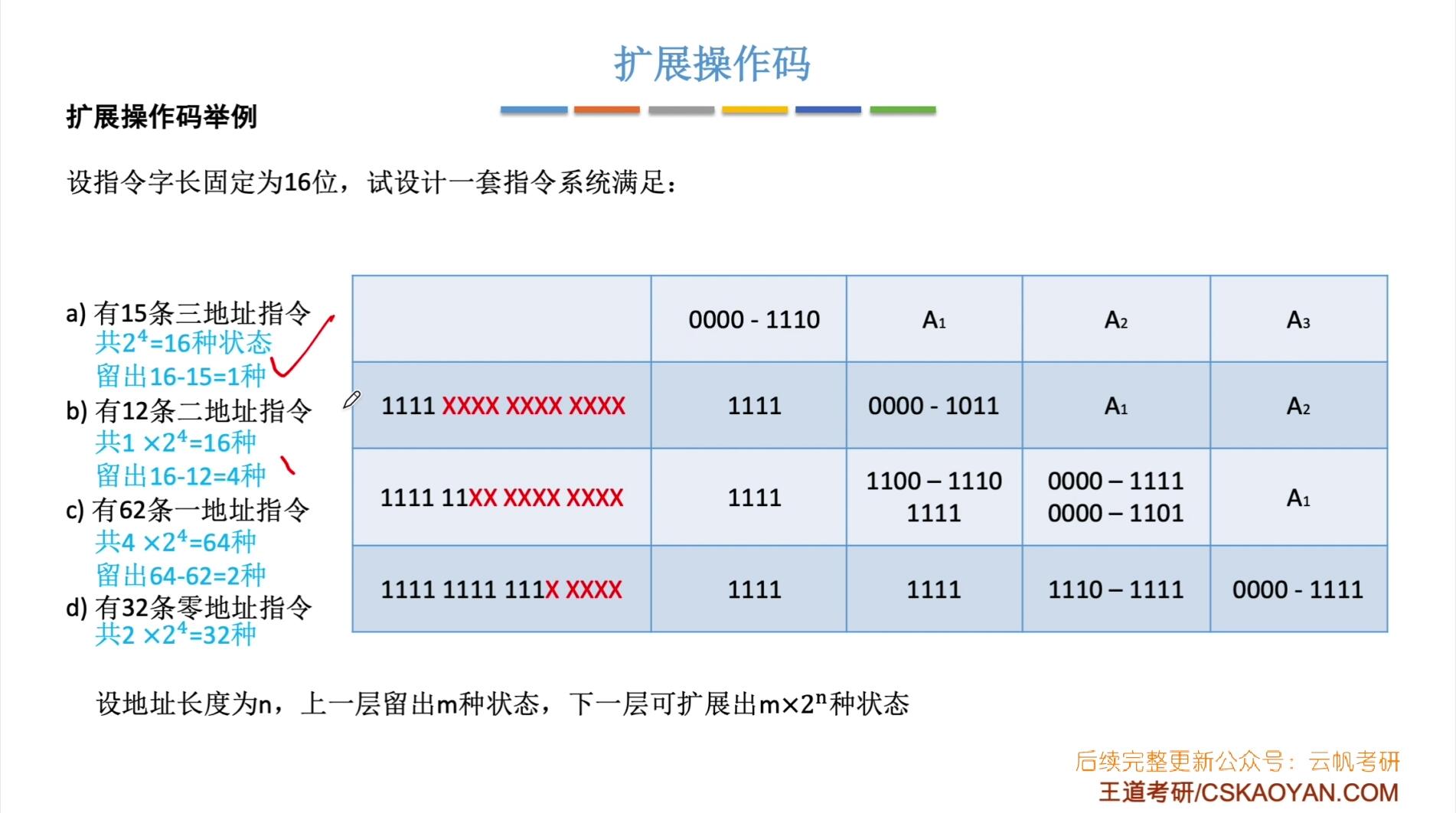

拓展操作码

前12位全1代表零地址指令

- 举例

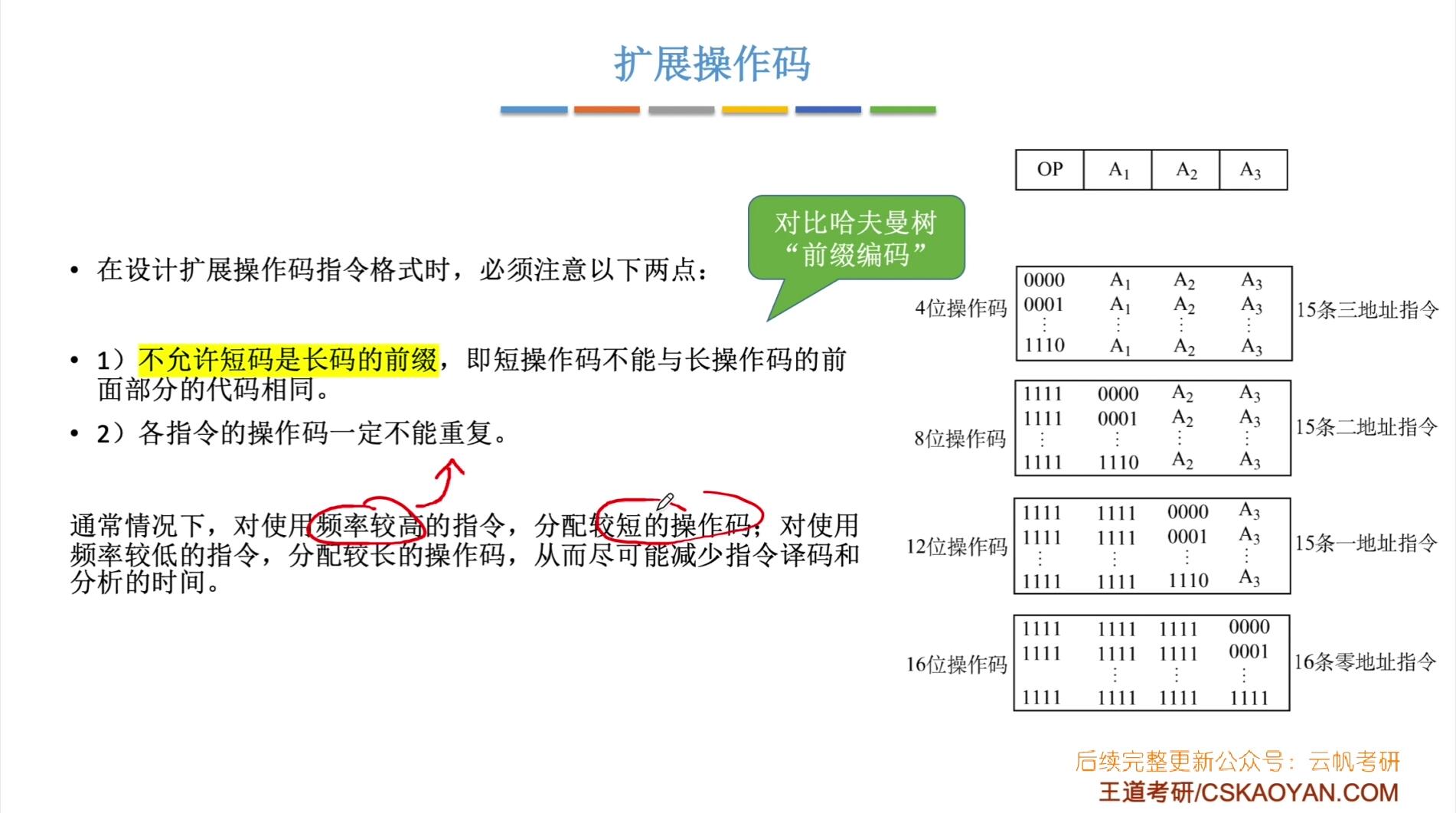

短的操作码不能是长的操作码的前缀

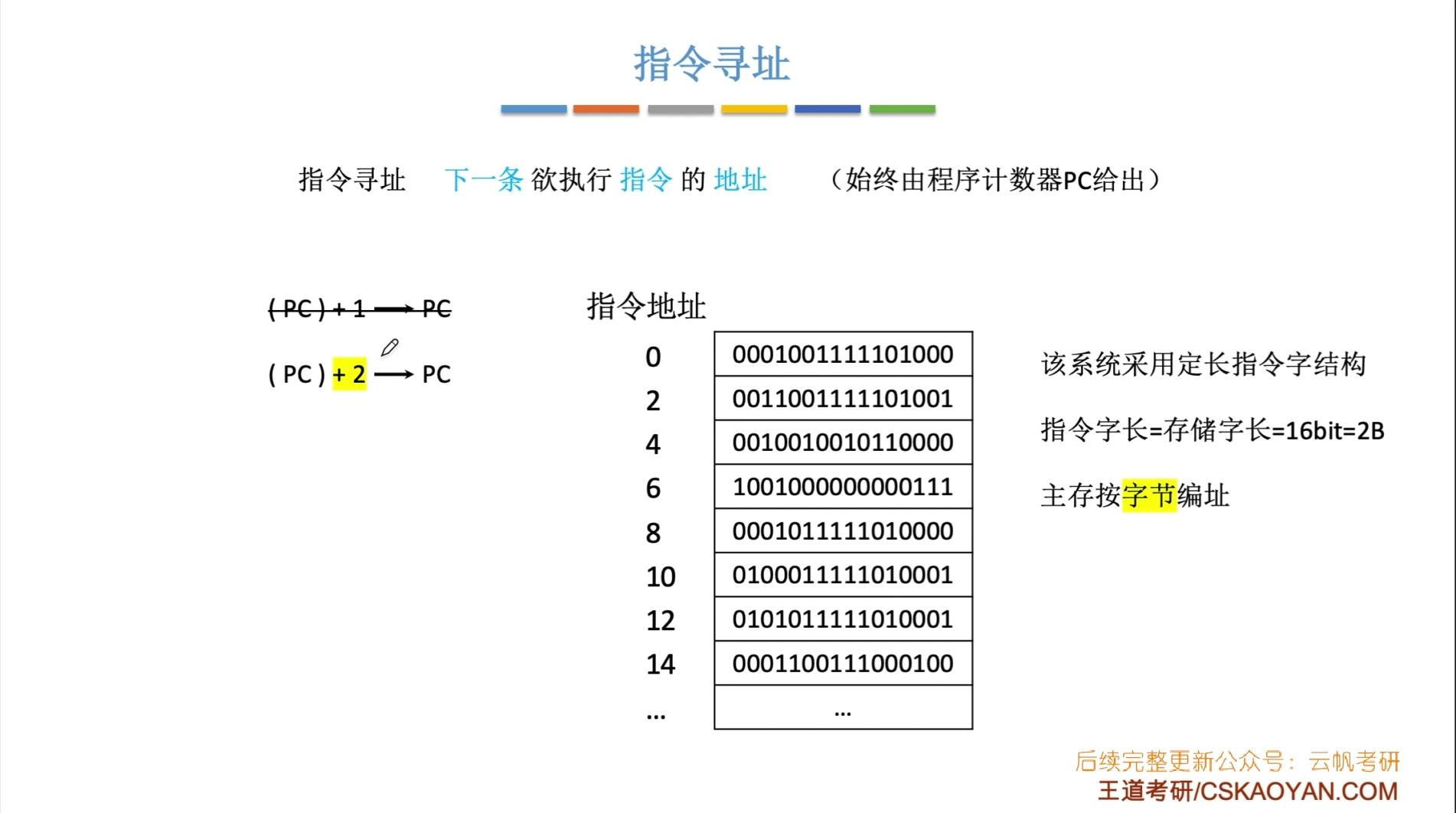

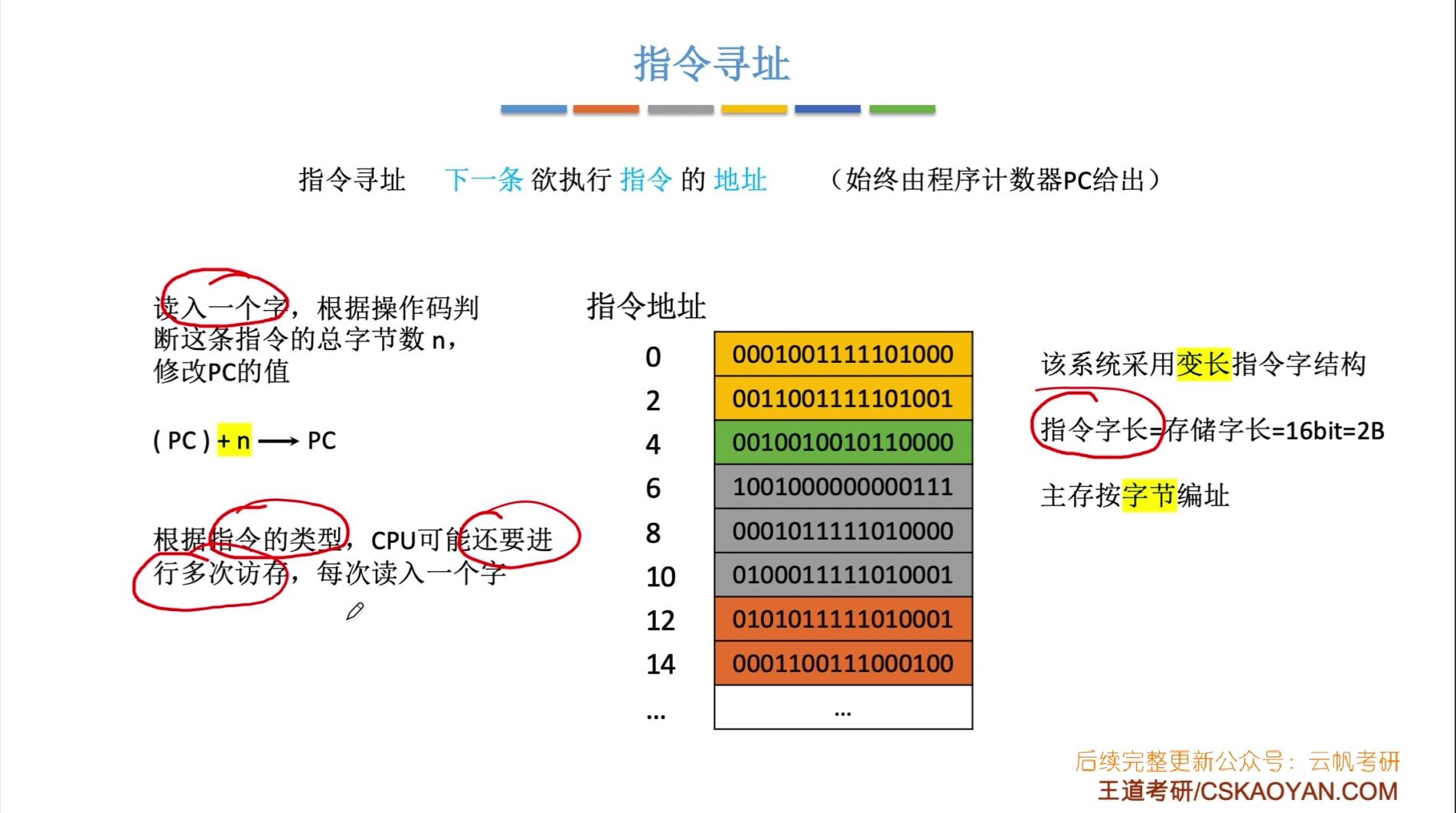

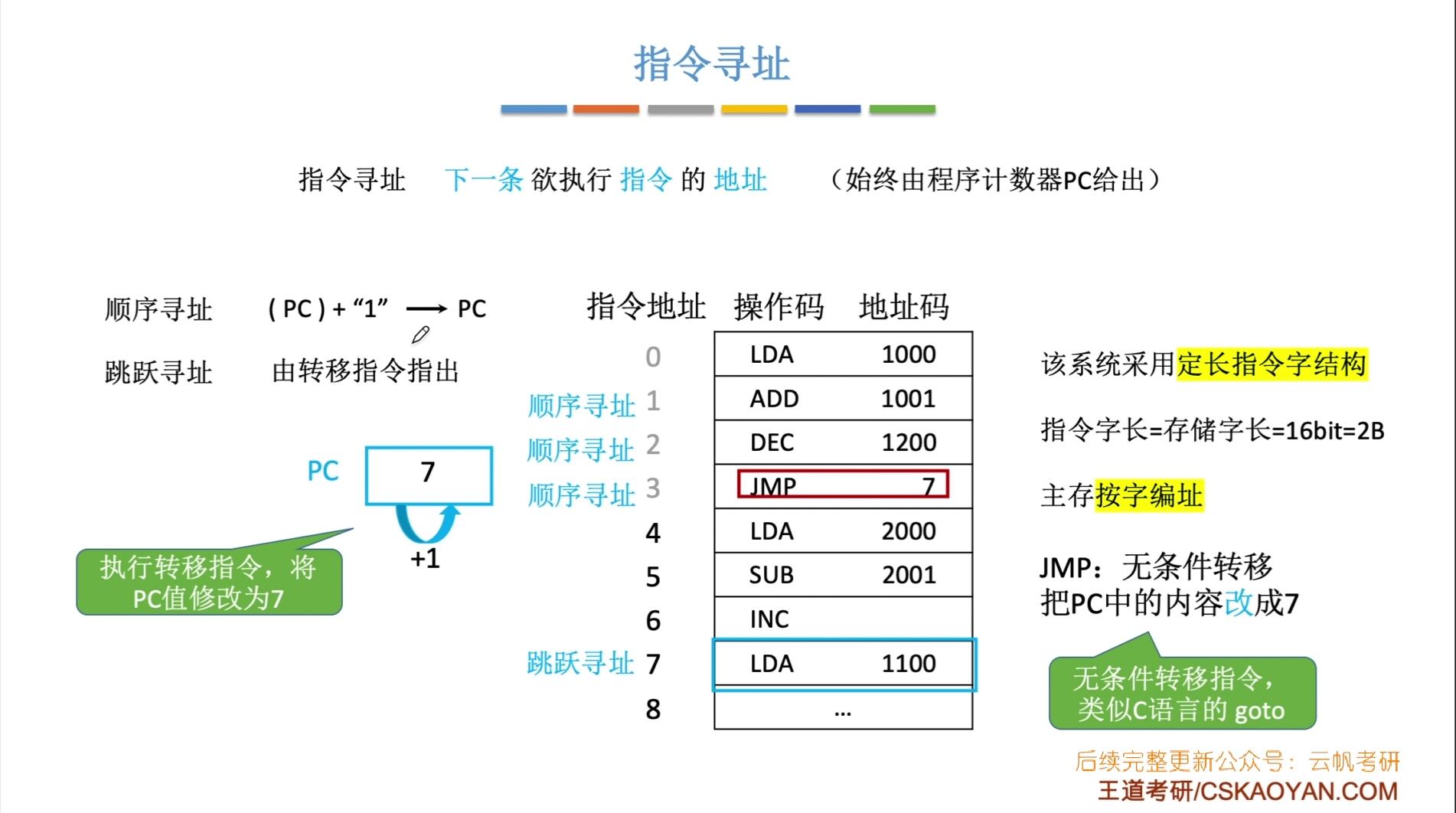

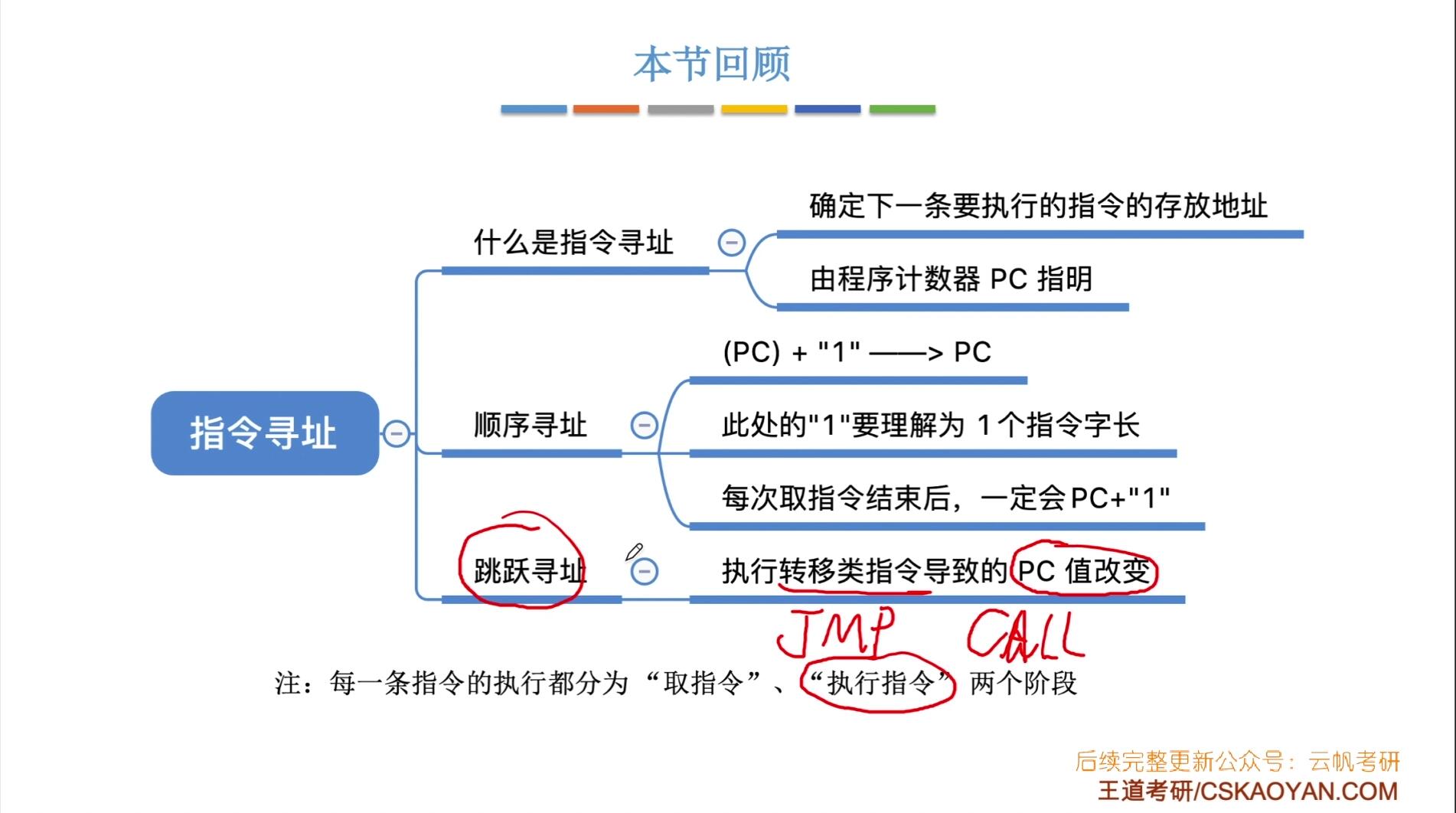

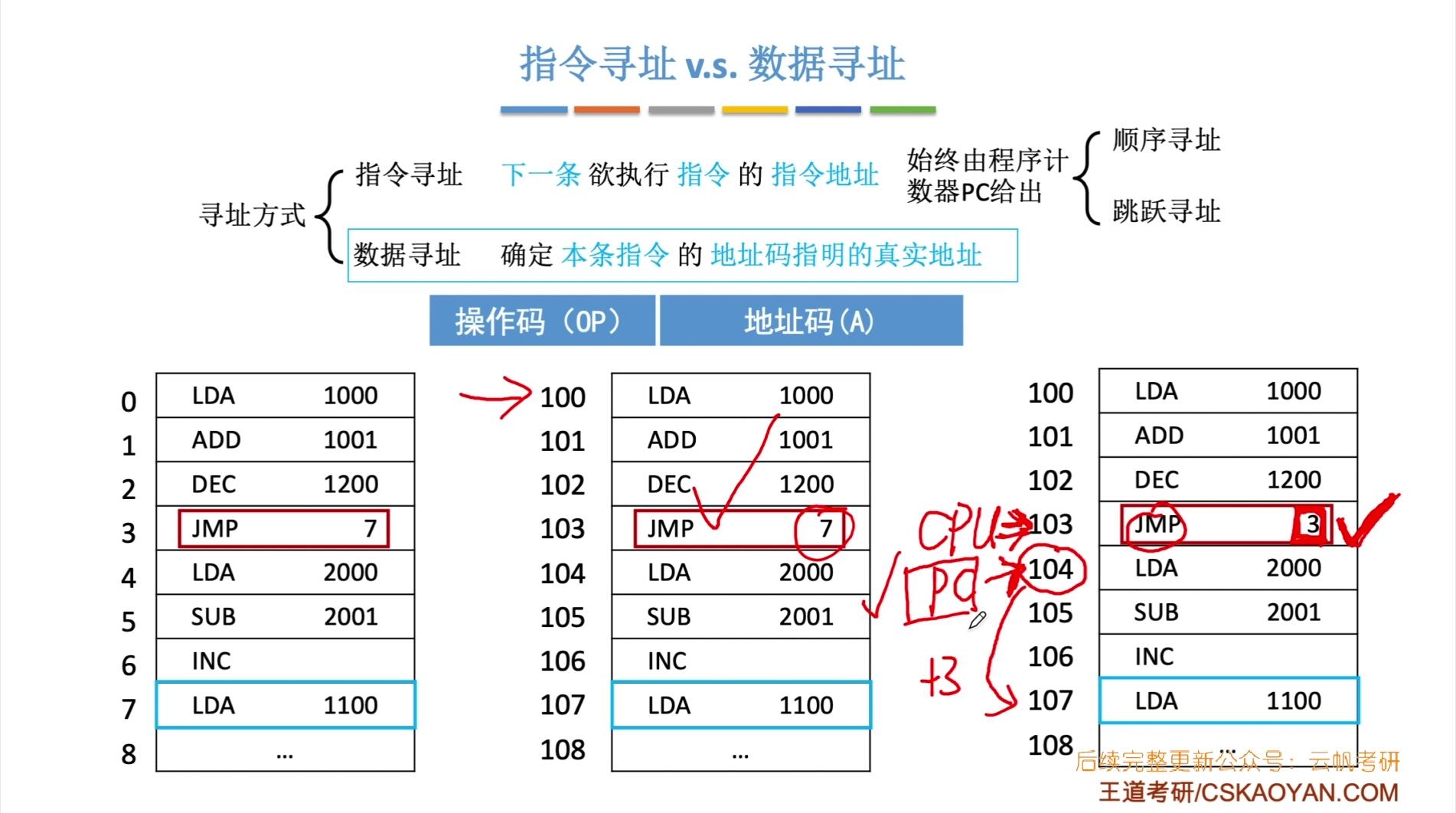

指令寻址

定长寻址

主存的编址方式决定 PC+x(指令字长)

变长寻址

跳跃寻址

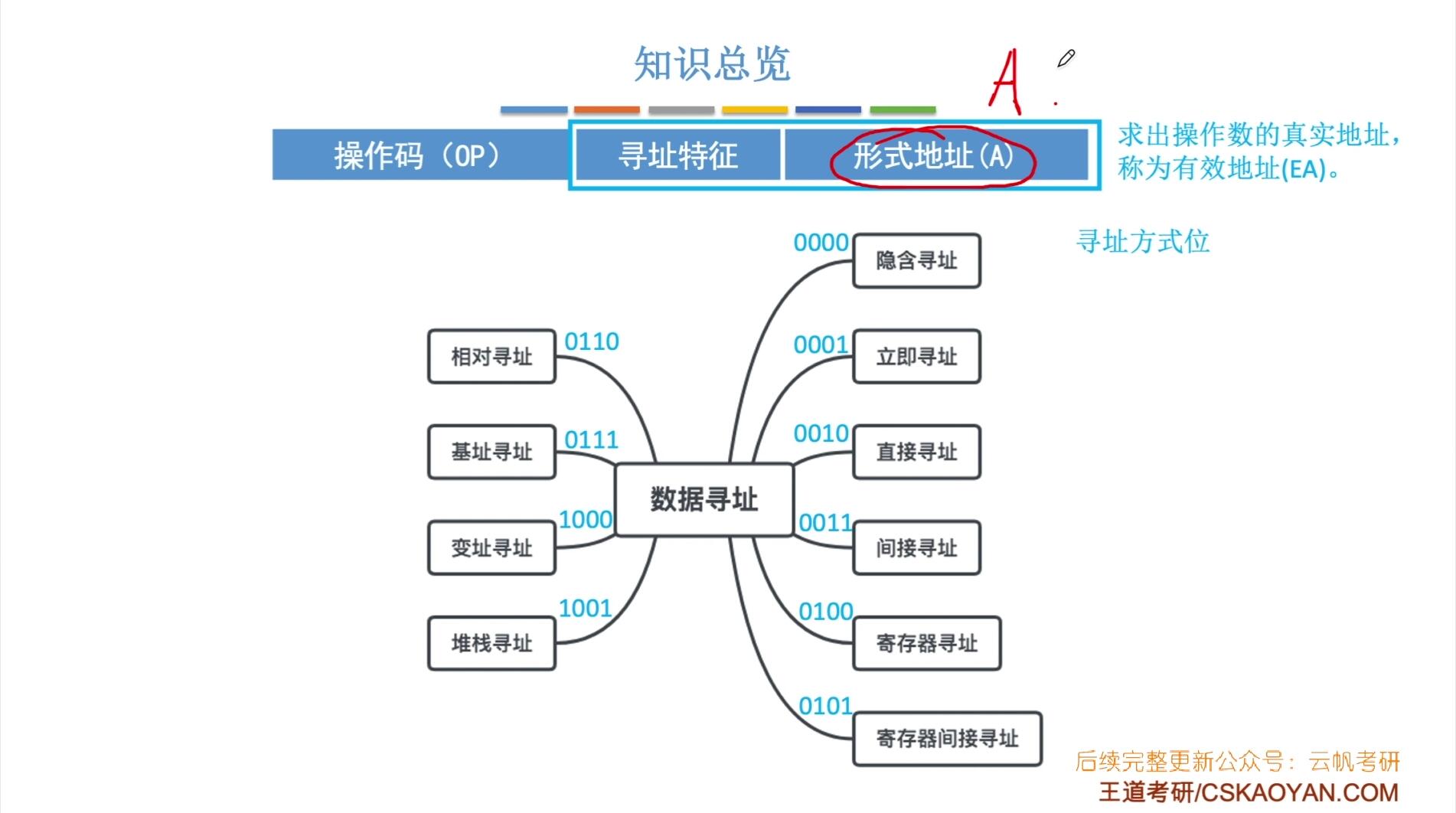

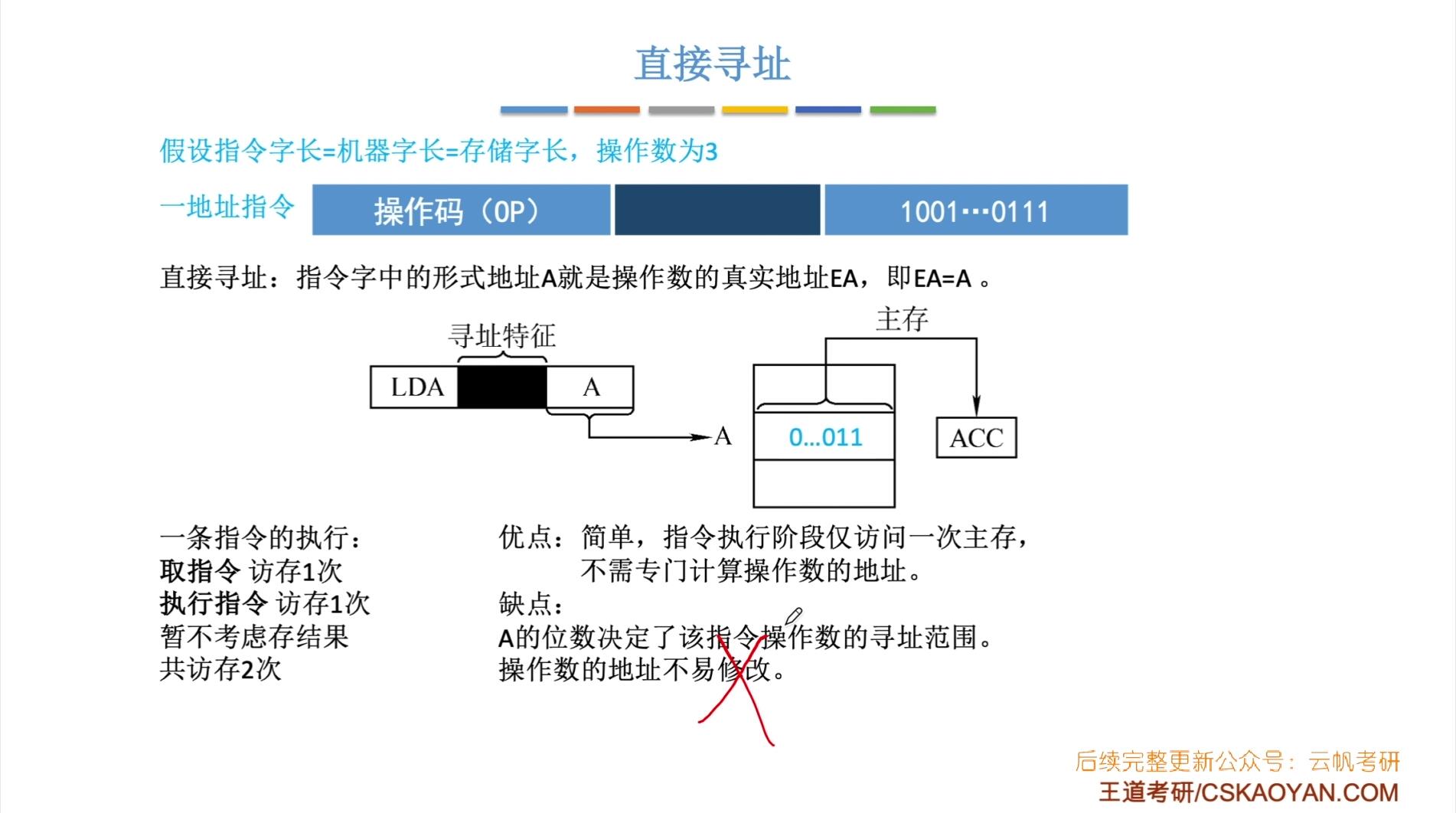

数据寻址

一地址指令

直接寻址

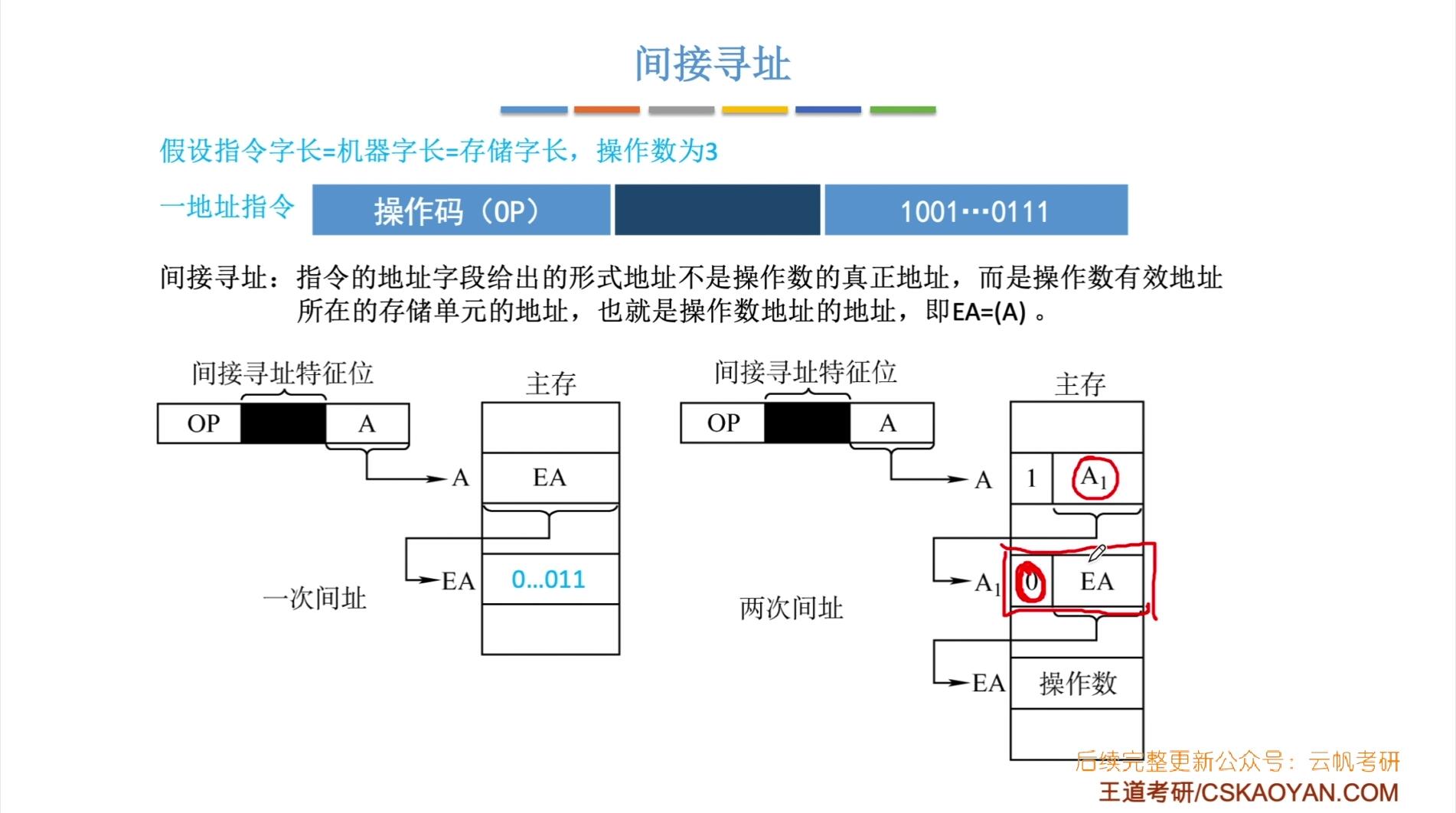

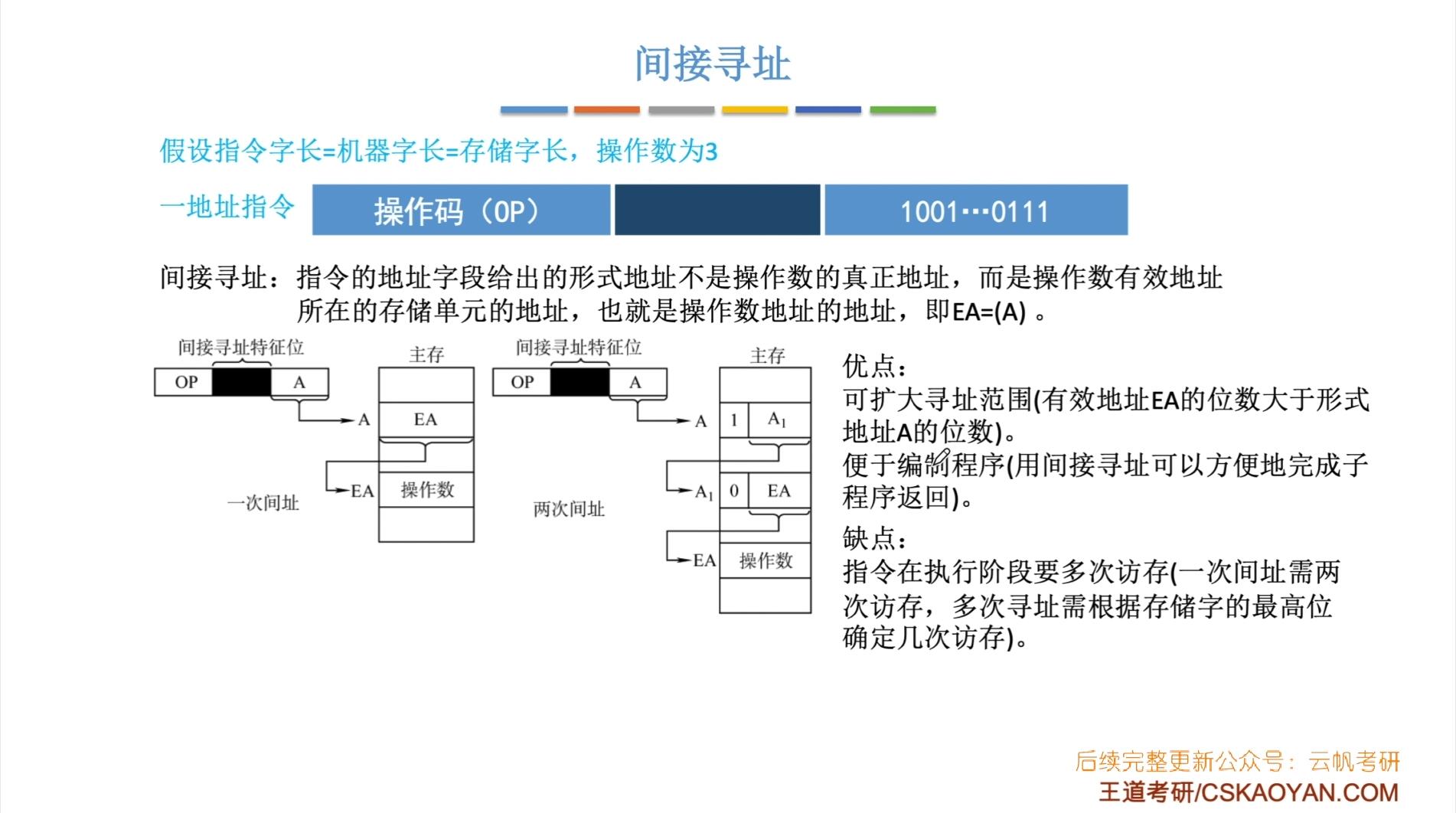

间接寻址

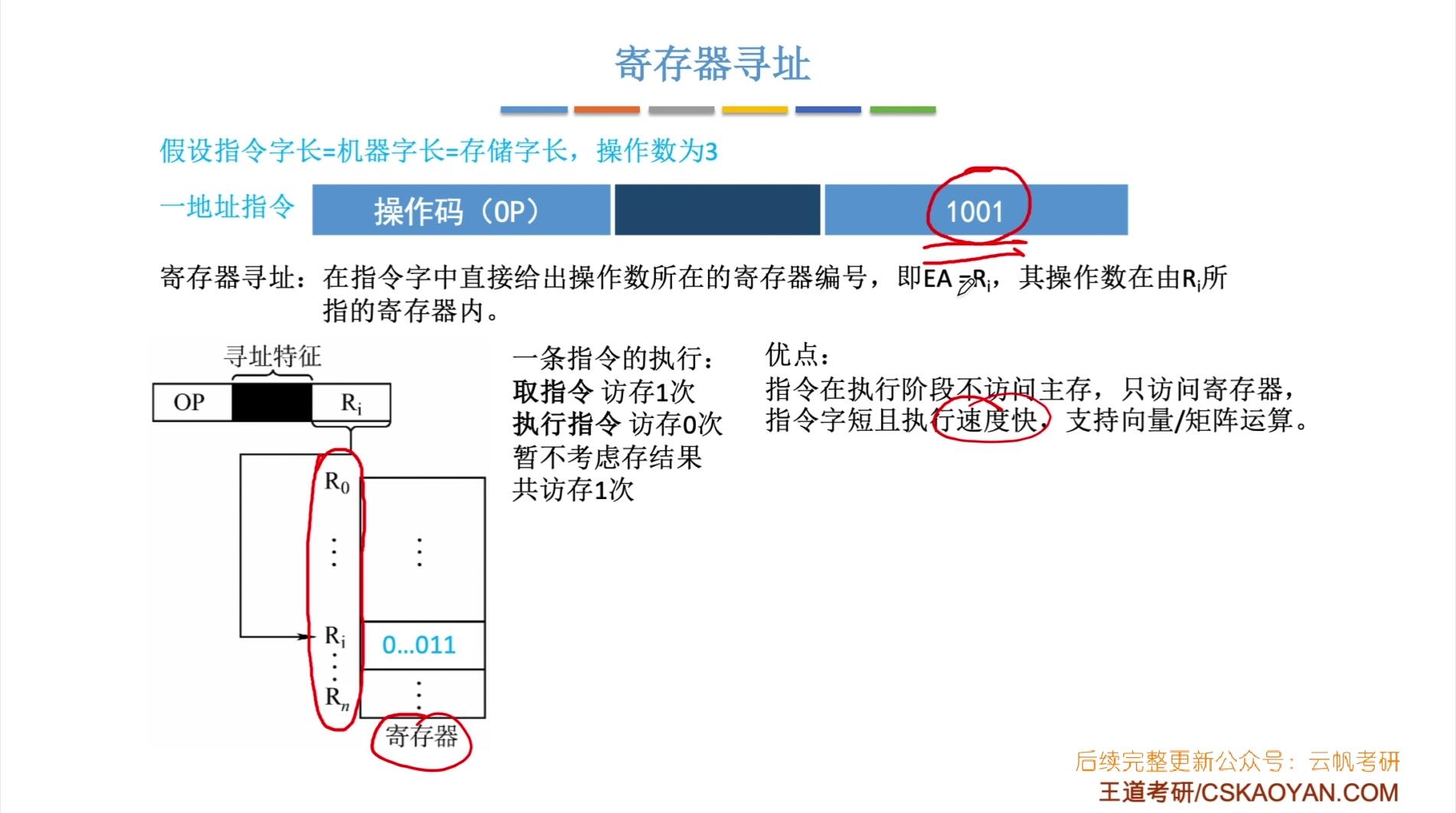

寄存器寻址

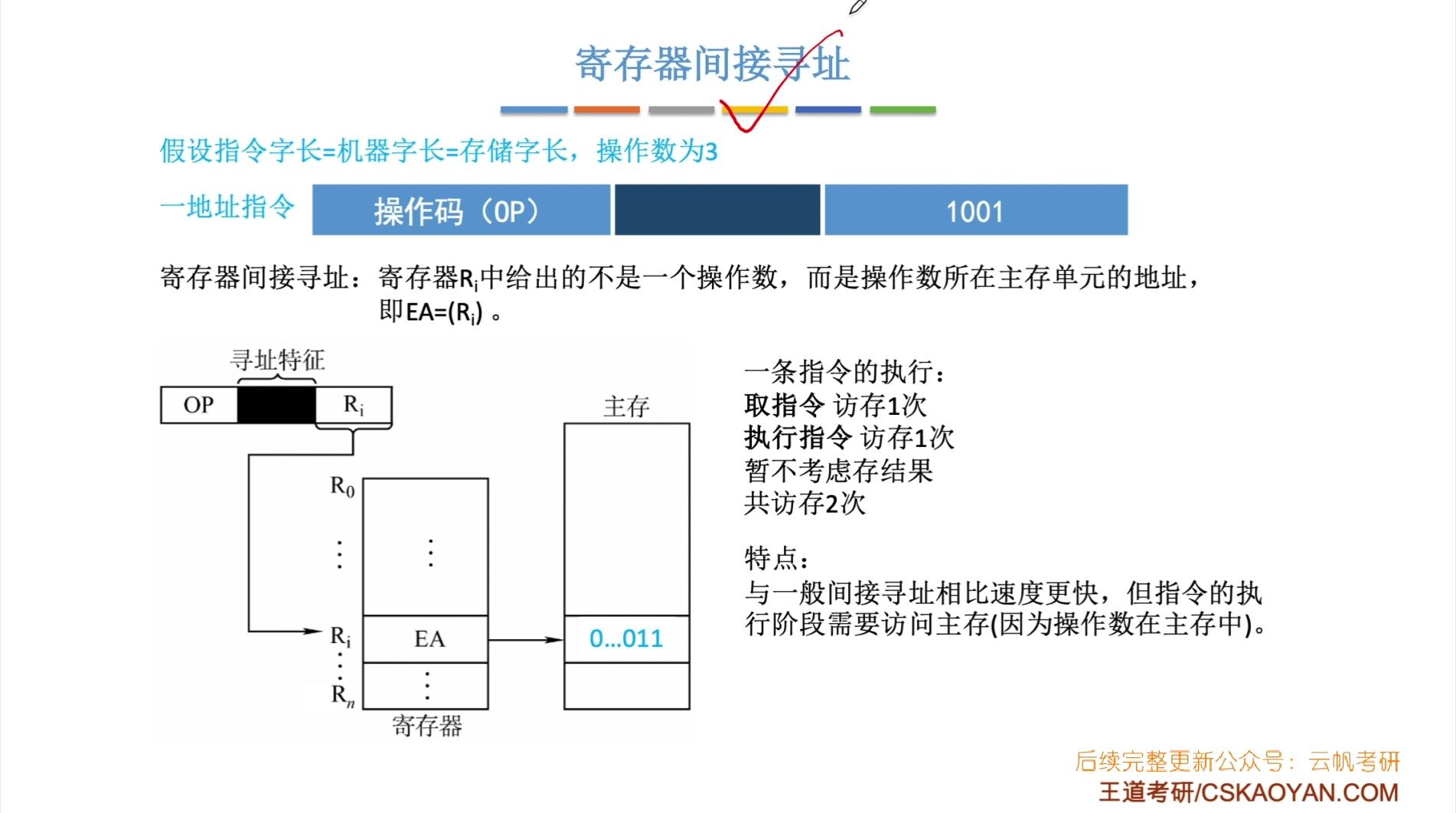

寄存器间接寻址

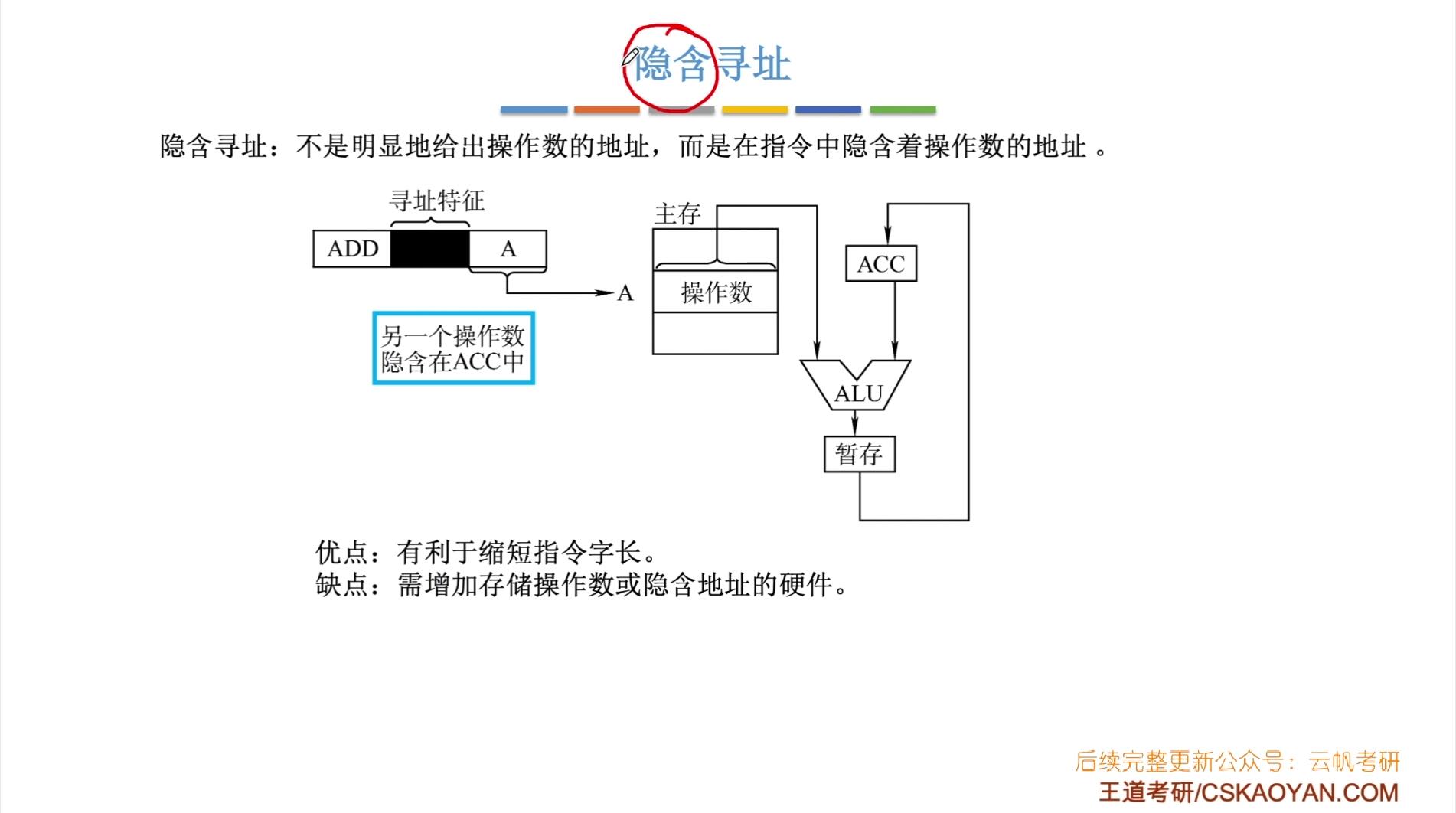

隐含寻址

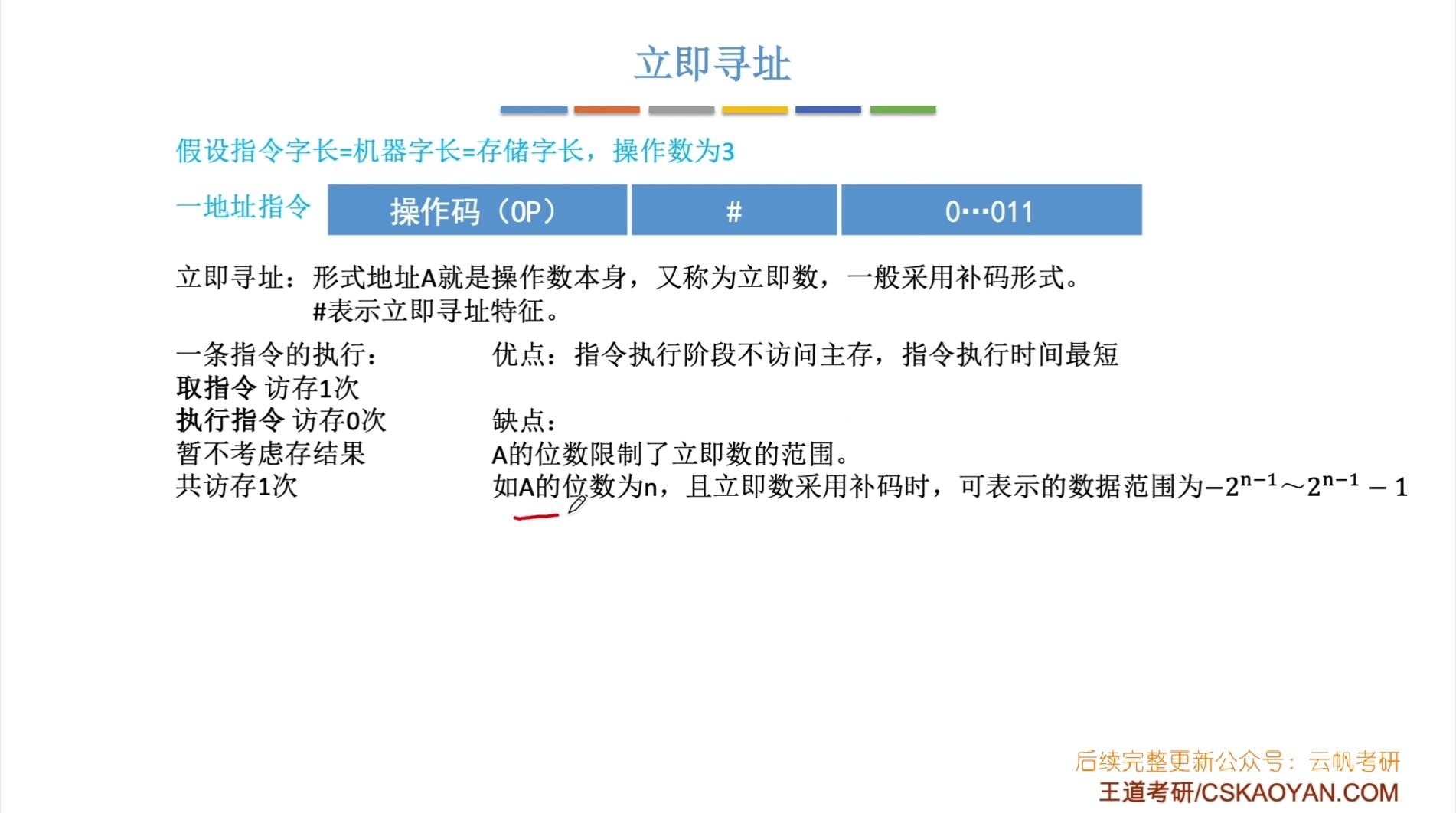

立即寻址

理解计算机系统组成原理 - 运用Java编程的工具rPeANUt